# Strahlenharter CAN Physical Layer in 65 nm CMOS Technologie für das Kontrollsystem des ATLAS Pixeldetektors

Masterthesis

Erstprüfer: Prof. Dr. Michael Karagounis

Zweitprüfer: Alexander Walsemann

Autor: Tobias Fröse

Abgabetermin: 30.10.19

# Kurzzusammenfassung

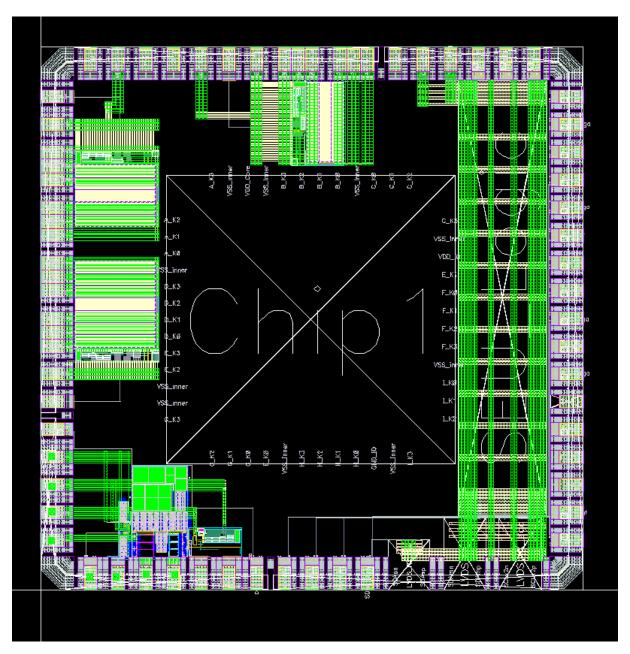

Die vorliegende Masterthesis beschreibt die Entwicklung eines Strahlenharten CAN Physical Layer in einer 65 nm CMOS Technologie für das Kontrollsystem des ATLAS Pixeldetektors. Dieser CAN Physical Layer ist Bestandteil des DCS Chips (Detector Control System), der im Rahmen des Upgrades des ATLAS Pixeldetektors zum High Luminosity Large Hadron Collider (HL-LHC) entwickelt wird. Die Aufgabe des DCS Chips ist die Steuerung und Überwachung der Sensorik des ATLAS Pixeldetektors. Die Transistoren der verwendeten Technologie dürfen mit maximal 1,2 Volt betrieben werden. Um dennoch die Kompatibilität zum CAN Standard beizubehalten ist es notwendig mit wesentlich höheren Spannungspegeln zu arbeiten. Im Verlauf dieser Masterthesis werden zu diesem Zweck ein CAN Treiber, ein Levelshifter und ein CAN Empfänger entworfen, die dazugehörigen Layouts erstellt und die Eigenschaften der Schaltungen auf dem ersten gefertigten Prototyp des DCS Chips vermessen.

# **Abstract**

This thesis describes the development of a radiation hard CAN physical layer in a 65 nm CMOS technology for the control system of the ATLAS pixel detector. This CAN physical layer is part of the Detector Control System (DCS) chip, which is being developed as part of the upgrade of the ATLAS pixel detector to the High Luminosity Large Hadron Collider (HL-LHC). The task of the DCS chip is the control and monitoring of the sensor technology in the ATLAS pixel detector. The transistors of the used technology shall be operated with a maximum voltage of 1.2 volts. Nevertheless, to maintain compatibility with the CAN standard, it is necessary to work with much higher voltage levels. In this thesis, a CAN driver, a level shifter and a CAN receiver are designed, the associated layouts are generated and the measurement of the first produced prototype of the DCS chip is carried out.

# Eidesstattliche Erklärung

| Hiermit versichere ich an Eides statt, dass die von mir vorgelegte Prüfungsleistu<br>ohne unzulässige fremde Hilfe erstellt worden ist. Alle verwendeten Quellen sir<br>aufgeführt, dass Art und Umfang der Verwendung nachvollziehbar sind | · ·          |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|

|                                                                                                                                                                                                                                             |              |  |  |

| Ort, Datum                                                                                                                                                                                                                                  | Unterschrift |  |  |

# Inhalt

| 1. | Einle  | eitung                                                       | 1   |

|----|--------|--------------------------------------------------------------|-----|

| 2. | CAN    | Treiber                                                      | 2   |

|    | 2.1.   | Beschreibung und Anforderungen                               | 2   |

|    | 2.2.   | Grundfunktion CAN Treiber                                    | 2   |

|    | 2.3.   | Strahlenharter CAN Treiber                                   | 3   |

|    | 2.4.   | Anforderungen an den CAN Treiber                             | 4   |

|    | 2.4.1. | Transistorkette                                              | 5   |

|    | 2.4.2. | Biasschaltung                                                | 8   |

|    | 2.5.   | Gesamtschaltung                                              | .10 |

| 3. | Leve   | elshifter                                                    | .11 |

|    | 3.1.   | Beschreibung und Anforderungen                               | .11 |

|    | 3.2.   | Grundmodell Levelshifter                                     | .11 |

|    | 3.3.   | Einstellung des Levelshifters                                | .14 |

|    | 3.4.   | Synchronisation der NMOS/PMOS Steuersignale des CAN Treibers | .16 |

|    | 3.5.   | Endergebnis und weitere Aufgaben                             | .19 |

| 4. | Simi   | ulationsergebnisse CAN Treiber und Levelshifter              | .20 |

|    | 4.1.   | Simulationsergebnisse                                        | .24 |

|    | 4.1.1. | Cornersimulation                                             | .24 |

|    | 4.1.2. | Transiente Signalanalyse                                     | .26 |

|    | 4.1.3. | Monte Carlo (Mismatch)                                       | .28 |

|    | 4.1.4. | Monte Carlo (Process)                                        | .30 |

| 5. | CAN    | Empfänger                                                    | .31 |

|    | 5.1.   | Beschreibung und Anforderungen                               | .31 |

|    | 5.2.   | Eingangsstufe                                                | .32 |

|    | 5.3.   | Komparator mit PMOS Eingangsstufe                            | .34 |

|    | 5.3.1. | Dominanter Zustand im Komparator mit PMOS Eingangsstufe      | .35 |

|    | 5.3.2. | Rezessiver Zustand im Komparator mit PMOS Eingangsstufe      | .36 |

|    | 5.3.3. | Arbeitsbereich Transistor M8                                 | .37 |

|    | 5.4.   | Komparator mit NMOS Eingangsstufe                            | .38 |

|    | 5.4.1. | Dominanter Zustand im Komparator mit NMOS Eingangsstufe      | .39 |

|    | 5.4.2. | Rezessiver Zustand im Komparator mit NMOS Eingangsstufe      | .40 |

|    | 5.4.3. | Arbeitsbereich Transistor M7                                 | .41 |

|    | 5.5.   | Endverstärkung                                               | .42 |

|    | 5.6.   | Simulationsergebnisse CAN Empfänger                          | .43 |

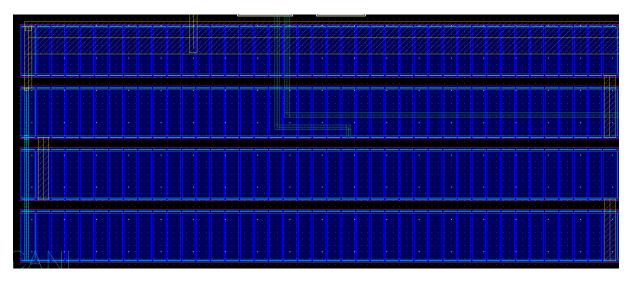

| 6. | Layo   | out44                                    |

|----|--------|------------------------------------------|

|    | 6.1.   | Allgemein                                |

|    | 6.1.1. | Erläuterung Schichten44                  |

|    | 6.1.2. | Bauteile47                               |

|    | 6.1.3. | Begriffe Layoutdesign54                  |

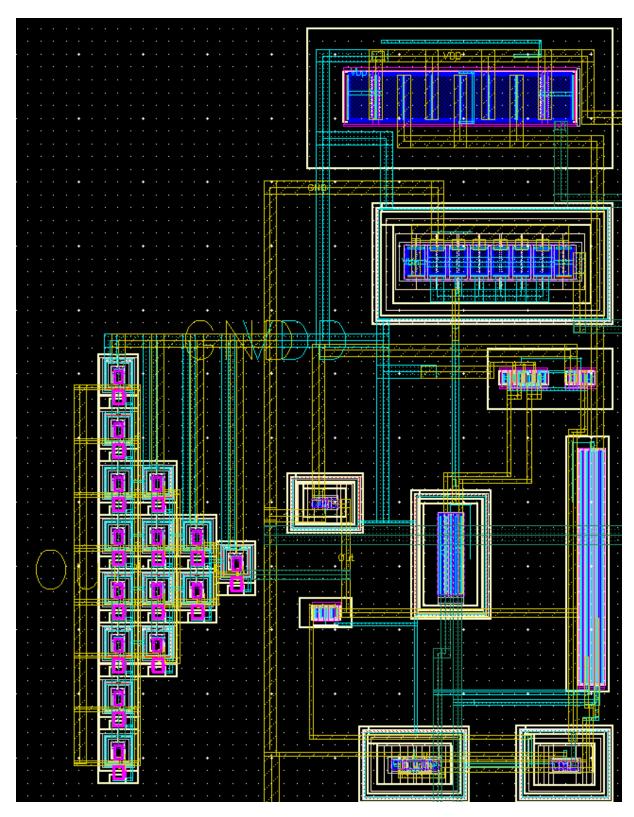

|    | 6.2.   | Layout des Levelshifters56               |

|    | 6.2.1. | Allgemein56                              |

|    | 6.2.2. | Position Kontakte56                      |

|    | 6.2.3. | Bauteilpositionierung57                  |

|    | 6.2.4. | Dimensionierung der Bauteile im Layout59 |

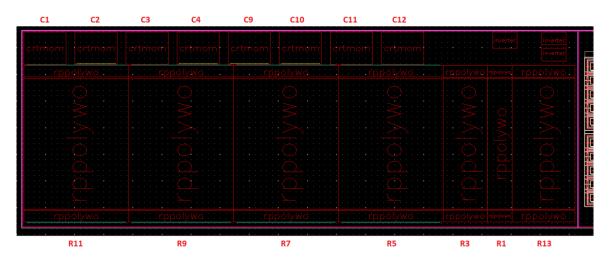

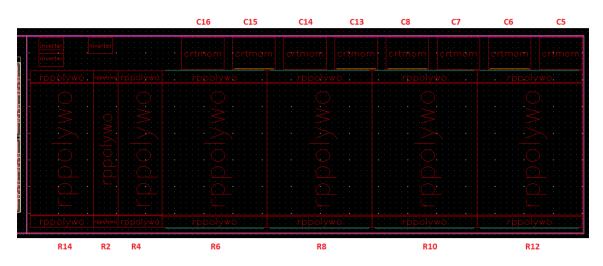

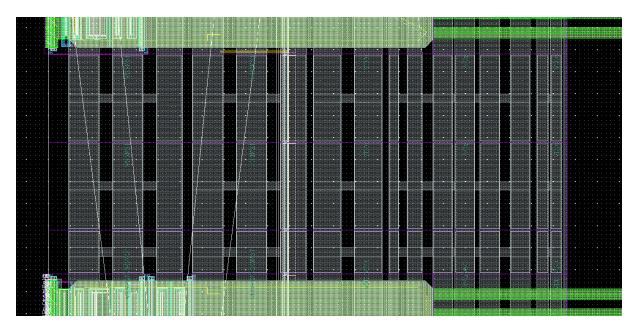

|    | 6.3.   | Layout des CAN Treibers60                |

|    | 6.3.1. | Floorplan des CAN Treibers60             |

|    | 6.3.2. | Position Kontakte61                      |

|    | 6.3.3. | Bauteilpositionierung62                  |

|    | 6.3.4. | Layout Dimensionierung der Bauteile63    |

|    | 6.4.   | Layout des CAN Empfängers65              |

|    | 6.4.1. | Floorplan des CAN Empfängers65           |

|    | 6.4.2. | Position der Kontakte66                  |

|    | 6.4.3. | Positionierung der Bauteile68            |

|    | 6.4.4. | Dimensionierung der Bauteile im Layout68 |

|    | 6.5.   | Floorplan69                              |

| 7. | Erge   | bnis nach Produktion72                   |

|    | 7.1.   | Messungen am CAN Treiber73               |

|    | 7.2.   | Messungen am CAN Empfänger74             |

| 8. | Zusa   | nmmenfassung75                           |

|    | 8.1.   | Ausblick76                               |

| 9. | Anh    | ang77                                    |

| 10 | ). Li  | teratur88                                |

# Abbildungsverzeichnis

| Abbildung 1: CAN Treiber (einfach)                                                             | 2     |

|------------------------------------------------------------------------------------------------|-------|

| Abbildung 2: Blockdiagramm CAN Treiber                                                         | 3     |

| Abbildung 3: Steuersignale PMOS (rot) und NMOS (blau)                                          | 4     |

| Abbildung 4: Ausgangssignal CAN Treiber                                                        | 5     |

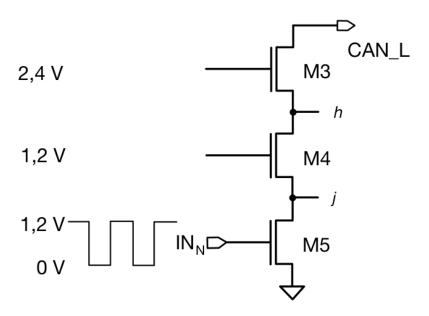

| Abbildung 5: Transistorkette NMOS Teil                                                         | 5     |

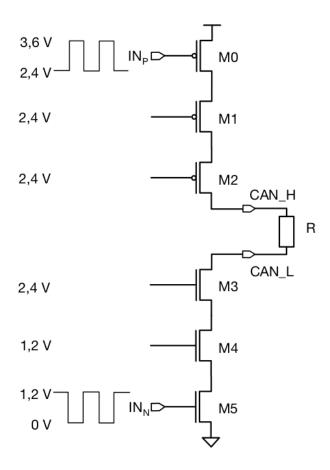

| Abbildung 6: Transistorketten PMOS und NMOS Teil                                               | 7     |

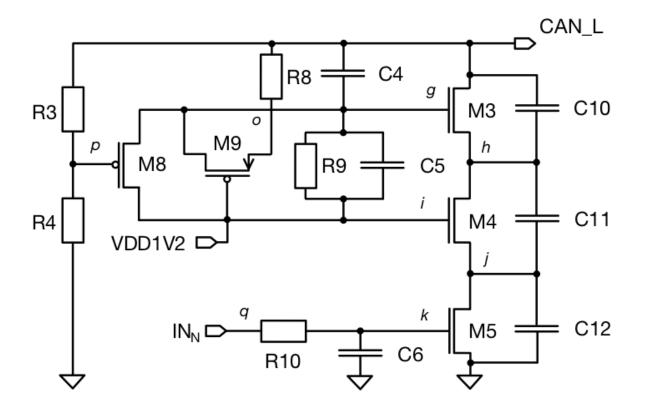

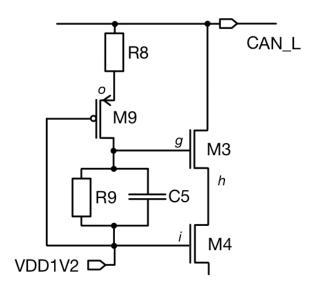

| Abbildung 7: NMOS CAN Treiber                                                                  | 8     |

| Abbildung 8: Spannungsteiler R8/R9                                                             |       |

| Abbildung 9: Gesamtschaltung CAN Treiber                                                       |       |

| Abbildung 10: Einfacher Inverter                                                               | 11    |

| Abbildung 11: Grundmodell Levelshifter                                                         | 12    |

| Abbildung 12: Ausgangspegel Levelshifter                                                       | 13    |

| Abbildung 13: Schaltbild Transistoreinstellung VDD3V6                                          | 14    |

| Abbildung 14: Oberes Ausgangssignal und Eingangssignal                                         |       |

| Abbildung 15: Schaltbild Transistoreinstellung VDD1V2                                          |       |

| Abbildung 16: Steuersignale NMOS (unten) und PMOS (oben)                                       | 18    |

| Abbildung 17: Blockschaltbild gesamt                                                           | 20    |

| Abbildung 18: Flanken vor und nach Verzögerungskette. Alle Corner. Steigende Flanke PMOS vor   | (rot) |

| nach (gelb). Fallende Flanke NMOS vor (blau) nach (grün)                                       | 21    |

| Abbildung 19: Flanken vor und nach Verzögerungskette. Alle Corner. Fallende Flanke PMOS vor (r | ot)   |

| nach (gelb). Steigende Flanke NMOS vor (blau) nach (grün).                                     | 22    |

| Abbildung 20: Verzögerungskette. Oben: Verzögerung PMOS Steuersignal. Mitte: Flakensteilheit   |       |

| PMOS. Unten: Flankensteilheit NMOS                                                             | 23    |

| Abbildung 21: Output Setup Cornersimulation                                                    | 24    |

| Abbildung 22: Cornersimulation Vbus = 2V                                                       | 25    |

| Abbildung 23: Cornersimulation Vbus = 3V                                                       | 25    |

| Abbildung 24: CAN_H, CAN_L, V_Diff                                                             | 26    |

| Abbildung 25: Monte Carlo (Mismatch)                                                           | 28    |

| Abbildung 26: Output Setup für Transistor MO                                                   | 29    |

| Abbildung 27: Monte Carlo (Process)                                                            | 30    |

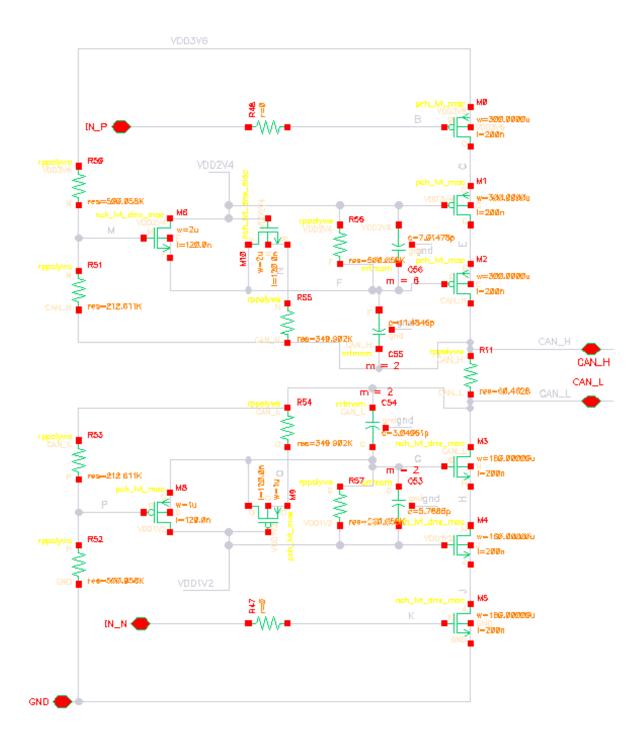

| Abbildung 28: Gesamtschaltung CAN Empfänger                                                    | 31    |

| Abbildung 29: Eingangssignale und Potentiale a und b                                           | 33    |

| Abbildung 30: Entscheidungsnetzwerk mit PMOS Eingangsstufe                                     | 34    |

| Abbildung 31: Entscheidungsnetzwerk mit PMOS Eingangsstufe. Arbeitspunkt im dominanten         |       |

| Zustand                                                                                        | 35    |

| Abbildung 32: Entscheidungsnetzwerk mit PMOS Eingangsstufe. Arbeitspunkt im rezessiven Zusta   | and   |

|                                                                                                |       |

| Abbildung 33: Entscheidungsnetzwerk mit NMOS Eingangsstufe                                     | 38    |

| Abbildung 34: Entscheidungsnetzwerk mit NMOS Eingangsstufe. Arbeitspunkt im dominanten         |       |

| Zustand                                                                                        | 39    |

| Abbildung 35: Entscheidungsnetzwerk mit NMOS Eingangsstufe. Arbeitspunkt im rezessiven Zusta   |       |

|                                                                                                |       |

| Abbildung 36: Verstärker oberer und unterer Schaltungsteil                                     |       |

| Abbildung 37: CAN Empfänger Ein- und Ausgangssignal                                            |       |

| Abbildung 38: Wannenstruktur aus NW (grün) und DNW (blau)                                      |       |

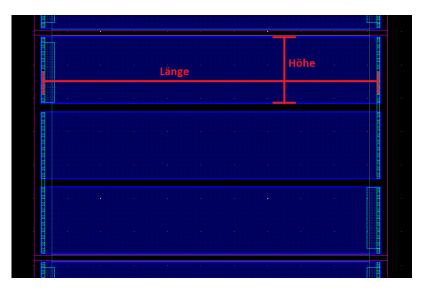

| Abbildung 39: Layout Widerstand (RPDMY und RH ausgeblendet)                                    |       |

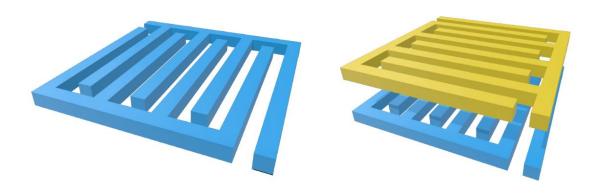

| Abbildung 40: MOM Kanazität Links: Motallohana 1, Pachts Motallohana 1 und 2, Ohna VIAs        | 10    |

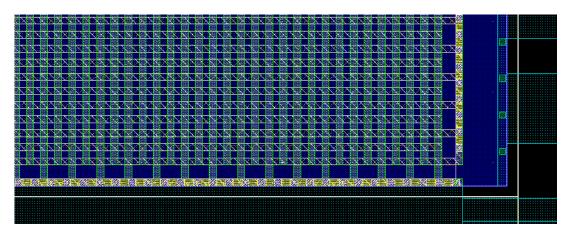

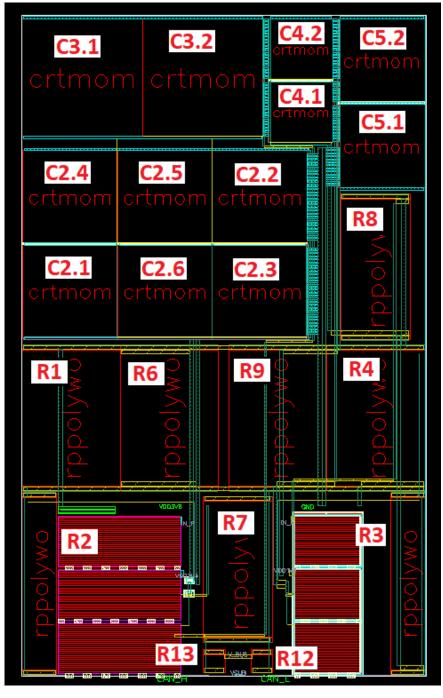

| Abbildung 41: Ausschnitt eines Kondensators im Layout                                    | 48       |

|------------------------------------------------------------------------------------------|----------|

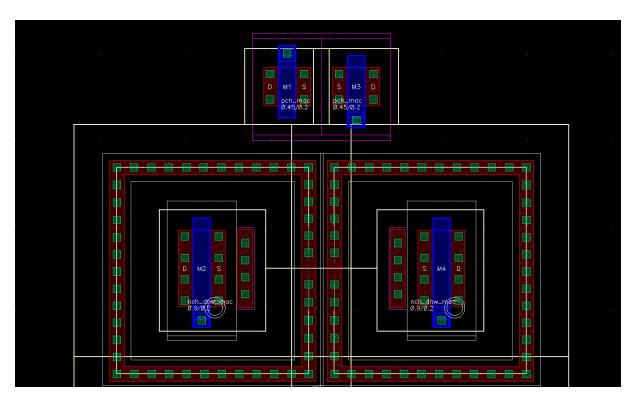

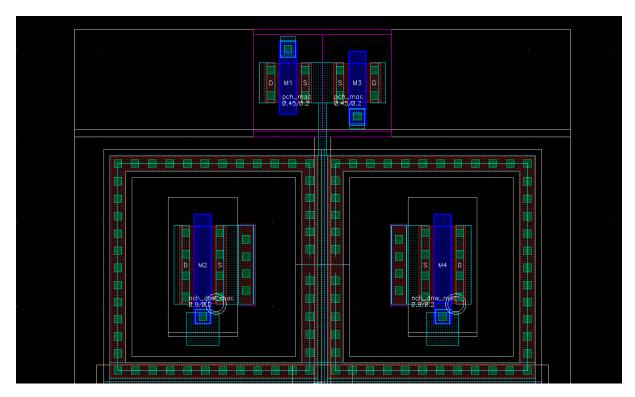

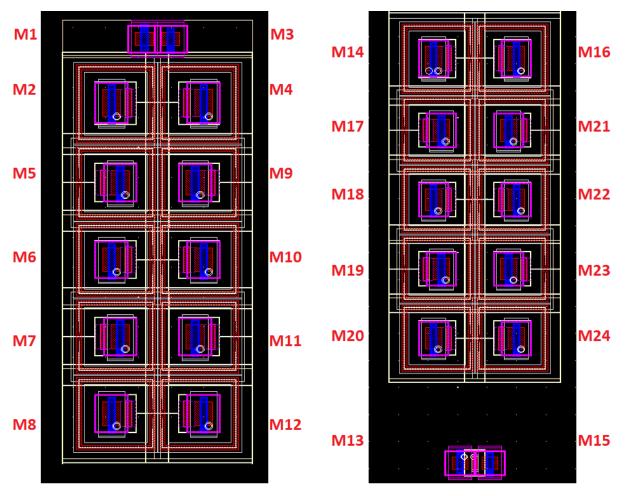

| Abbildung 42: Layout PMOS und NMOS Transistoren M1 bis M4 des Levelshifters              | 49       |

| Abbildung 43: Layout NMOS und PMOS Transistoren Levelshifter. Metallisierung unterster E | bene und |

| DNW                                                                                      | 50       |

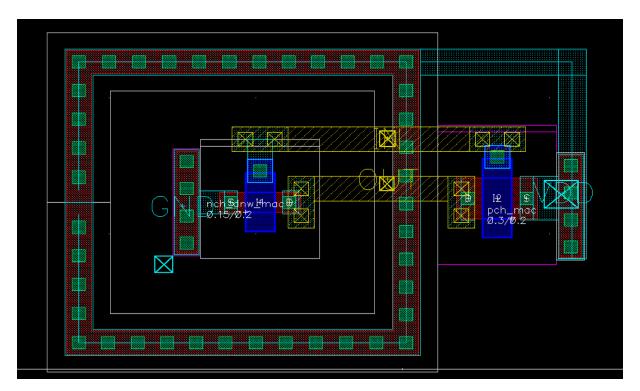

| Abbildung 44: Layout Inverterschaltung                                                   | 51       |

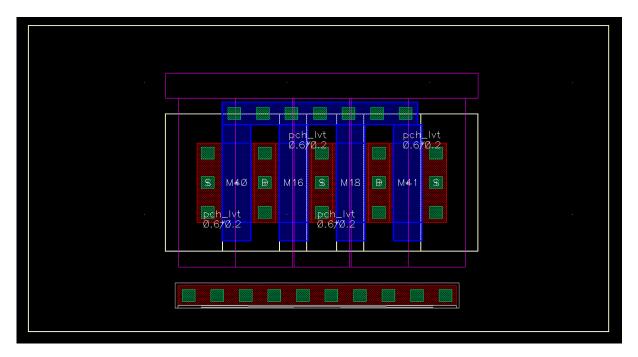

| Abbildung 45: Layout PMOS Transistoren mit Dummy                                         | 52       |

| Abbildung 46: Layout Widerstand mit Dummy                                                | 53       |

| Abbildung 47: Layout Levelshifter Bauteilpositionierung                                  | 56       |

| Abbildung 48: Layout Levelshifter IO                                                     | 56       |

| Abbildung 49: Layout Levelshifter links Bauteile                                         | 57       |

| Abbildung 50: Layout Levelshifter rechts Bauteile                                        | 57       |

| Abbildung 51: Layout Levelshifter Transistoren in der Mitte                              | 58       |

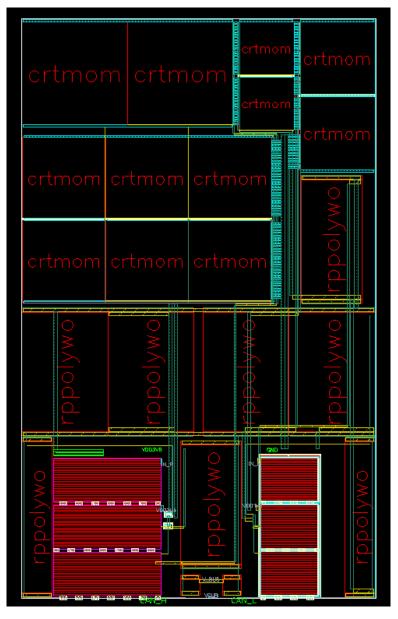

| Abbildung 52: Layout CAN Treiber Bauteilpositionierung                                   | 60       |

| Abbildung 53: Layout CAN Treiber IO                                                      | 61       |

| Abbildung 54: Layout CAN Treiber Kapazitäten und Widerstände                             | 62       |

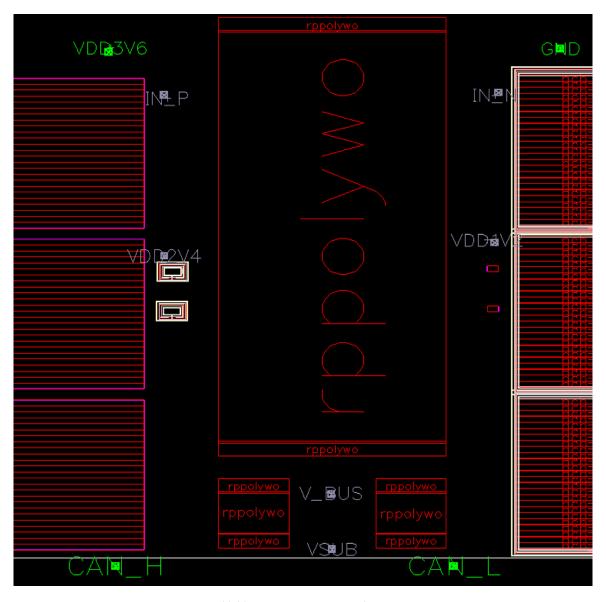

| Abbildung 55: Layout CAN Empfänger                                                       | 65       |

| Abbildung 56: Schaltbild CAN Empfänger                                                   | 65       |

| Abbildung 57: Spannungsteilung CAN_L im CAN Empfänger                                    | 66       |

| Abbildung 58: Transistoren und Inverterstufen im CAN Empfänger                           | 67       |

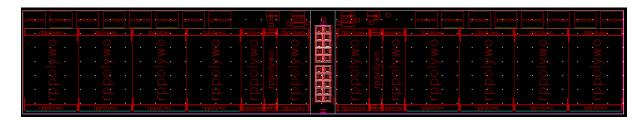

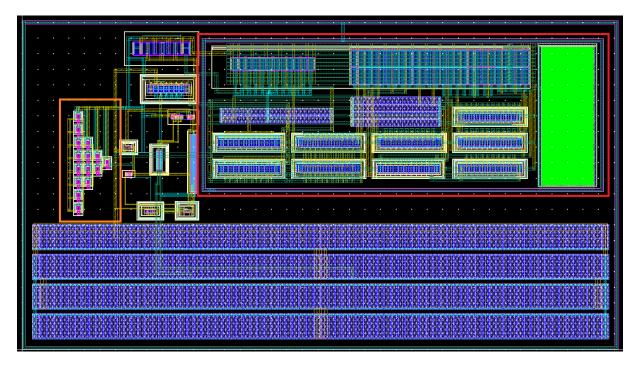

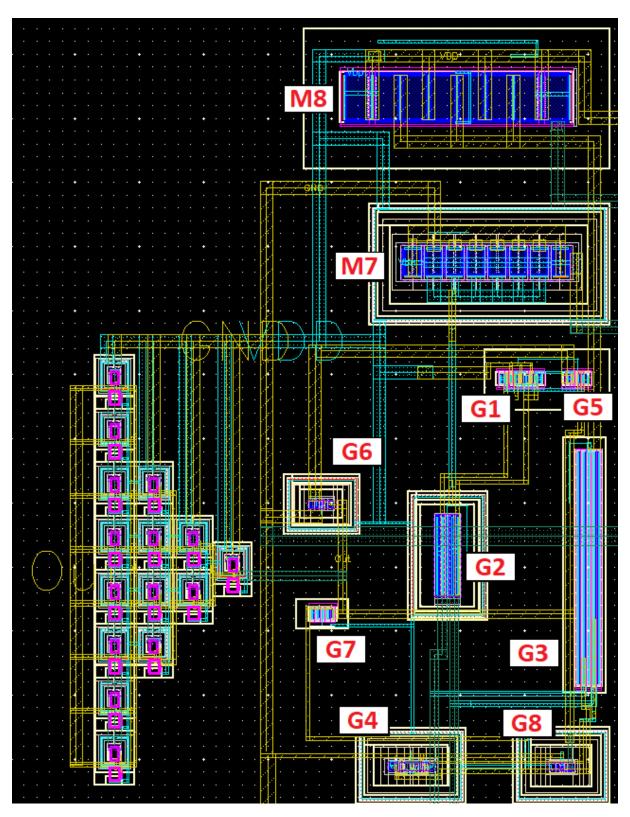

| Abbildung 59: Floorplan Gesamtansicht                                                    | 69       |

| Abbildung 60: Padring: Ringstruktur und Pad für Bonding                                  |          |

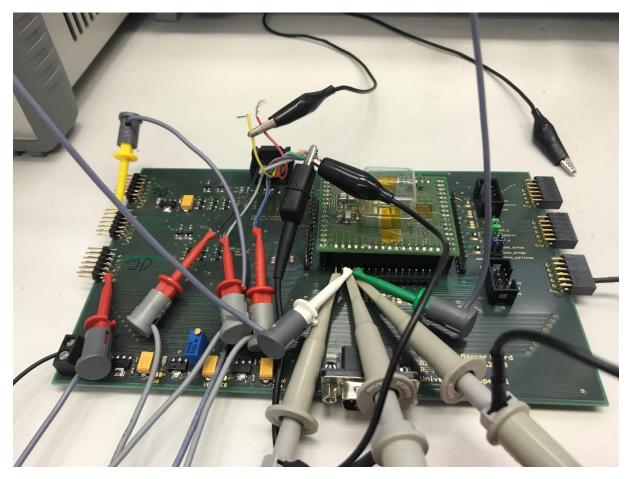

| Abbildung 61: Messaufbau DCS Prototyp                                                    | 72       |

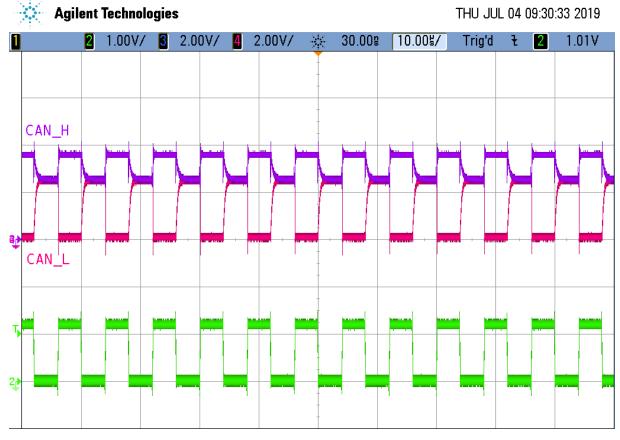

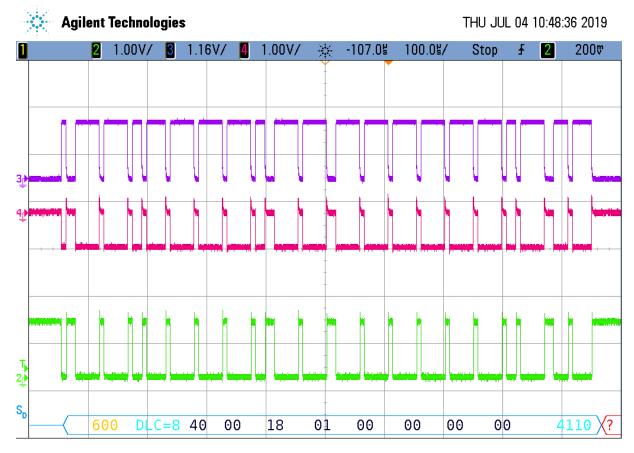

| Abbildung 62: Messergebnis CAN Treiber. Lila: CAN_H. Rot: CAN_L. Grün: IN                | 73       |

| Abbildung 63: Messergebnis CAN Empfänger. Lila: CAN_H. Rot: CAN_L, Grün: OUT             | 74       |

# 1. Einleitung

Das ATLAS Projekt ist einer der beiden großen Experimente des Large Hadron Collider (LHC) am europäischen Forschungszentrum CERN. Mit diesem Detektor werden Kollisionen zwischen Teilchen beobachtet, Theorien der Teilchenphysik überprüft und nach neuen Teilchen jenseits des aktuellen Wissensstandes gesucht. Ein großer Meilenstein des ATLAS Experiments ist der Nachweis des Higgs-Boson.

Ein wichtiger Bestandteil des ATLAS Experiments ist der Pixel Detektor. Um die Kollisionshäufigkeit zu steigern und die Genauigkeit der Analyse zu verbessern wird der Large Hadron Collider zum High Luminositiy LHC ausgebaut. Für dieses Ziel werden deutlich mehr Pixelsensoren verbaut. Die Stromversorgung über Zuleitungen für die Pixelsensoren wird dabei zu einem kritischen Thema. Es ist nicht mehr möglich die erhöhte Anzahl an Pixelsensoren parallel zu verschalten. Stattdessen wird eine serielle Stromversorgung eingeführt. Diese Umstellung senkt erheblich den Strombedarf und die Materialkosten, die in Versorgungsleitungen investiert werden müssten. Allerdings erzeugt diese Umstellung auch die Problematik, dass ein einzelnes beschädigtes Pixelmodul zum Ausfall aller in einer seriellen Versorgungskette verschalteten Pixelmodule führen wird. Um diesem Problem beizukommen, wird in einer Zusammenarbeit der Fachhochschule Dortmund mit der Bergischen Universität Wuppertal ein neues Detektor-Kontroll-System (DCS) entwickelt. Dieses Detektor-Kontroll-System soll es ermöglichen, vitale Daten der seriell verschalteten Pixelmodule zu überwachen und bei Bedarf einzelne Module zu überbrücken, um diese vor Überlastung zu schützen oder bei Beschädigung den Stromfluss in der Versorgungskette aufrecht zu erhalten.

Für die Kommunikation zwischen dem DCS Chip im Pixeldetektor und dem DCS Computer in der Leitwarte greift das DCS System auf den aus der Automobilindustrie bekannten CAN Standard [4] zurück. Hauptbestandteil dieser Masterthesis ist die Entwicklung des CAN Physical Layers, der für diese Kommunikationsstrecke benötigt wird. Das Kernproblem dieser Aufgabe wird durch die geforderte Strahlenhärte hervorgerufen. Da der DCS Chip nahe an den zu überwachenden Pixelsensoren betrieben wird, ist er der vollen Strahlungsdosis des Experiments ausgesetzt. Um trotz der Strahlung den sicheren Betrieb der Schaltung über die komplette Lebensdauer zu gewährleisten, sollen alle Transistoren mit dünnem Gate-Oxid in der gewählten 65 nm Technologie von TSMC verwendet werden. Außerdem darf nicht mit minimalen Transistorlängen und -breiten gearbeitet werden. Dadurch wird eine Verschiebung der Schwellenspannung mit zunehmender Strahlungsdosis vermieden. Durch diese dünnen Gateoxide ist die Spannung, die an den Transistoren anliegt, auf 1,2 V begrenzt. Um dem CAN Standard einzuhalten ist es allerdings nötig mit erheblich höheren Spannungen zu arbeiten.

Die Zielsetzung dieser Masterthesis ist die Entwicklung eines strahlenharten CAN Treibers und eines CAN Empfängers, die mit hohen Versorgungsspannungen von bis zu 3,6 V zuverlässig arbeiten, um die vom CAN Standard vorgegebenen Richtwerte einzuhalten. Im Verlauf dieser Masterthesis werden die benötigten Schaltungen entwickelt und simuliert. Es wird ein Layout für jede Schaltung erzeugt und anschließend eine Messung am ersten Prototyp mit einer gefertigten Testumgebung durchgeführt.

## 2. CAN Treiber

#### 2.1. Beschreibung und Anforderungen

Gegenstand dieses Kapitels ist die Entwicklung des benötigten strahlenharten CAN Treibers.

Eine besondere Herausforderung des Projekts besteht darin, die Treiberschaltung so aufzubauen, dass trotz der Versorgungsspannung von 3,6V sichergestellt wird, dass unter allen Simulationsbedingungen die maximale erlaubte Spannung nicht überschritten wird. Der sichere Betrieb der Schaltung muss sowohl bei Raumtemperatur als auch bei der Betriebstemperatur von -20°C gewährleistet sein. Auch Prozessvariationen dürfen nicht zu einer Überschreitung der Spannungsgrenzen führen.

#### 2.2. Grundfunktion CAN Treiber

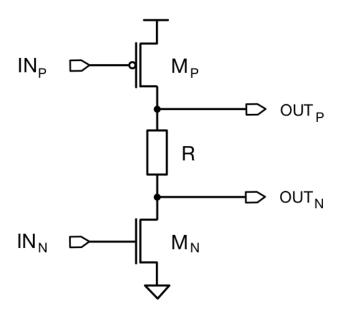

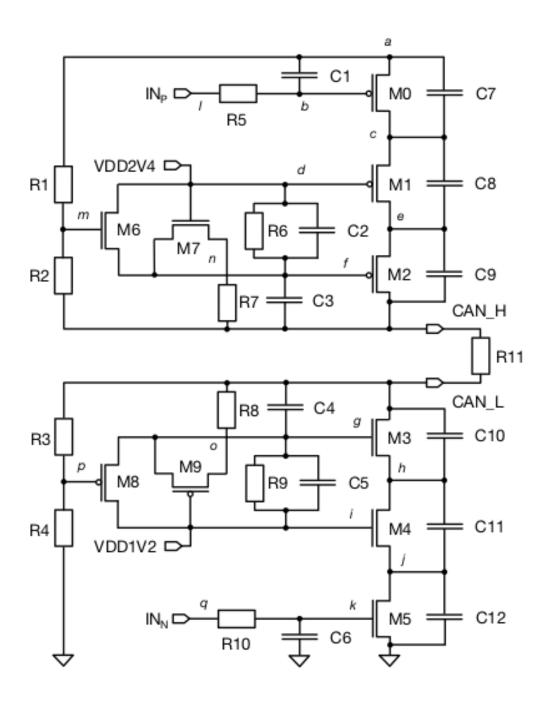

Abbildung 1 zeigt eine einfache Umsetzung, die zur Erzeugung eines CAN Signals verwendet werden kann.

Abbildung 1: CAN Treiber (einfach)

Um mit dieser Schaltung ein CAN Standard konformes Signal zu erzeugen, werden zwei Zustände benötigt.

Im ersten Zustand werden die Gatepotentiale beider Transistoren so angesteuert, dass die Transistoren schließen. IN<sub>P</sub> wird kleiner als die obere Spannungsversorgung während IN<sub>N</sub> ein Potential oberhalb der Masse annimmt. Der resultierende Stromfluss erzeugt am Widerstand R einen Spannungsabfall. Die differentielle Spannung zwischen OUT<sub>P</sub> und OUT<sub>N</sub> erhöht sich. Die differentielle Spannung hängt proportional mit dem Stromfluss durch die Transistoren zusammen und wird nur von den Drain-Source Spannungen der Transistoren begrenzt, die wiederum vom Kanalwiderstand der Transistoren im geschlossenen Zustand bestimmt wird. Eine hohe differentielle Spannung stellt im CAN Standard die logische 0 dar und wird dominanter Zustand genannt.

Für den zweiten Zustand werden beide Transistoren geöffnet. IN<sub>N</sub> nimmt das Massepotential an während IN<sub>P</sub> auf die obere Spannungsversorgung gelegt wird. Der Stromfluss geht gegen 0 A und damit ist auch die differentielle Spannung 0 V. Das Potential an OUT<sub>P</sub> und OUT<sub>N</sub> wird von außen eingestellt und liegt im CAN Standard zwischen 2 V und 3 V. Eine differentielle Spannung unter 50 mV wird im CAN Standard als rezessiver Zustand betrachtet.

#### 2.3. Strahlenharter CAN Treiber

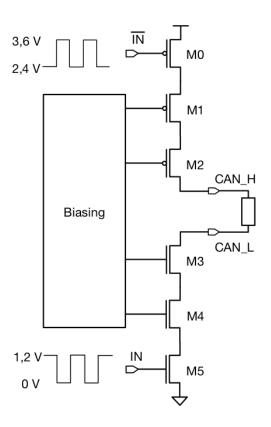

Abbildung 2 zeigt ein Blockdiagramm des CAN Treibers, mit den nötigen Veränderungen für die strahlungsharte Ausführung durch kaskodierte Dünngateoxid-Transistoren. Die Steuersignale für PMOS und NMOS Teil werden von einem Levelshifter erzeugt, der eigens für diesen CAN Treiber entwickelt wurde und in Kapitel 3 vorgestellt wird. Zur Erzeugung des CAN Ausgangssignals werden zwei Zustände benötigt. Im dominanten Zustand wird die logische 0 übertragen. Die Transistorkette wird leitend und der Stromfluss erzeugt einen Spannungsabfall über den Terminierungswiderstand. Im rezessiven Zustand wird die logische 1 übertragen. Hier ist die Transistorkette geöffnet. Das Potential wird von außen an CAN\_H und CAN\_L eingestellt.

Abbildung 2: Blockdiagramm CAN Treiber

#### 2.4. Anforderungen an den CAN Treiber

Dieses Kapitel befasst sich mit den grundlegenden Schaltungselementen, die zur Erzeugung des CAN Treibers verwendet werden. Außerdem werden Anforderungen an den CAN Treiber vermittelt und die Signale an Ein- und Ausgang erläutert.

Der CAN Treiber soll ein Signal mit einer Bitrate von 150 kbit/s erzeugen. Alle Simulationen werden mit einer Frequenz von 75 kHz und einer alternierenden Bitfolge (Rechtecksignal) durchgeführt. Im rezessiven Zustand wird der Bus mit einer Biasspannung von 2,5 V eingestellt. Um ein CAN Standard konformes Signal zu erzeugen, muss das Ausgangssignal über folgende Charakteristiken verfügen.

#### Dominanter Zustand:

- Potential CAN H zwischen 2,75 V und 4,5 V

- Potential CAN\_L zwischen 0,5 V und 2,25 V

- Differentielle Spannung zwischen CAN\_H und CAN\_L im Bereich von 1,5 V bis 3 V

#### Rezessiver Zustand (Biasspannung aktiv):

- Potential CAN\_H und CAN\_L zwischen 2 V und 3 V

- Differentielle Spannung zwischen CAN\_H und CAN\_L im Bereich von -0,5 V bis 50 mV

#### Rezessiver Zustand (Biasspannung inaktiv):

- Potential CAN\_H und CAN\_L zwischen -0,1 V und 0,1 V

- Differentielle Spannung zwischen CAN\_H und CAN\_L im Bereich von -0,2 V bis 0,2 V

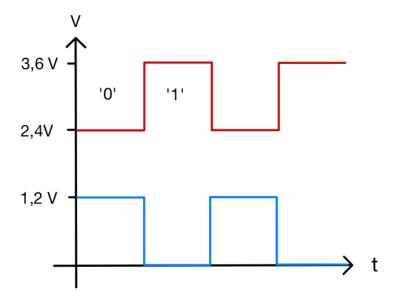

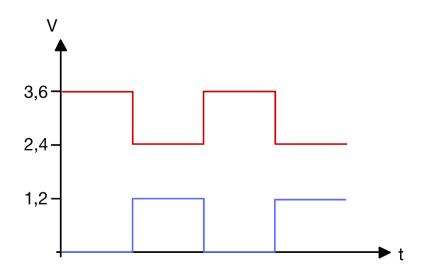

Es werden zwei Steuersignale benötigt. Diese Steuersignale werden von einem Levelshifter und einer nachgeschalteten Verzögerungsschaltung bereitgestellt. In Abbildung 3 werden die erzeugten Steuersignale für den PMOS sowie für den NMOS Teil des CAN Treiber dargestellt.

Abbildung 3: Steuersignale PMOS (rot) und NMOS (blau)

Wenn das Steuersignal für den PMOS Teil der Schaltung (rot) 2,4 V beträgt und das Steuersignal für den NMOS Teil der Schaltung (blau) 1,2 V beträgt, befindet sich der CAN Treiber im dominanten Zustand. Der rezessive Zustand stellt sich ein, wenn am Gate des PMOS 3,6 V und am Gate des NMOS 0 V anliegen. Abbildung 4 zeigt die benötigten Ausgangssignale des CAN Treibers.

Abbildung 4: Ausgangssignal CAN Treiber

#### 2.4.1. Transistorkette

Da die obere Spannungsversorgung bei 3,6 V liegt und die Technologie der Transistoren eine maximale Spannung von 1,2 V zwischen den Anschlüssen Gate, Source, Drain und Bulk erlaubt, ist es erforderlich, die Schaltung aus Abbildung 1 zu erweitern.

Abbildung 5: Transistorkette NMOS Teil

Abbildung 5 zeigt die Transistorkette, die für den NMOS Teil des CAN Treibers eingesetzt wird.

#### Rezessiver Zustand

Im rezessiven Zustand wird das Potential an CAN\_L über eine externe Busspannung eingestellt. Diese Spannung hat ein Potential von V<sub>Bias</sub> = 2,5 V. Selbst bei gleichmäßiger Spannungsteilung erfordern die Technologiegrenzen bei einer Gesamtspannung von 2,5 V eine Aufteilung auf mindestens drei Transistoren. Damit kann die Transistorkette mit einer Gesamtspannung von bis zu 3,6 V betrieben werden. Außerdem ist die Transistorkette durch die Verwendung eines dritten Transistors gegen folgende Probleme abgesichert:

- Spannungserhöhung auf dem Bus durch unterschiedliche Massepotentiale der Biasspannung im rezessiven Zustand.

- Spannungsspitzen durch Asynchronität der Steuersignale IN<sub>N</sub>, und IN<sub>P</sub> auf den Gate-Sourcesowie auf den Drain-Source Strecken der Transistoren.

- Spannungsspitzen durch Umladevorgänge der Kapazitäten zwischen Gate-Source- und Drain-Source an den Transistoren.

Im rezessiven Zustand liegt am Gate von Transistor M5 eine Spannung von 0 V an. Transistor M5 ist somit geöffnet.

Da das Gatepotential an Transistor M4 auf 1,2 V eingestellt ist, kann das Potential *j* in diesem Zustand ebenfalls auf maximal 1,2 V geladen werden. Sobald das Potential *j* 1,2 V erreicht, wird die Gate-Source Spannung an Transistor M4 klein und der Transistor öffnet. Die hinzugefügte Ladung auf diesem Punkt kann durch den geöffneten Transistor M5 nicht abgeführt werden.

Transistor M3 und das Potential h verhalten sich entsprechend. Mit steigendem Potential h sinkt die Gate-Source Spannung an Transistor M3 und der Transistor öffnet. Das Sourcepotential dieses Transistors kann die angelegte Gatespannung von 2,4 V nicht übersteigen. Die hinzugefügte Ladung auf dem Potentialpunkt h kann durch den bereits geöffneten Transistor M4 nicht mehr abgeführt werden.

Abbildung 6 zeigt die Erweiterung um die Transistorkette für den PMOS Teil der Schaltung. Die Transistorkette im NMOS Teil besteht aus drei Transistoren, um mit der Biasspannung von 2,5 V arbeiten zu können. Zwischen dieser Biasspannung und der maximalen Betriebsspannung von 3,6 V verbleibt noch eine Differenz von 1,1 V für den PMOS Teil der Schaltung. Diese Differenz wäre klein genug, um den PMOS Teil der Schaltung als einzelnen Transistor umzusetzen. Um eine höhere Synchronität im Schaltverhalten zwischen den beiden Schaltungsteilen zu erhalten, wird der PMOS Teil der Schaltung ebenfalls mit drei Transistoren umgesetzt.

Im rezessiven Zustand liegt am Gate von Transistor M0 eine Spannung von 3,6 V an. Die Gate-Source Spannung ist minimal und der Transistor M0 ist geöffnet.

Das Gatepotential von Transistor M1 ist auf 2,4 V eingestellt. Das Potential c liegt im Umschaltmoment eine Drain-Source Spannung unterhalb von 3,6 V. Da Transistor M0 geöffnet ist, kann dem Potential c keine weitere Ladung hinzugefügt werden. Über den geschlossenen Transistor M1 wird die Ladung am Potentialpunkt c solange abgeführt, bis die Gate-Source Spannung an Transistor M1 minimal wird und den Transistor öffnet. Das Potential c kann somit die angelegte Gatespannung von Transistor M1 nicht unterschreiten. Das Potential c wird durch die angelegte Gatespannung von 2,4 V an Transistor M2 begrenzt.

#### **Dominanter Zustand**

Befindet sich die Schaltung im dominanten Zustand, geht das Potential an CAN\_L gegen 0 V. In diesem Zustand werden die Technologiegrenzen von den Drain-Source Spannungen an den Transistoren nicht verletzt. Da das Potential CAN\_L durch die hohe differentielle Spannung in diesem Zustand nach unten getrieben wird, sind auch die Potentiale an den Punkten h und j sehr gering. Die Drain-Source Spannungen über die Transistoren sind in diesem Zustand unkritisch.

Da die Gatepotentiale der Transistoren M3 und M4 fest eingestellt sind, kommt es im dominanten Zustand, bei Potentialen unter 1,2 V für CAN\_L, zu einer kritischen Gate-Source Spannung an Transistor M3. Um diese kritische Spannung zu verhindern, wird im folgenden Kapitel eine Möglichkeit vorgestellt, mit der das Gatepotential an M3 abhängig vom Potential an CAN\_L eingestellt wird.

Abbildung 6: Transistorketten PMOS und NMOS Teil

#### 2.4.2. Biasschaltung

Wenn das Gatepotential an M3, wie im Kapitel 2.2. beschrieben, fest auf 2,4 V eingestellt wäre, dürfte das Potential CAN\_L die Grenzen von 1,2 V und 3,6 V nicht unter- bzw. überschreiten, da andernfalls die Gate-Source Spannung des Transistors M3 die von der Technologie vorgegebene Spannungsgrenze überschreiten würde. Aus diesem Grund wird für die Ansteuerung der Kaskodetransistoren M1 bis M4 in Abbildung 6 eine Biasschaltung eingeführt, welche ursprünglich aus der Schaltung eines ADSL Treibers stammt [3]. Abbildung 7 zeigt den NMOS Teil des CAN Treibers. Die Funktion wird anhand des NMOS Teils des Treibers erläutert und verhält sich entsprechend für den PMOS Teil.

Abbildung 7: NMOS CAN Treiber

Die Biasschaltung besteht aus den zwei Spannungsteilern R3/R4 und R8/R9 und den Transistoren M8 und M9, die für die Einstellung des Gatepotentials an M3 verwendet werden. Die Kapazitäten C4, C5 und C6 bilden RC-Glieder, mit denen die Umladegeschwindigkeiten der Gatepotentiale angeglichen werden kann. Die Kapazitäten C10 bis C12 werden eingeführt, um Spannungsspitzen im Umschaltmoment der Zustände zu kompensieren.

Das Steuersignal  $IN_N$  hat keinen direkten Einfluss auf die Gatepotentiale der Transistoren M3 und M4. Die Biasschaltung wird wie folgt mit dem Potential CAN\_L gesteuert.

Im dominanten Zustand sorgt die über den Terminierungswiderstand abfallende Spannung für ein niedriges Potential an CAN\_L und damit auch für ein niedriges Potential der Punkte o und p. Die Source-Gate Spannung des Transistors M9 sinkt und öffnet damit den Transistor. Die steigende Source-Gate Spannung an Transistor M8 schließt den Transistor und verbindet den Gateanschluss von Transistor M3 mit der 1,2 V Spannungsquelle VDD1V2. Durch dieses Verhalten kann das Potential CAN\_L bis auf 0 V sinken, ohne dass die Source-Gate Spannung des Transistors M3 die Technologiegrenzen überschreitet.

Im rezessiven Zustand wird das Potential CAN\_L auf einen Wert zwischen 2 V und 3 V eingestellt. In diesem Zustand wird das Gatepotential für M3 über den Spannungsteiler R8/R9 eingestellt. Das hohe Potential an CAN\_L schließt den Transistor M9 und öffnet den Transistor M8. Abbildung 8 zeigt eine veränderte Darstellung des Spannungsteiler R8/R9 über die Drain-Source Strecke von Transistor M9.

Abbildung 8: Spannungsteiler R8/R9

Das Potential g für den Gateanschluss von Transistor M3 wird mit folgender Formel berechnet.

$$U_g = \frac{R9}{R8 + R9} \times (U_{CAN_L} - 1.2 V)$$

Diese Formel vernachlässigt die Drain-Source Spannung über M9. Werden die Widerstände R8 und R9 gleich dimensioniert, so bildet sich der Vorfaktor 0,5 und das Potential g wird mittig zwischen den Potentialen CAN\_L und 1,2 V eingestellt. Durch dieses Verhalten kann das Potential CAN\_L bis auf 3,6 V steigen, ohne dass die Source-Gate Spannung des Transistors M3 den zulässigen Spannungsbereich überschreitet. Bei diesem maximalen Potential an CAN\_L von 3,6 V wird das Gatepotential von M3 auf 2,4 V eingestellt.

## 2.5. Gesamtschaltung

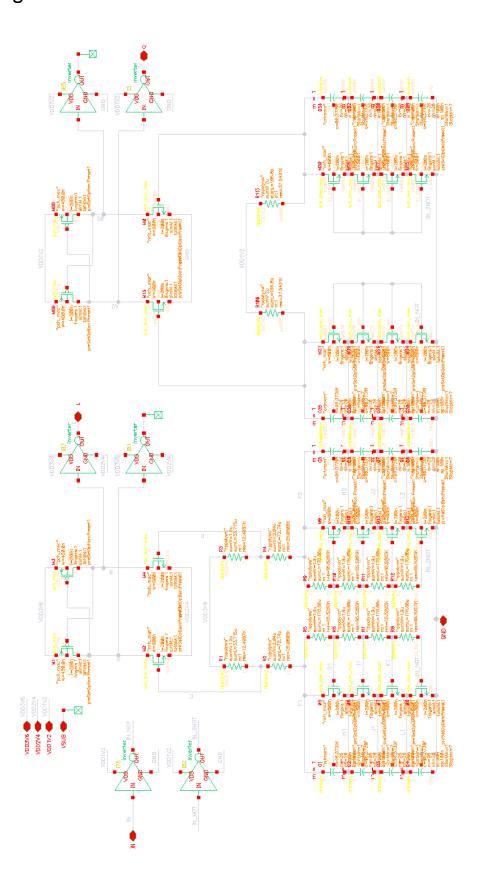

Abbildung 9 zeigt die Gesamtschaltung des CAN Treibers. Der Aufbau und die Funktion des NMOS Teils dieser Schaltung wurde in Kapitel 2 erläutert. Der PMOS Teil wird entsprechend gespiegelt realisiert. Der hinzugekommene Terminierungswiderstand R11 verbindet die beiden Teilschaltungen und erzeugt die differentielle Spannung im dominanten Zustand.

Abbildung 9: Gesamtschaltung CAN Treiber

Um diese Schaltung zu betreiben, wird ein Levelshifter zur Erzeugung beider Steuersignale  $IN_P$  und  $IN_N$  benötigt. Der Levelshifter wird im folgenden Kapitel vorgestellt.

## 3. Levelshifter

#### 3.1. Beschreibung und Anforderungen

Gegenstand dieses Kapitels ist die Entwicklung eines Levelshifters der zur Ansteuerung des vorgestellten CAN Treibers verwendet wird. Der CAN Treiber benötigt zu Erzeugung des BUS-Pegels zwei Eingangssingale. Um den CAN Bus in den rezessiven Zustand zu versetzen (logisch 1) wird für den NMOS Teil der Schaltung eine Spannung von 0 V und für den PMOS Teil der Schaltung eine Spannung von 3,6 V benötigt. Für den dominanten BUS Zustand (logisch 0), wird für den NMOS Teil eine Spannung von 1,2 V und für den PMOS Teil eine Spannung von 2,4 V benötigt. Die zu übertragenen Bits werden jedoch von der Buskontrolllogik als Standard CMOS Signale mit Pegeln zwischen 0 V und 1,2 V generiert. Der im folgenden beschriebene Levelshifter muss daher das Steuersignal auf den Pegel 2,4V/3,6V wandeln und gleichzeitig die Synchronität zum Signal mit den niedrigen Pegeln gewährleisten. Die geforderte Übertragungsrate des CAN Treibers liegt bei 150 kbit/s, was einer Bitzeit von 6,67 µs entspricht. In der Simulation wurden die Steuersignale durch ein Taktsignal mit 75 kHz generiert, da eine Halbperiode dieses Taktsignals genau der geforderten Bitzeit entspricht.

#### 3.2. Grundmodell Levelshifter

In diesem Kapitel wird die grundlegende Funktion des gewählten Levelshifters erläutert und im Anschluss aufgezeigt, welche Änderungen und Erweiterungen vorgenommen werden müssen, um den Anforderungen des Projekts gerecht zu werden.

Levelshifter werden immer dann verwendet, wenn Steuersignale zwischen zwei Schaltungsteilen übertragen werden, die mit verschiedenen Versorgungsspannungen betrieben werden. Ohne die Signalanpassung durch den Levelshifter kann es an der Schnittstelle zwischen den zwei Spannungsversorgungsdomänen zu erhöhten Ruheströmen kommen.

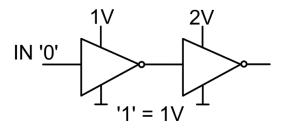

Abbildung 10: Einfacher Inverter

Wie in Abbildung 10 am Beispiel eines einfachen Inverters zu sehen ist, kann es beispielsweise dazu kommen, dass auf Grund der Signalfehlanpassung alle Transistoren des Inverters in der Versorgungspannungsdomäne mit der höheren Spannung geschlossen sind und sich dadurch ein Strompfad von der Versorgungsspannung zu Masse ergibt, was zu einer höheren statischen Leistungsaufnahme führt.

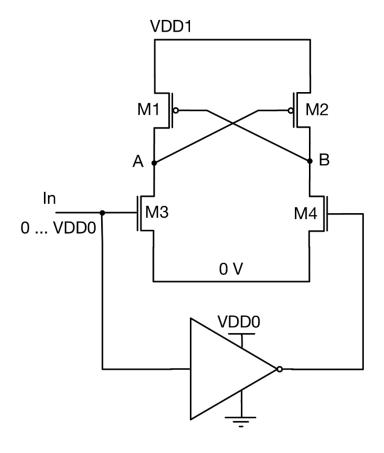

Abbildung 11: Grundmodell Levelshifter

Zur Umgehung dieser Problematik werden Schaltungen wie die in Abbildung 11 eingesetzt. Die NMOS und PMOS Strukturen sind im linken und rechten Pfad identisch dimensioniert. Im unteren Teil der Abbildung befindet sich ein Inverter, der für eine invertierte Ansteuerung der beiden Schaltungspfade sorgt. Zusätzlich werden oft weitere Inverter am Eingang und Ausgang zur Entkopplung des Levelshifters von den vor und nachgeschalteten Gattern verwendet.

Bei einer logischen 1 am Eingang In des Levelshifters liegt die Spannung VDD0 am Gate des Transistors M3 an, während das Gate des Transistors M4 auf Masse gezogen wird. Dadurch ist M3 geschlossen und M4 geöffnet. Resultierend aus den Strömen, welche die Transistoren M3 und M4 einprägen, erhöht sich die Gatespannung des Transistors M1, während sich am Gate des Transistors M2 ein niedriges Potential einstellt. Potential B nähert sich demnach bei einer logischen 1 am Eingang des Levelshifters der Versorgungsspannung VDD1, während das Potential A auf Masse bleibt. Durch den symmetrischen Aufbau stellen sich die inversen Spannungsverhältnisse bei einer Ansteuerung des Levelshifters mit einer logischen 0 ein. Potential A oder B können als Ausgang des Levelshifters verwendet werden. Das Ausgangssignal zeichnet sich dadurch aus, dass es im High-Zustand den neuen Pegel VDD1 annimmt. Während des Betriebes sind immer entweder der PMOS Transistor oder der NMOS Transistor, der im gleichen Zweig der Schaltung liegt, geöffnet. Dadurch kommt es zu keiner erhöhten statischen Leistungsaufnahme.

Die folgende Grafik zeigt die für die Ansteuerung des CAN Treibers benötigten Pegel, welche der Levelshifter liefern muss.

Abbildung 12: Ausgangspegel Levelshifter

Der in rot dargestellte Signalverlauf entspricht dem Gatepotential des PMOS Transistors im CAN Treiber, während der blau gefärbte Signalverlauf dem Gatepotential des NMOS Transistors darstellt. Durch dieses Muster werden PMOS und NMOS Teil gleichzeitig geschlossen bzw. geöffnet, wodurch sich der CAN BUS entweder im rezessiven oder dominanten Zustand befindet. Um mit der Schaltung aus Abbildung 11 die geforderten Pegel zu erzeugen ist es nötig, dass die untere Spannung des Levelshifters auf 2,4 V und die obere Spannung auf 3,6 V angehoben wird. Eine besondere Herausforderung stellt die Ansteuerung der Transistoren M3 und M4 in diesem Fall dar. Durch das Eingangssignal, welches Standard CMOS Pegel verwendet, ist es nicht möglich die Transistoren M3 und M4 vollständig zu öffnen und zu schließen. In Kapitel 3.3 wird eine einstellende Schaltung vorgestellt, die dieses Problem löst.

Da der CAN Treiber sehr empfindlich auf eine Asynchronität zwischen dem PMOS und dem NMOS Steuersignal reagiert ist es nicht möglich das Levelshifter Eingangssignal direkt an den Gateanschluss des NMOS Transistors im CAN Treiber weiterzuführen. Stattdessen ist es nötig die im Levelshifter erzeugte Laufzeit sowie den Flankenverlauf des PMOS Signals für das NMOS Signal nachzubilden. Die verwendete Synchronisierungsschaltung wird in Kapitel 3.4 vorgestellt.

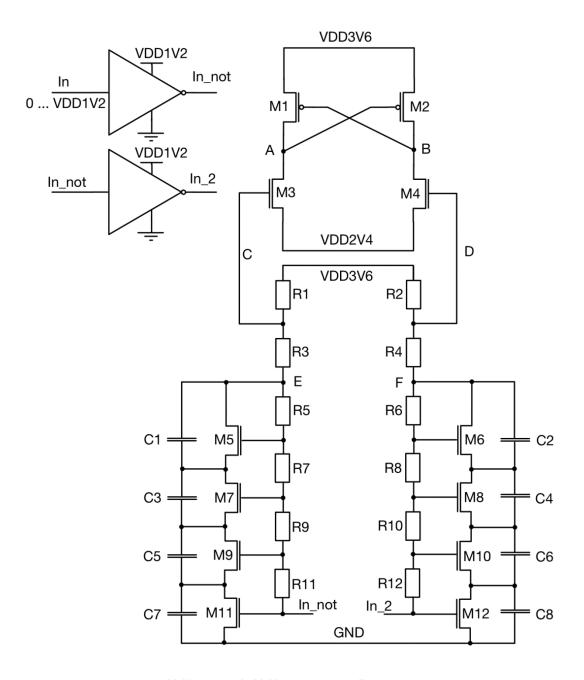

# 3.3. Einstellung des Levelshifters

In diesem Kapitel wird die Schaltung vorgestellt, welche die Pegelanpassung für die Gate-Spannungen der NMOS Transistoren M3 und M4 durchführt, um diese vollständig öffnen und schließen zu können. Abbildung 13 zeigt die vollständige Schaltung, die neben dem bereits vorgestellten Levelshifter noch einen weiteren Schaltungsteil umfasst, mit der die Pegelanpassung der Eingangssignale erzielt wird.

Abbildung 13: Schaltbild Transistoreinstellung VDD3V6

Dieser zusätzliche Schaltungsteil besteht im Wesentlichen aus zwei Spannungsteilern mit konfigurierbaren Teilungsfaktor. Da die Erweiterung für beide Signalpfade vollkommen symmetrisch aufgebaut ist, wird im Folgenden nur ein Signalpfad beschrieben. Ein Teil des Spannungsteilers, R5 bis R12, wird je nach Schaltungszustand zugeschaltet oder durch parallel geschaltete Transistoren kurzgeschlossen. Durch den Ansatz des variablen Spannungsteilers ist es möglich die Pegeländerung der Signale C und D soweit zu erhöhen, dass M3 und M4 entweder durchgehend geschlossen oder geöffnet bleiben. Der Spannungsteiler besteht aus dem Widerstand R3, welcher doppelt so groß dimensioniert als der Widerstand R1 ist und den Widerständen R5 bis R12, welche um den Faktor 5 größer als R1 sind. Die NMOS Transistoren M5 bis M12 sind nach dem Stacked-Transistor Prinzip verschaltet. Die Kapazitäten, die den Drain-Source Strecken zugeschaltet sind, verhindern hohe Spannungsspitzen während der Umschaltvorgänge, um Spannungen oberhalb von 1,32 Volt nicht zu überschreiten. Im Folgenden werden die beiden Schaltzustände anhand des linken Strompfades erläutert.

Wenn am Signal In\_not 0 V anliegt, ist der Transistor M11 geöffnet. Der Strom aus der Spannungsquelle VDD3V6 fließt durch die Widerstandskette und wird anschließend im ansteuernden Inverter nach Masse abgeleitet. Durch die hohen Widerstandswerte der Widerstände R5 bis R11 stellt sich an ihnen ein hoher Spannungsabfall ein. Das Potential E steigt somit zu hohen Werten. Die Spannungsteilung zwischen R1 und R3, R5, R7, R9, R11 stellt die Spannung am Knoten C ein, welcher mit dem Gate von M3 verbunden ist und erreicht ebenfalls sehr hohe Werte bei nahezu 3,6V. Die Gate-Source Spannung an M3 erreicht somit einen Wert von nahezu 1,2 V. Mit dieser hohen Spannung am Gate von M3 ist der Transistor im geschlossenen Zustand.

Im komplementären Zustand liegt an In\_not eine Spannung von 1,2 V an. Der Transistor M11 ist somit geschlossen und durch die Anhebung der Gate-Potentiale der Transistoren M5-M9 werden auch diese Transistoren leitfähig. In Folge werden die Widerstände R5, R7, R9 und R11 durch die parallel geschalteten Transistoren kurzgeschlossen. Da R3 doppelt so groß wie R1 gewählt wurde und die Spannung am Punkt E nahezu 0 V entspricht, stellt sich ein minimaler Spannungswert von 2,4 V ein. Mit einer Spannung von 2,4 V an Punkt C ist sichergestellt, dass M3 geöffnet ist.

Da zwischen den beiden Eingängen In\_not und In\_2 eine Invertierung vorliegt, ist immer nur ein Pfad im geöffneten Zustand, während der andere Pfad sich im geschlossenen Zustand befindet. Auch die Ausgänge A und B stellen jeweils das Ausgangssignal und dessen Invertierung zur Verfügung. Zur Entkopplung des Levelshifters wird ein Inverter an den Ausgang geschaltet. Für eine symmetrische Belastung der beiden Zweige befindet sich im anderen Zweig ebenfalls ein Inverter.

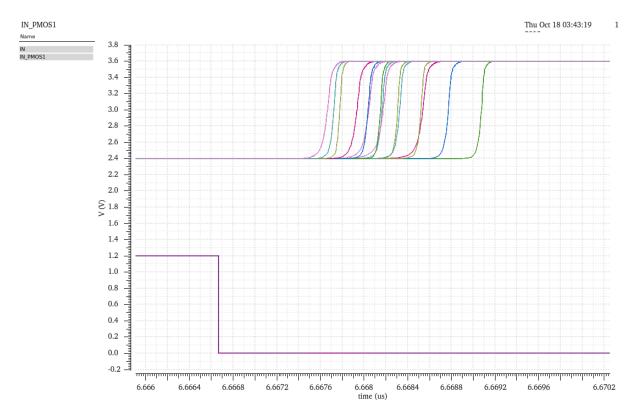

## 3.4. Synchronisation der NMOS/PMOS Steuersignale des CAN Treibers

In diesem Kapitel wird die Problematik behandelt, welche sich durch eine zeitliche Verzögerung zwischen den PMOS und NMOS Steuersignalen im CAN Treiber ergibt. Abbildung 14 stellt das, mit der Schaltung aus Kapitel 3 erzeugte PMOS Steuersignal dem NMOS Signal gegenüber, welches auch gleichzeitig das Eingangssignal des Levelshifters darstellt.

Abbildung 14: Oberes Ausgangssignal und Eingangssignal

Im oberen Bereich der Abbildung 14 sind die Simulationsergebnisse des Levelshifter Ausgang bzw. des PMOS Steuersignals über alle Corner und für die Temperaturen -40 °C, 27 °C sowie 120 °C dargestellt, während im unteren Bereich das Levelshifter Eingangssignal bzw. das NMOS Steuersignal dargestellt ist. Durch Simulationen am CAN Treiber hat sich herausgestellt, dass es bereits ab einer Signalverzögerung zwischen den NMOS und PMOS Steuersignalen von 200 ps zu Transistorspannungen jenseits der 1,32 V Grenze kommt. Es ist daher dringend nötig die beiden Ausgangssignale zueinander zu synchronisieren.

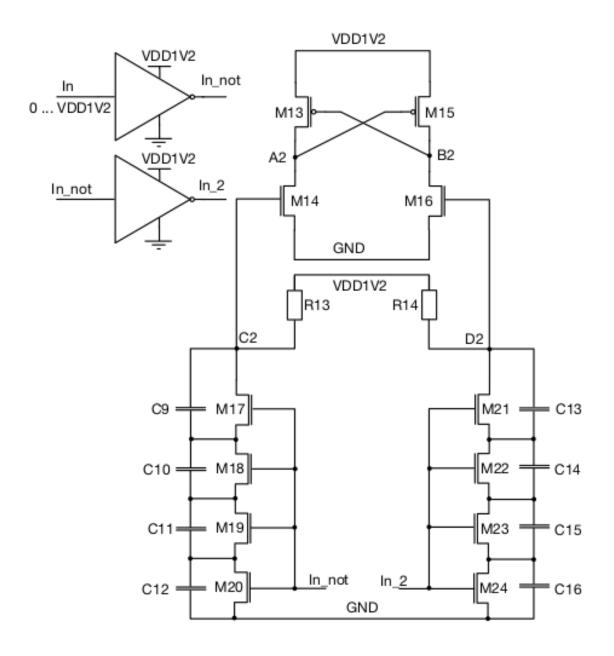

Ein Ansatz für die Synchronisation zwischen dem PMOS und dem NMOS Steuersignal besteht darin, den Signalpfad der NMOS Steuerung an die der PMOS Steuerung anzupassen. Hierfür wird die in Abbildung 15 gezeigten Schaltung verwendet.

Abbildung 15: Schaltbild Transistoreinstellung VDD1V2

Diese Schaltung ist bis auf wenige Anpassungen eine Kopie der Schaltung des Levelshifters aus Abbildung 13 zur Erzeugung des PMOS Steuersignals. Um die benötigten Pegel für das NMOS Steuersignal zu erzeugen, wird die Versorgungsspannung des Levelshifters auf 1,2 V und der Masseanschluss auf 0 V gesetzt. Da der Levelshifter in diesem Fall nicht mit einer erhöhten Versorgungsspannung betrieben wird, ist es auch prinzipiell nicht mehr nötig, den Pegel des Eingangssignals über eine Widerstandkette mit konfigurierbaren Spannungsteilerfaktor einzustellen. Simulationen haben gezeigt, dass die Entfernung dieser Widerstände keinen signifikanten Einfluss auf

die Signallaufzeit nimmt und damit auch die Synchronisierung zwischen dem NMOS und dem PMOS Transistorsignal nicht beeinflusst. Durch die Entfernung der hochohmigen Widerstände kann jedoch erheblicher Flächenanteil im Layout eingespart werden, ohne die Kernfunktionalität der Schaltung zu gefährden.

Da die Schaltung aus zwei symmetrisch aufgebauten Zweigen besteht, wird die Funktion der Schaltung anhand eines Schaltungszweiges erläutert.

Wird an die Schaltung eine logische 1 angelegt, wird das Signal In\_not zu einer logischen 0 invertiert. In diesem Zustand sind die Transistoren M17, M18, M19 und M20 geöffnet. Der Knoten C2 wird dann auf die Spannung von 1,2V aufgeladen, welche von der Spannungsquelle VDD1V2 eingeprägt wird. Damit steigt die Gate-Source Spannung des Transistors M14 ebenfalls auf 1,2 V, wodurch M14 geschlossen wird.

Wird an die Schaltung eine logische 0 angelegt, wird das Signal In\_not zu einer logischen 1 invertiert. Die Transistoren M17, M18, M19 und M20 sind dann geschlossen. Dadurch wird der Knoten C2 über die geschlossenen Transistoren niederohmig mit dem Massepotential verbunden. Das Potential C2 entspricht dann den aufsummierten Drain-Source Spannungen der in Reihe geschalteten Transistoren und ist so gering, dass sich Transistor M14 öffnet.

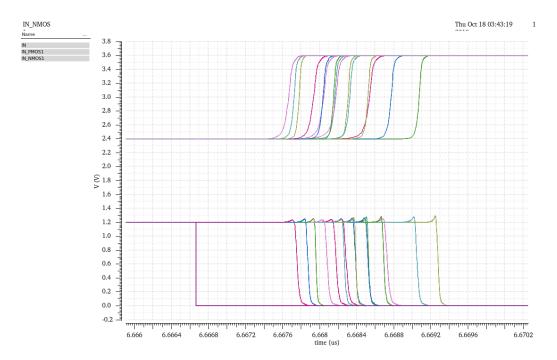

Abbildung 16: Steuersignale NMOS (unten) und PMOS (oben)

Im unteren Teil von Abbildung 16 ist die synchronisierte NMOS Steuerspannung dargestellt. Es ist deutlich zu sehen, dass sich die Temperaturvarianz und die Prozess Corner sehr ähnlich auf beide Steuerspannungen auswirken.

#### 3.5. Endergebnis und weitere Aufgaben

In diesem Kapitel werden die Ergebnisse zusammengefasst und analysiert. Ein Schaltplan der Gesamtschaltung (Abbildung A1) und Tabellen mit den Dimensionierungen aller Bauteile (Tabelle A3 bis A6) findet sich im Anhang. Darüber hinaus ist dem Anhang A2 eine Simulation mit steigender und fallender Flanke beider Steuersignale beigefügt worden. Tabelle 1 zeigt die Verzögerungen dem PMOS und dem NMOS Steuersignal für verschiedene Temperasturen und Prozess Corner. Ein positiver Wert bedeutet, dass die Flanke des NMOS Steuersignals nacheilt.

| Temperatur | Corner | Delay Rising Edge | Delay Falling Edge |

|------------|--------|-------------------|--------------------|

| in °C      |        | in ps             | in ps              |

| -40        | ff     | 183               | 87                 |

| 27         | ff     | 151               | -22                |

| 120        | ff     | 91                | -166               |

| -40        | fs     | 242               | 157                |

| 27         | fs     | 232               | 63                 |

| 120        | fs     | 149               | -127               |

| -40        | sf     | 173               | 76                 |

| 27         | sf     | 200               | 23                 |

| 120        | sf     | 115               | -147               |

| -40        | SS     | 203               | 96                 |

| 27         | SS     | 283               | 118                |

| 120        | SS     | 193               | -73                |

| -40        | tt     | 222               | 127                |

| 27         | tt     | 224               | 55                 |

| 120        | tt     | 137               | -117               |

Tabelle 1: Verzögerung der Ausgangssignale

Für die steigende Flanke ergibt sich eine mittlere Verzögerung von 186 ps. Die Differenz zwischen der kleinsten und der größten Verzögerung beträgt 192 ps. Für die fallende Flanke ist der Mittelwert nicht aussagekräftig, da die negativen Verzögerungswerte das Resultat verfälschen. Um den CAN Treiber zuverlässig anzutreiben ist eine weitere Schaltung nötig, die die Verzögerungen ausgleicht und die Anstiegs- und Abfallzeiten der Flanken reduziert. Diese Schaltung wird unter anderem Gegenstand des nächsten Kapitels.

Die vorgestellte Levelshifter Schaltung erfüllt damit alle Anforderung, welche an sie gestellt worden sind. Die Schaltung ist strahlenhart, da keine Transistoren mit minimaler Länge oder Breite verwendet wurden. In der transienten Analyse werden die Spannungsbegrenzungen für Core Transistoren zu keinem Zeitpunkt überschritten. Der Levelshifter erzeugt die geforderten Ausgangssignale in allen Prozess-Cornern und über den geforderten Temperaturbereich.

# 4. Simulationsergebnisse CAN Treiber und Levelshifter

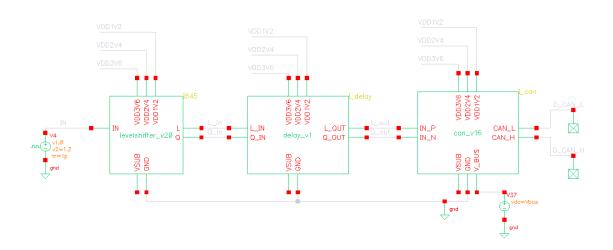

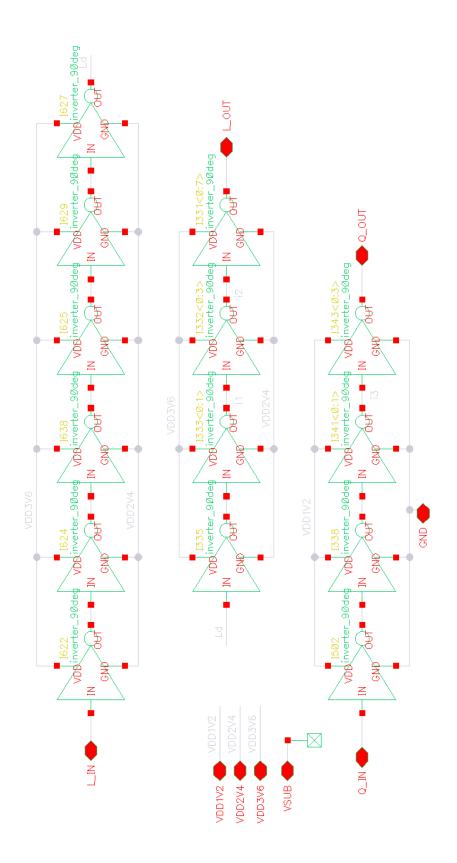

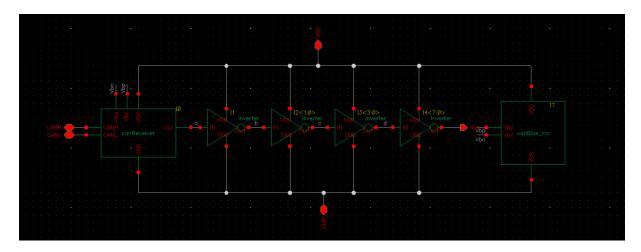

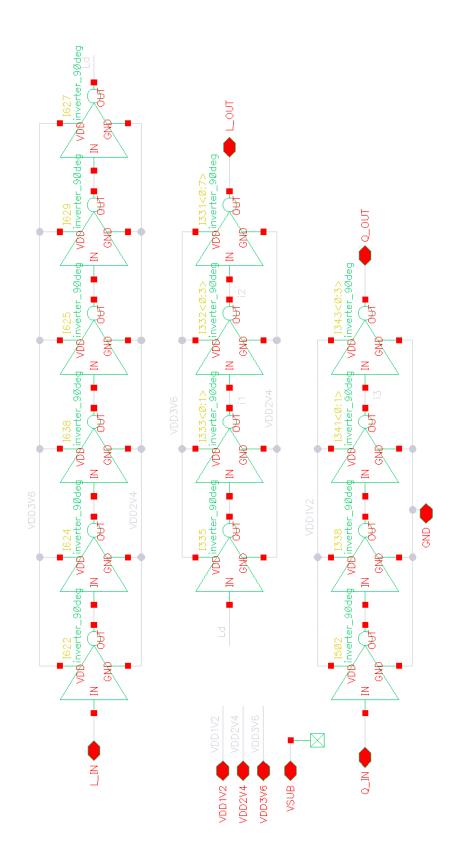

Da die Transistoren im CAN Treiber auf eine zeitliche Asynchronität der Steuersignale empfindlich reagieren, wird eine Verzögerungsschaltung auf beide Steuersignale angewendet. Diese Verzögerungsschaltung wird als Inverterkette realisiert und erhöht gleichzeitig die Flankensteilheit der Steuersignale. Die zeitliche Differenz zwischen den Flanken der Steuersignale darf während eines Zustandswechsels maximal 150ps betragen. Die folgende Abbildung 17 zeigt ein Blockschaltbild bestehend aus Levelshifter, Verzögerungsschaltung und CAN Treiber.

Abbildung 17: Blockschaltbild gesamt

Um die zeitliche Asynchronität der Ausgangssignale anzupassen, werden für das Steuersignal des PMOS Teils 7 Inverter und für das Steuersignal des NMOS Teils 2 Inverter eingefügt. Jeder Inverter erzeugt eine Signalverzögerung von 32ps. Außerdem werden durch Stufen parallelgeschalteter Inverter die Flankensteilheiten erhöht, um die Signalformen der Steuersignale weiter anzupassen. Jede Stufe verfügt dabei über die doppelte Anzahl paralleler Inverter der vorherigen Stufe. Im PMOS Steuersignal werden 3 Stufen (Stufe 1: 2 parallel, Stufe 2: 4 parallel, Stufe 3: 8 parallel) verwendet, während im NMOS Steuersignal nur 2 Stufen verwendet werden. Zusammengefasst wird das PMOS Steuersignal mit 10 Verzögerungen um etwa 320ps verzögert. Das NMOS Steuersignal wird mit 4 Verzögerungen um 128ps verzögert.

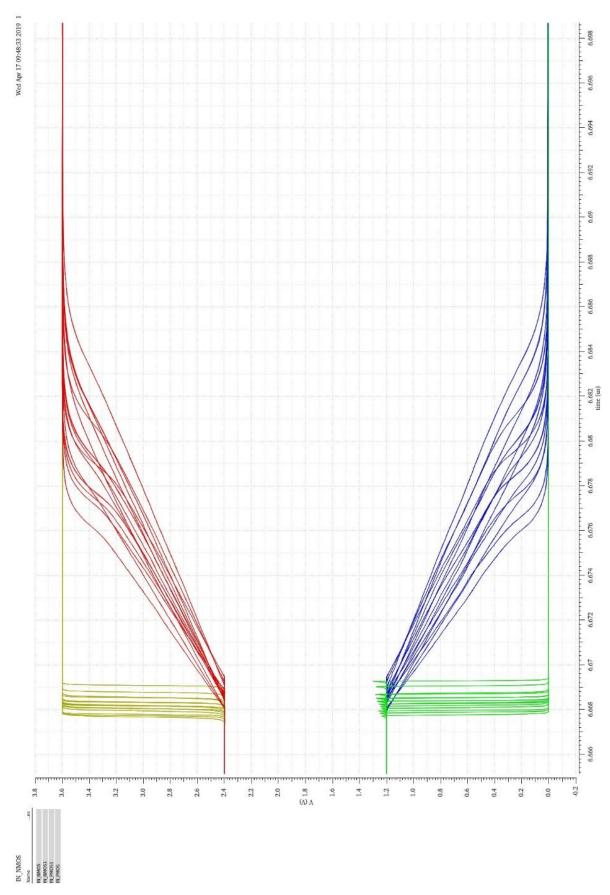

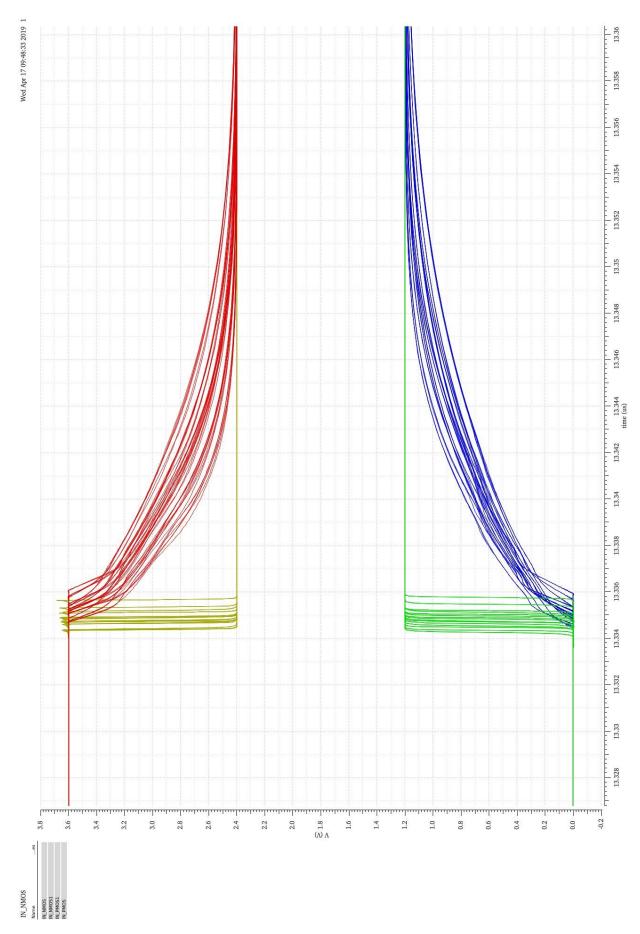

Abbildung 18 und Abbildung 19 zeigen den Signalverlauf für beide Steuersingale vor und nach der Verzögerungskette für die fallenden und steigenden Flanken.

Abbildung 20 zeigt den Aufbau der Verzögerungsschaltung.

Abbildung 18: Flanken vor und nach Verzögerungskette. Alle Corner. Steigende Flanke PMOS vor (rot) nach (gelb). Fallende Flanke NMOS vor (blau) nach (grün).

Abbildung 19: Flanken vor und nach Verzögerungskette. Alle Corner. Fallende Flanke PMOS vor (rot) nach (gelb). Steigende Flanke NMOS vor (blau) nach (grün).

Abbildung 20: Verzögerungskette. Oben: Verzögerung PMOS Steuersignal. Mitte: Flakensteilheit PMOS. Unten: Flankensteilheit NMOS.

#### 4.1. Simulationsergebnisse

Dieses Kapitel befasst sich mit Simulationsergebnissen des CAN Treibers. Der Levelshifter und die Verzögerungsschaltung sind in den Simulationen vorgeschaltet. Die Simulationen werden mit Cadence Virtuoso ADE XL durchgeführt. Der Schwerpunkt liegt in der Einhaltung der von den Technologiegrenzen vorgegebenen maximalen Spannungen an den Transistoren sowie in der Erzeugung eines CAN Ausgangssignals, welches den Anforderungen des CAN Standards genügt.

#### Simulationen:

• Cornersimulation (DC):

o Corner: tt, ff, ss, sf, fs

Temperatur: -40° C, 27° C, 120° C

Busspannung V<sub>bus</sub>: 2V, 2,5V, 3V

Monte Carlo (Mismatch) (TRANS):

o 200 Iterationen

• Monte Carlo (Process) (TRANS):

o 200 Iterationen

#### 4.1.1. Cornersimulation

Die folgenden Abbildungen zeigen die Konfigurationen für den Simulationsoutput sowie die Simulationsergebnisse für eine Busspannung von 2V und 3V. Die Grenzen von 2V und 3V werden vom CAN Standard als obere und untere Grenze für die Busspannung gesetzt. Der Ausdruck "No violations" zeigt, dass während der Simulation keine Verletzungen der Technologiegrenzen detektiert wurden.

Die Prüfung der Violations schließt die Schaltungen des Levelshifters und der Verzögerungskette ein.

Vergrößerte Ansichten des Signalverlaufs der differentiellen Spannung sowie der Signalverläufe der Spannungen CAN\_H und CAN\_L finden sich in Abbildung 24.

| Test   | Name    | Туре       | Details                        | EvalType | Plot     |

|--------|---------|------------|--------------------------------|----------|----------|

| corner |         | violations | Count 'All Checks/Asserts'     | point    | V        |

| corner | V_Diff  | expr       | (VT("/D_CAN_H") - VT("/D_CAN_L | point    | ✓        |

| corner | D_CAN_H | expr       | VT("/D_CAN_H")                 | point    | <b>✓</b> |

| corner | D_CAN_L | expr       | VT("/D_CAN_L")                 | point    | ✓        |

| corner | IN_PMOS | expr       | VT("/L_out")                   | point    | <b>✓</b> |

| corner | IN_NMOS | expr       | VT("/Q_out")                   | point    | ✓        |

Abbildung 21: Output Setup Cornersimulation

| Point - | Corner       | Vbus | temperature | toplevel.scs | Count 'All Checks/Ass |

|---------|--------------|------|-------------|--------------|-----------------------|

| 4       | all_models_l | 2    | -40         | ff_lib       | No violations         |

| 4       | all_models_l | 2    | 27          | ff_lib       | No violations         |

| 4       | all_models_l | 2    | 120         | ff_lib       | No violations         |

| 4       | all_models_l | 2    | -40         | fs_lib       | No violations         |

| 4       | all_models_l | 2    | 27          | fs_lib       | No violations         |

| 4       | all_models_l | 2    | 120         | fs_lib       | No violations         |

| 4       | all_models_l | 2    | -40         | sf_lib       | No violations         |

| 4       | all_models_l | 2    | 27          | sf_lib       | No violations         |

| 4       | all_models_l | 2    | 120         | sf_lib       | No violations         |

| 4       | all_models_l | 2    | -40         | ss_lib       | No violations         |

| 4       | all_models_l | 2    | 27          | ss_lib       | No violations         |

| 4       | all_models_l | 2    | 120         | ss_lib       | No violations         |

| 4       | all_models_l | 2    | -40         | tt_lib       | No violations         |

| 4       | all_models_l | 2    | 27          | tt_lib       | No violations         |

| 4       | all_models_l | 2    | 120         | tt_lib       | No violations         |

Abbildung 22: Cornersimulation Vbus = 2V

| Point $ abla$ | Corner       | Vbus | temperature | toplevel.scs | Count'All Checks/Ass |

|---------------|--------------|------|-------------|--------------|----------------------|

| 6             | all_models_l | 3    | -40         | ff_lib       | No violations        |

| 6             | all_models_l | 3    | 27          | ff_lib       | No violations        |

| 6             | all_models_l | 3    | 120         | ff_lib       | No violations        |

| 6             | all_models_l | 3    | -40         | fs_lib       | No violations        |

| 6             | all_models_l | 3    | 27          | fs_lib       | No violations        |

| 6             | all_models_l | 3    | 120         | fs_lib       | No violations        |

| 6             | all_models_l | 3    | -40         | sf_lib       | No violations        |

| 6             | all_models_l | 3    | 27          | sf_lib       | No violations        |

| 6             | all_models_l | 3    | 120         | sf_lib       | No violations        |

| 6             | all_models_l | 3    | -40         | ss_lib       | No violations        |

| 6             | all_models_l | 3    | 27          | ss_lib       | No violations        |

| 6             | all_models_l | 3    | 120         | ss_lib       | No violations        |

| 6             | all_models_l | 3    | -40         | tt_lib       | No violations        |

| 6             | all_models_l | 3    | 27          | tt_lib -     | No violations        |

| 6             | all_models_l | 3    | 120         | tt_lib       | No violations        |

Abbildung 23: Cornersimulation Vbus = 3V

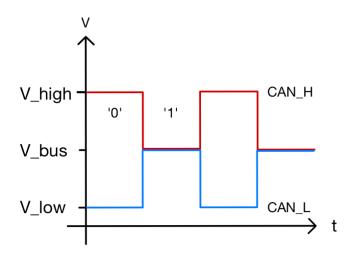

# 4.1.2. Transiente Signalanalyse

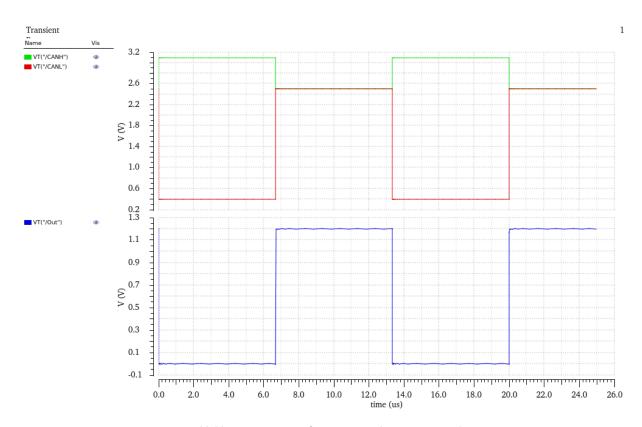

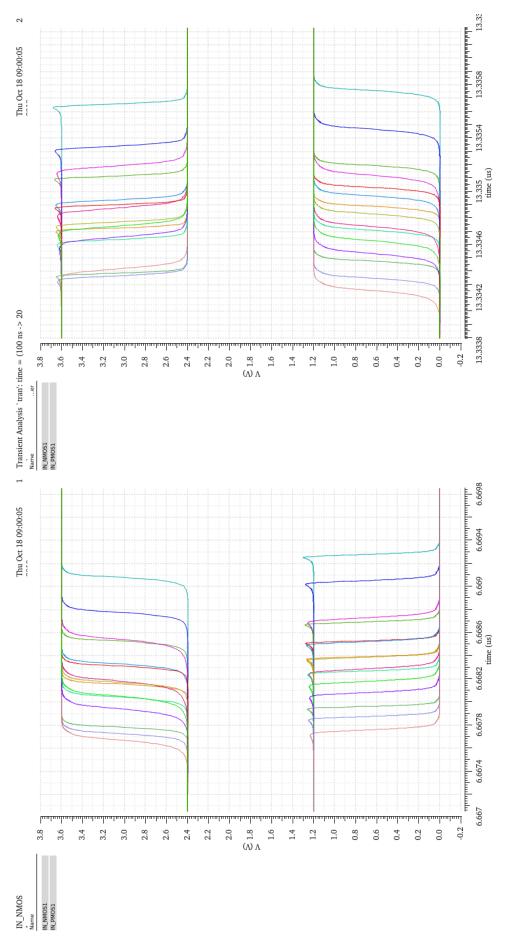

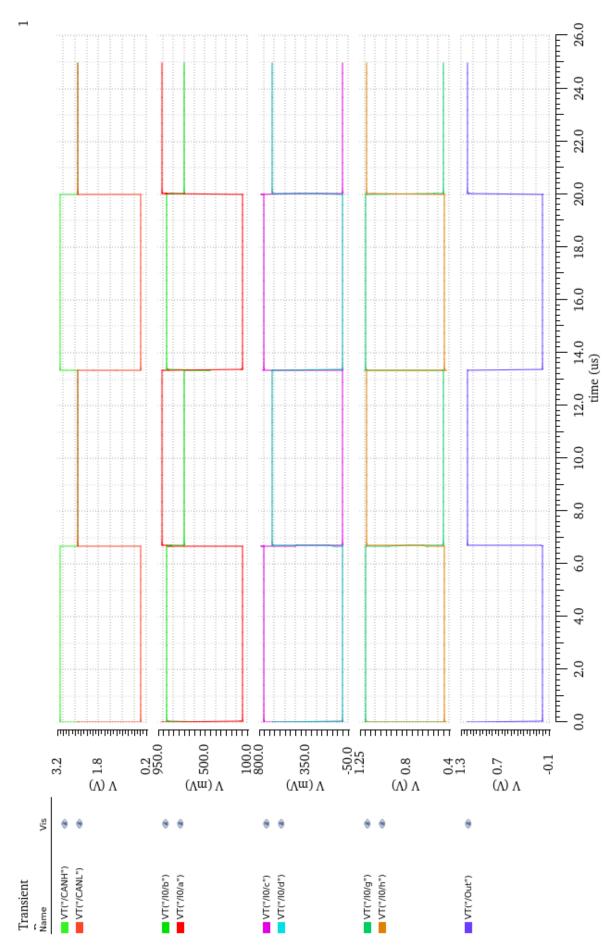

Abbildung 24: CAN\_H, CAN\_L, V\_Diff

Abbildung 24 zeigt eine transiente Simulation des CAN Treibers mit 75 kHz über 20 µs. Da eine Pulsbreite bei 75 kHz die Information von zwei Bits erzeugt, wird mit dieser Frequenz eine Bitrate von 150 kbit/s simuliert. Die Busspannung ist auf 2,5 V eingestellt. Die drei Temperaturen sowie die verschiedenen Corner werden in verschiedenen Farben dargestellt.

Der obere Graph zeigt die Spannung an CAN\_H. Der Graph in der Mitte zeigt die Spannung an CAN\_L. Im unteren Bereich wird die differentielle Spannung gezeigt. Im ersten und dritten Abschnitt auf der Zeitachse zeigt die differentielle Spannung einen Wert zwischen 2,5 V und 3 V. In diesen Bereichen ist der CAN Treiber im dominanten Zustand und übermittelt die logische "0". Im zweiten Bereich auf der Zeitachse ist der CAN Treiber im rezessiven Zustand und übermittelt die logische "1".

Es fällt auf, dass die benötigte Zeit zum Wechsel aus dem dominanten Zustand in den rezessiven Zustand etwa doppelt so viel Zeit in Anspruch nimmt, wie der Wechsel vom rezessiven Zustand in den dominanten Zustand. Der Umladevorgang des ersten Zustandswechsels dauert etwa 0,4 μs. Der zweite Umladevorgang dauert hingegen nur 0,2 μs. Dennoch sind die Auswirkungen des Umladevorgangs auf die differentielle Spannung nur im zweiten Wechsel (rezessiv zu dominant) sichtbar.

Weiterhin fällt auf, dass die Spannungsänderung während eines Zustandswechsels größtenteils zu Spannungsänderung auf CAN\_L führt. Dies ist darauf zurückzuführen, dass die im rezessiven Zustand angelegte Busspannung nicht mittig zwischen Versorgungsspannung und Massepotential liegt.

Ein letzter erwähnenswerter Punkt ist die Gruppierung der Graphen der differentiellen Spannung. Durch die drei verschiedenen Temperaturen bilden sich hier im dominanten Zustand drei Gruppen. Innerhalb dieser Gruppen findet eine geringere Variation durch die verschiedenen Prozess-Corner statt. Dieser Effekt wird durch mehrere verschiedene Einflüsse erzeugt. Der erste Einfluss ist die Änderung des Widerstandswertes des Terminierungswiderstandes und die Änderung des Kanalwiderstandes der Transistoren über die Temperatur. Eine frühere Arbeit an einer temperaturunabhängigen Spannungsreferenz (Bandgap) [1] zeigt, dass die Temperaturkoeffizienten von CMOS Transistoren und Widerständen mit umgekehrten Vorzeichen behaftet sind. Diese Einflüsse heben sich somit zum Teil auf. Die verbleibenden Einflüsse sind zu gering, um den Effekt der Gruppierung der Graphen über die Temperaturänderung zu erklären. Ein weiterer Einfluss ist die Abhängigkeit der Ladungsträgerbeweglichkeit über die Temperatur. Auch dieser Einfluss ist nur minimal und kann den gezeigten Effekt nicht erklären. Die ausschlaggebende Größe ist die Schwellenspannung. Mit sinkender Temperatur steigt die Schwellenspannung an. Obwohl der Einfluss der Ladungsträgermobilität einen gegensätzlichen Effekt beiträgt, reicht die Änderung der Schwellenspannung über die Temperatur aus, um einen sichtbaren Einfluss auf die differentielle Spannung zu nehmen. Ein Näherungswert für die Temperaturabhängigkeit der Schwellenspannung von CMOS Transistoren liegt bei -1 mV/°C. Durch eine abnehmende Schwellenspannung wird ein größerer Kanalstrom erzeugt. Mit diesem erhöhten Strom wird eine erhöhte Spannung über den Terminierungswiderstand erzeugt.

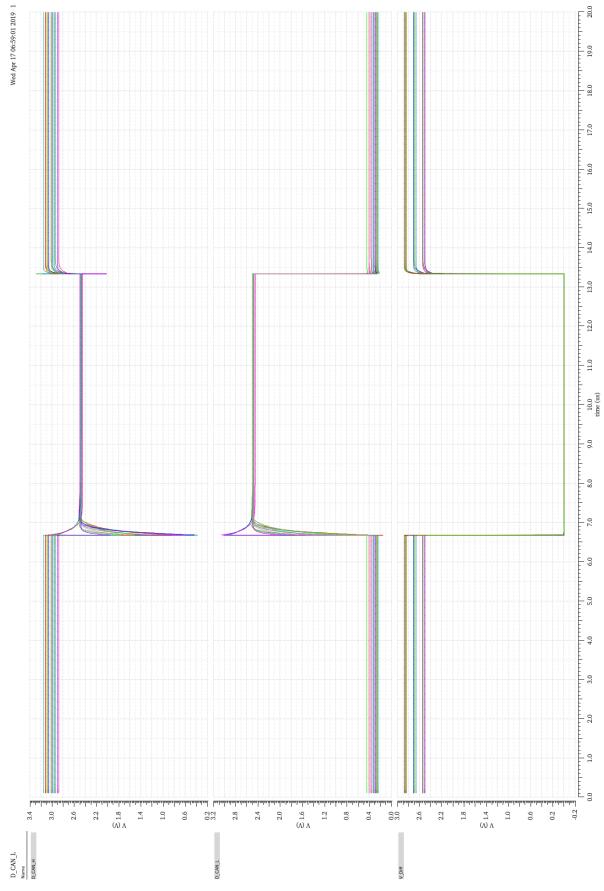

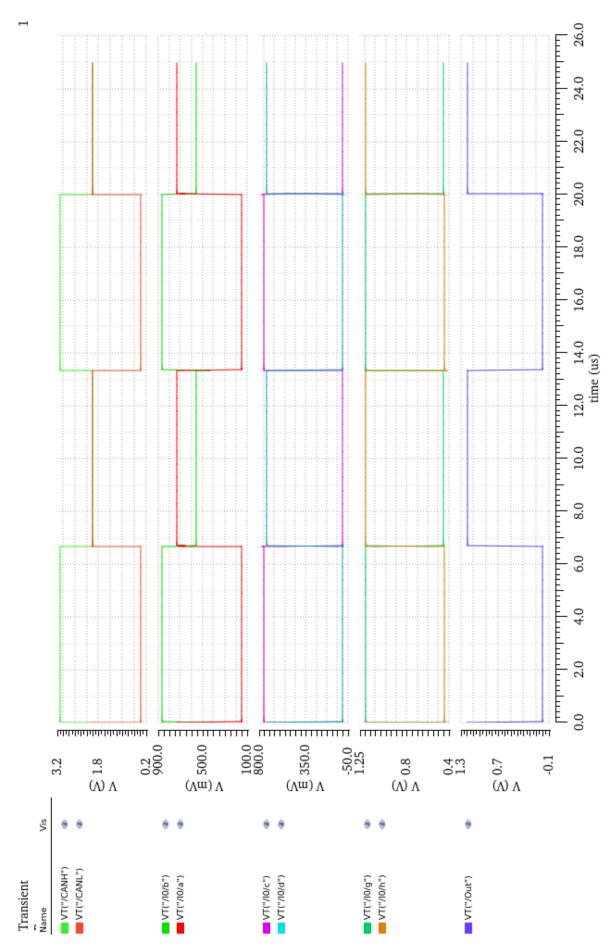

## 4.1.3. Monte Carlo (Mismatch)

Simulationsergebnisse der Monte Carlo (Mismatch) Simulation mit 200 Iterationen.

| Test        | Output▽ | Min    | Max    | Mean   | Median | Std Dev | Spec   | Pass/Fail |

|-------------|---------|--------|--------|--------|--------|---------|--------|-----------|

| mc_mismatch | M0_ds   | 777.5m | 1.257  | 962.9m | 919.3m | 173.7m  | < 1.32 | pass      |

| mc_mismatch | M0_gs   | 1.2    | 1.2    | 1.2    | 1.2    | 14.74u  | < 1.32 | pass      |

| mc_mismatch | M0_gd   | 1.046  | 1.257  | 1.104  | 1.082  | 69.35m  | < 1.32 | pass      |

| mc_mismatch | M1_ds   | 228.6m | 773.7m | 468.2m | 407.7m | 202m    | < 1.32 | pass      |

| mc_mismatch | M1_gs   | 1.047  | 1.101  | 1.075  | 1.076  | 17.41m  | < 1.32 | pass      |

| mc_mismatch | M1_gd   | 850.2m | 985.8m | 920.5m | 925.9m | 44.91m  | < 1.32 | pass      |

| mc_mismatch | M2_ds   | 442.6m | 1.148  | 802.9m | 792.5m | 285.2m  | < 1.32 | pass      |

| mc_mismatch | M2_gs   | 848.8m | 906.8m | 882.1m | 884m   | 21.47m  | < 1.32 | pass      |

| mc_mismatch | M2_gd   | 357.2m | 616.1m | 523.6m | 546.3m | 85.93m  | < 1.32 | pass      |

| mc_mismatch | M3_ds   | 651.5m | 1.094  | 886.9m | 913.6m | 187.6m  | < 1.32 | pass      |

| mc_mismatch | M3_gs   | 923.3m | 1.041  | 986.7m | 994.2m | 38.04m  | < 1.32 | pass      |

| mc_mismatch | M3_gd   | 735.2m | 944.5m | 845.6m | 857.4m | 67.88m  | < 1.32 | pass      |

| mc_mismatch | M4_ds   | 875.5m | 1.231  | 1.053  | 1.06   | 156.1m  | < 1.32 | pass      |

| mc_mismatch | M4_gs   | 1.078  | 1.137  | 1.109  | 1.111  | 18.13m  | < 1.32 | pass      |

| mc_mismatch | M4_gd   | 1.01   | 1.118  | 1.062  | 1.06   | 37.07m  | < 1.32 | pass      |

| mc_mismatch | M5_ds   | 982.8m | 1.217  | 1.129  | 1.151  | 77.79m  | < 1.32 | pass      |

| mc_mismatch | M5_gs   | 1.2    | 1.2    | 1.2    | 1.2    | 3.802u  | < 1.32 | pass      |

| mc_mismatch | M5_gd   | 1.115  | 1.217  | 1.157  | 1.154  | 36.95m  | < 1.32 | pass      |

| mc_mismatch | M6_ds   | 120.7m | 514.3m | 343m   | 372.7m | 132.7m  | < 1.32 | pass      |

| mc_mismatch | M6_gs   | 646.2m | 786.6m | 736m   | 750.9m | 50.96m  | < 1.32 | pass      |

| mc_mismatch | M6_gd   | 606.8m | 831.3m | 728.9m | 747.2m | 83.06m  | < 1.32 | pass      |

| mc_mismatch | M7_ds   | 361.6m | 630.5m | 500.9m | 495.5m | 96.22m  | < 1.32 | pass      |

| mc_mismatch | M7_gs   | 430.3m | 617.9m | 528m   | 539m   | 65.55m  | < 1.32 | pass      |

| mc_mismatch | M7_gd   | 120.7m | 514.3m | 343m   | 372.7m | 132.7m  | < 1.32 | pass      |

| mc_mismatch | M8_ds   | 1.006  | 1.21   | 1.103  | 1.089  | 76.84m  | < 1.32 | pass      |

| mc_mismatch | M8_gs   | 860.2m | 1.02   | 953.9m | 966.4m | 53.6m   | < 1.32 | pass      |

| mc_mismatch | M8_gd   | 895.5m | 1.023  | 957.6m | 961.6m | 41.68m  | < 1.32 | pass      |

| mc_mismatch | M9_ds   | 499.4m | 844.9m | 687.1m | 714.4m | 139.6m  | < 1.32 | pass      |

| mc_mismatch | M9_gs   | 1.012  | 1.217  | 1.112  | 1.103  | 77.54m  | < 1.32 | pass      |

| mc_mismatch | M9_gd   | 1.006  | 1.21   | 1.103  | 1.089  | 76.84m  | < 1.32 | pass      |

Abbildung 25: Monte Carlo (Mismatch)

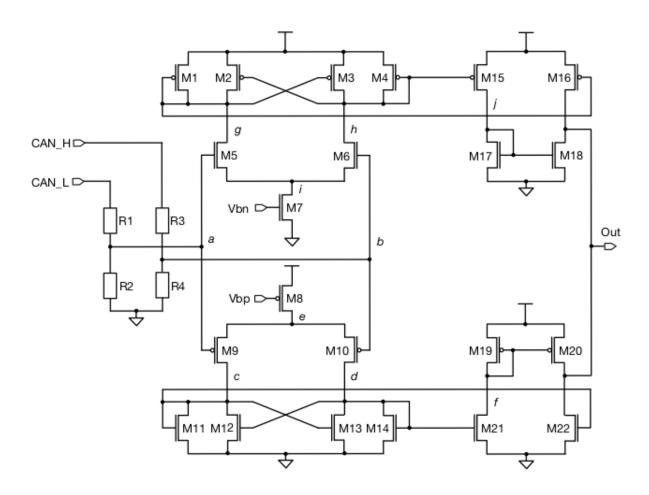

Bei der Monte Carlo Mismatch Simulation werden alle Transistorparameter zufällig variiert. Mit jeder erzeugten Iteration wird eine transiente Simulation durchgeführt. Die Auswertung (Abbildung 25) dieser Simulation fasst alle Iterationen zusammen und gibt für jeden Output ein minimales, maximales und durchschnittliches Simulationsergebnis sowie den Median und die Standardabweichung an. Außerdem kann in der Einstellung der Outputs eine Grenze (Spalte "Spec") angegeben werden, die in der Spalte "Pass/Fail" bewertet wird.

Für jeden Transistor werden drei Outputs in der Simulation verwendet. Jeweils einen für die Gate-Source, Drain-Source sowie Gate-Drain Spannung. Im Folgenden wird die verwendete Formel erläutert. Abbildung 26 zeigt die Einstellung der drei Outputs für den Transistor MO.

VT("C") – VT("A") erzeugt zuerst eine Differenz zwischen zwei Potentialpunkten des Transistors. VT() ist die Funktion, mit der in einer transienten Analyse ein Spannungswert ausgelesen wird. Als Übergabeparameter wird ein Netzname des Schaltplans benötigt. Durch die Differenzbildung zweier Potentiale wird die Spannung zwischen den zwei Punkten ermittelt. Die Funktion abs() erzeugt den Absolutwert des übergebenen Zahlenwertes. Dieser Schritt ist nötig, da die gesetzte Grenze negative Werte höherer Spannung als "pass" interpretiert. Die äußerste Funktion ist die ymax()-Funktion. Als Übergabeparameter werden Daten vom Typ "Waveform" benötigt, die durch eine transiente Analyse erzeugt werden (VT()). Die ymax()-Funktion gibt den maximalsten Wert auf der Y-Achse der übergeben Waveform zurück.

Die in Abbildung 26 genannten Netznamen A, B und C sind die Gate-, Drain- und Source-Potentiale des Transistors M0 und können Abbildung 9 entnommen werden.

Abbildung 26: Output Setup für Transistor M0

Die Simulationsergebnisse zeigen als maximalen Spannungsabfall an den Ports der Transistoren einen Wert von "< 1.32". Die Spannung darf in der transienten Simulation diesen Wert nicht übersteigen.

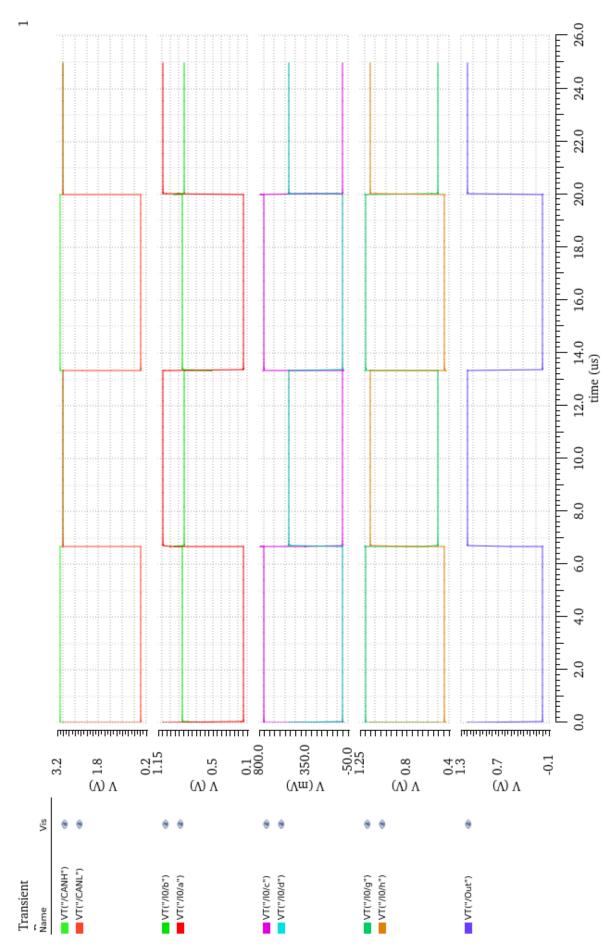

4.1.4. Monte Carlo (Process)

Simulationsergebnisse der Monte Carlo (Process) Simulation mit 200 Iterationen.

| Test       | Output▽ | Min    | Max    | Mean   | Median | Std Dev | Spec   | Pass/Fail |

|------------|---------|--------|--------|--------|--------|---------|--------|-----------|

| mc_process | M9_gs   | 831.6m | 1.256  | 1.11   | 1.133  | 91.46m  | < 1.32 | pass      |

| mc_process | M9_gd   | 831.3m | 1.25   | 1.101  | 1.12   | 91.07m  | < 1.32 | pass      |

| mc_process | M9_ds   | 489.7m | 847.3m | 687m   | 714.6m | 139.6m  | < 1.32 | pass      |

| mc_process | M8_gs   | 810.8m | 1.037  | 953.7m | 966.8m | 54.54m  | < 1.32 | pass      |

| mc_process | M8_gd   | 885.1m | 1.045  | 957.6m | 961m   | 42.68m  | < 1.32 | pass      |

| mc_process | M8_ds   | 831.3m | 1.25   | 1.101  | 1.12   | 91.07m  | < 1.32 | pass      |

| mc_process | M7_gs   | 383.3m | 672.9m | 535.6m | 540.3m | 68.1 m  | < 1.32 | pass      |

| mc_process | M7_gd   | 91.15m | 610.1m | 346.8m | 408.8m | 138.4m  | < 1.32 | pass      |

| mc_process | M7_ds   | 228.5m | 699m   | 499.6m | 476.7m | 109.1m  | < 1.32 | pass      |

| mc_process | M6_gs   | 440m   | 847.4m | 735.6m | 776.5m | 67.74m  | < 1.32 | pass      |

| mc_process | M6_gd   | 431m   | 885.1m | 728.9m | 770.4m | 93.36m  | < 1.32 | pass      |

| mc_process | M6_ds   | 91.15m | 610.1m | 346.8m | 408.8m | 138.4m  | < 1.32 | pass      |

| mc_process | M5_gs   | 1.2    | 1.2    | 1.2    | 1.2    | 5.571 u | < 1.32 | pass      |

| mc_process | M5_gd   | 1.106  | 1.275  | 1.16   | 1.152  | 38.95m  | < 1.32 | pass      |

| mc_process | M5_ds   | 958.1m | 1.275  | 1.131  | 1.157  | 79.75m  | < 1.32 | pass      |

| mc_process | M4_gs   | 1.069  | 1.155  | 1.11   | 1.11   | 18.59m  | < 1.32 | pass      |

| mc_process | M4_gd   | 984.3m | 1.174  | 1.063  | 1.064  | 40.12m  | < 1.32 | pass      |

| mc_process | M4_ds   | 741.8m | 1.251  | 1.054  | 1.098  | 162.4m  | < 1.32 | pass      |

| mc_process | M3_gs   | 901.5m | 1.053  | 986.7m | 995.1m | 38.39m  | < 1.32 | pass      |

| mc_process | M3_gd   | 731.6m | 968.2m | 845.6m | 857.1m | 68.61m  | < 1.32 | pass      |

| mc_process | M3_ds   | 597.6m | 1.152  | 896.3m | 968.6m | 182.8m  | < 1.32 | pass      |

| mc_process | M2_gs   | 839.5m | 927.1m | 883.3m | 883.3m | 22.54m  | < 1.32 | pass      |

| mc_process | M2_gd   | 299.4m | 673.1m | 532.5m | 586.6m | 85.61m  | < 1.32 | pass      |

| mc_process | M2_ds   | 349.9m | 1.25   | 807.6m | 822.1m | 285.4m  | < 1.32 | pass      |

| mc_process | M1_gs   | 1.043  | 1.106  | 1.075  | 1.078  | 17.35m  | < 1.32 | pass      |

| mc_process | M1_gd   | 840.6m | 997m   | 921.6m | 930.3m | 44.29m  | < 1.32 | pass      |

| mc_process | M1_ds   | 195.6m | 849.1m | 468.9m | 448.8m | 202.1m  | < 1.32 | pass      |

| mc_process | M0_gs   | 1.2    | 1.2    | 1.2    | 1.2    | 15.94u  | < 1.32 | pass      |

| mc_process | M0_gd   | 1.042  | 1.268  | 1.106  | 1.083  | 68.22m  | < 1.32 | pass      |

| mc_process | M0_ds   | 621.8m | 1.268  | 960.9m | 938m   | 181.2m  | < 1.32 | pass      |

Abbildung 27: Monte Carlo (Process)

# 5. CAN Empfänger

## 5.1. Beschreibung und Anforderungen

Dieses Kapitel befasst sich mit der Entwicklung eines CAN Empfängers. Der CAN Empfänger stellt das Gegenstück zum, in Kapitel 3 beschriebenen, CAN Treiber dar. Da der CAN Empfänger ebenfalls mit der 65 nm Technologie von TSMC gefertigt wird, sind die Anforderungen an diese Schaltung identisch.

Der DCS Chip wird gekühlt betrieben, weshalb der CAN Empfänger eine Signalverarbeitung bei -20 °C gewährleisten muss. Außerdem muss die Schaltung, genau wie die Schaltung des CAN Treibers, strahlenhart sein. Dies wird durch die Verwendung von Transistoren mit dünnem Oxid sichergestellt. Die Anforderung an die maximale Spannung über zwei Anschlüsse der Core Transistoren ist für die Schaltung des CAN Empfängers einfacher umzusetzen, da zur Verarbeitung des CAN Signals keine hohe Versorgungsspannung notwendig ist.

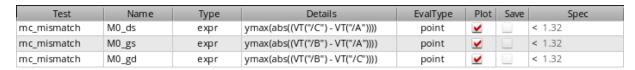

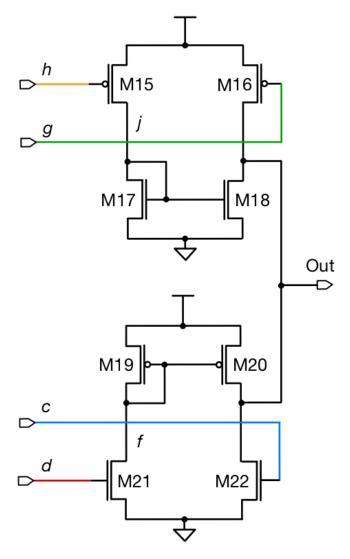

Abbildung 28: Gesamtschaltung CAN Empfänger

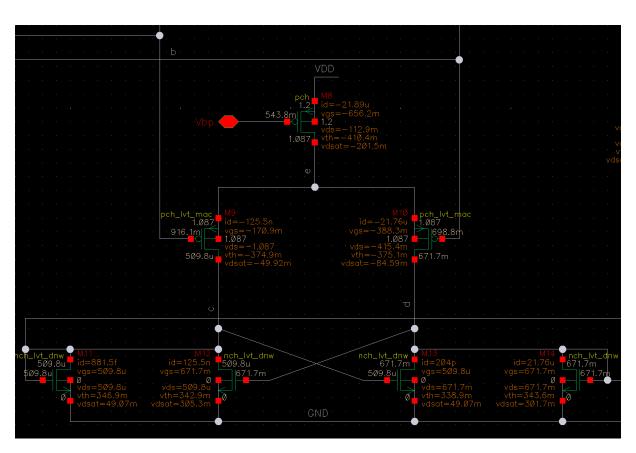

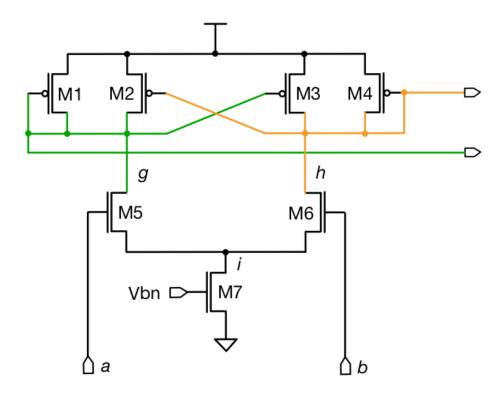

Abbildung 28 zeigt die gesamte Schaltung des CAN Empfängers. Die gezeigte Schaltung ist eine modifizierte Schaltung eines LVDS Drivers [2.1] [2.2]. Die Eingangssignale werden zuerst durch resistive Spannungsteiler auf Pegel gewandelt, welche die CMOS Schaltung ohne zusätzliche Schaltungstechniken wie Kaskodierung verarbeiten kann. Die geteilten Eingangsspannungen werden der eigentlichen Komparatorschaltung zugeführt, welche aus zwei parallel verschalteten Komparatoren besteht. Jeder Komparator verfügt jeweils über eine differentielle Eingangsstufe und eine Entscheidungsstufe. Durch die parallele Verschaltung ist es möglich, einen höheren Spannungsbereich der Eingangssignale abzudecken. Der im unteren Teil angesiedelte Komparator arbeitet mit einer differentiellen PMOS Eingangsstufe und einer NMOS Entscheidungsstufe und wird für Eingangssignale niedrigerer Spannung benötigt. Eingangssignale höherer Spannung werden vom oberen Schaltungsteil verarbeitet. Hier wird eine differentielle NMOS Eingangsstufe sowie eine Entscheidungsstufe mit PMOS Transistoren verwendet. Grundsätzlich ist hier anzumerken, dass beide Schaltungsteile in der Anwendung als CAN Empfänger arbeiten. Die Grenzen der einzelnen Schaltungsteile liegen außerhalb der CAN Standard Spezifikationen. Im Anschluss werden die Signale Verstärkern zugeführt, um ein Ausgangssignal mit einem CMOS Pegel von 1,2 V zu erzeugen. Im Folgenden werden die einzelnen Schaltungsbestandteile erläutert.

### 5.2. Eingangsstufe

Die Eingangsstufe (siehe Abbildung 28) besteht aus jeweils einem Spannungsteiler für die Eingangssignale CAN\_H und CAN\_L. Für die Spannungsteilung werden folgende Widerstände verwendet:

|        | _          |                      |  |  |

|--------|------------|----------------------|--|--|

|        | Widerstand | Teilerverhältnis     |  |  |

|        | in kΩ      | (Faktor zu CAN _H/L) |  |  |

| CAN II | R3 = 290   | 0.270                |  |  |

| CAN_H  | R4 = 112,5 | 0,279                |  |  |

| CAN I  | R1 = 255   | 0,366                |  |  |

| CAN_L  | R2 = 147,5 |                      |  |  |

Tabelle 2: Spannungsteiler CAN Empfänger Eingang

Die höchste Spannung auf CAN\_H wird erreicht, wenn ein dominantes Bit übertragen wird. Hier liegt die Spannung auf CAN\_H bei etwa 3,2 V (siehe Abbildung 24). Unter Berücksichtigung der Spannungsteilung ergibt sich für den Potentialpunkt b eine maximale Spannung von 830 mV. Die höchste Spannung für das Eingangssignal CAN\_L beträgt 3 V. Diese Spannung wird erreicht, wenn ein rezessives Bit übertragen wird und der Bus mit einer Busspannung von 3 V eingestellt wird. Unter Berücksichtigung der Spannungsteilung ergibt sich für Potentialpunkt a eine Spannung von 1,01 V. Das Potential b liegt bei einer Eingangsspannung von 3 V bei 0,84 V. Die beiden Potentialpunkte a und b werden im Folgenden als Eingangssignale für zwei Komparatoren verwendet, die zwischen einer Versorgungsspannung von 1,2 V und Masse arbeiteten. Dadurch ist sichergestellt, dass an keinem Transistor zu keiner Zeit eine Spannung größer als 1,2 V anliegt.

Des Weiteren wird durch die Wahl unterschiedlicher Teilerverhältnisse eine Differenz zwischen den beiden Eingangssignalen erzeugt. Dies ist notwendig, da bei der Übertragung im rezessiven Zustand die Potentiale der Eingangssignale nahezu identisch sind. Da die Eingangssignale die differentiellen Eingangsstufen zweier Komparatoren ansteuern, ist hier eine Differenz zwischen den beiden Signalen notwendig, um ein definiertes Schaltverhalten im rezessiven Zustand zu gewährleisten und rauschinduzierte Schwingungen des Komparators bei gleichen Eingangssignalen zu vermeiden.

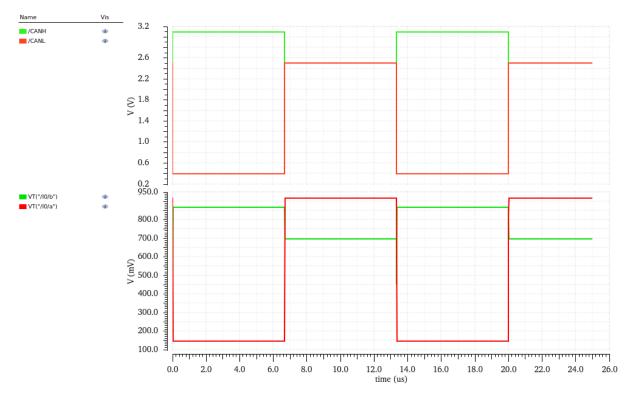

Abbildung 29 zeigt eine transiente Simulation der Eingangssignale CAN\_H und CAN\_L (oben) sowie die Signale a und b (unten). Die Einstellungen der Signale CAN\_H und CAN\_L in dieser Simulation sind die eines typischen Ausgangssignals des CAN Treiber. Im dominanten Zustand ist das Potential auf CAN\_H 3,1 V und das Potential auf CAN\_L 0,4 V. Der dominante Zustand wird zwischen 0  $\mu$ s und 6,66  $\mu$ s sowie zwischen 13,33  $\mu$ s und 20  $\mu$ s simuliert. Der rezessive Zustand wird in den übrigen Bereichen simuliert. Die externe Busspannung besitzt bei den durchgeführten Simulationen den Wert 2,5 V.

Im unteren Bereich werden die Potentiale a und b gezeigt. Das Potential a wird rot dargestellt und aus der Spannungsteilung des Eingangssignals CAN\_L erzeugt (rot, oben). Das Potential b wird grün dargestellt und aus der Spannungsteilung des Signals CAN\_H erzeugt (grün, oben). Im dominanten Zustand bleibt das Potential b (CAN\_H) kleiner als das Potential a (CAN\_L). In dieser Ausrichtung ist die differentielle Spannung auf dem Bus als positiv definiert. Durch die Wahl unterschiedlicher Verhältnisse der Spannungsteiler findet im rezessiven Zustand ein Vorzeichenwechsel statt. Das aus dem Eingangssignal CAN\_L erzeugte Potential a ist jetzt höher als das aus dem Eingangssignal CAN\_H erzeugte Potential b. Durch die Einführung dieser negativen Differenzspannung können beide Zustände sicher durch die Schaltung identifiziert werden.

Abbildung 29: Eingangssignale und Potentiale a und b

## 5.3. Komparator mit PMOS Eingangsstufe

Dieser Abschnitt erläutert die Funktionsweise des Komparators mit PMOS Eingangsstufe des CAN Empfängers. Zuerst wird das in Abbildung 30 gezeigte Entscheidungsnetzwerk im unteren Schaltungsteil analysiert.

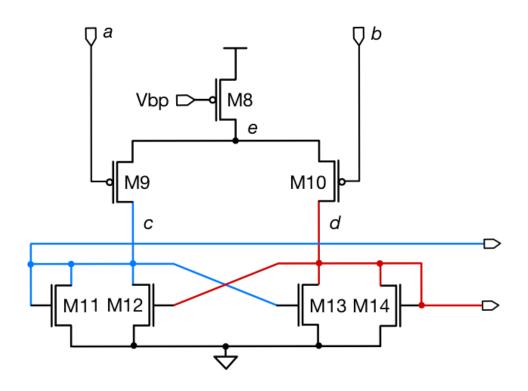

Abbildung 30: Entscheidungsnetzwerk mit PMOS Eingangsstufe

Die Versorgungsspannung des Komparators liegt bei 1,2 V. Die differentielle Eingangsstufe des Entscheidungsnetzwerks wird mit den PMOS Transistoren M9 und M10 gebildet. Die hier, an den Gateanschlüssen, anliegenden Steuersignale a und b haben zuvor die in Kapitel 5.2 besprochenen Spannungsteiler passiert. Die Eingangsstufe stellt sicher, dass in jedem gültigen Übertragungszustand eine Spannungsdifferenz zwischen a und b besteht.

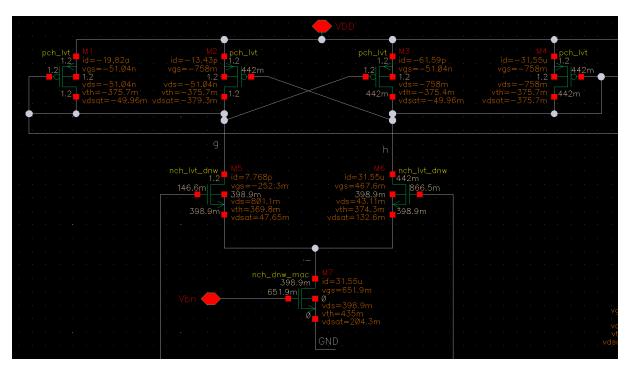

### 5.3.1. Dominanter Zustand im Komparator mit PMOS Eingangsstufe

Im dominanten Zustand stellt sich bei einer Eingangsspannung von 400 mV am Potentialpunkt a eine Spannung von 146 mV ein. Für den Potentialpunkt b stellt sich bei einer Eingangsspannung von 3,1 V eine Spannung von 866 mV ein. Der Potentialpunkt e stellt sich in diesem Zustand auf 771 mV ein. Bei dieser Einstellung befindet sich Transistor M9 in starker Inversion und leitet einen hohen Strom in das Netzwerk e. Transistor M10 ist aufgrund seiner hohen Gatespannung in schwacher Inversion und leitet nahezu keinen Strom ins Netzwerk e.

Die Gatespannung an Transistor M12 wird vom gegenüberliegenden Netz d eingestellt. Die niedrige Spannung in diesem Zweig öffnet Transistor M12. Die Gatespannung an Transistor M13 wird vom Netz c gesteuert und hat in diesem Zustand ein hohes Potential. Transistor M13 wird somit geschlossen und leitet sämtlichen Strom, der im Netz d fließt, nach Masse ab. Die übrigen beiden Transistoren M11 und M14 sind Gate-Drain verbundene Transistoren und wirken jeweils als der einstellende Teil eines Stromspiegels. Da das Netz c nicht über den geöffneten Transistor M12 nach Masse kurzgeschlossen wird, fließt der komplette Strom über Transistor M11 und die Spannung am Netz c stellt sich dementsprechend auch über den Gate-Drain verbundenen Transistor M11 ein. Die Potentiale c und d dienen als Eingangssignale für den folgenden Verstärker. Das Potential c nimmt ein hohes Potential an, während das Potential d ein sehr niedriges Potential annimmt. Abbildung 31 zeigt das Entscheidungsnetzwerk mit PMOS Eingangsstufe mit DC Arbeitspunkten im dominanten Zustand.

Abbildung 31: Entscheidungsnetzwerk mit PMOS Eingangsstufe. Arbeitspunkt im dominanten Zustand

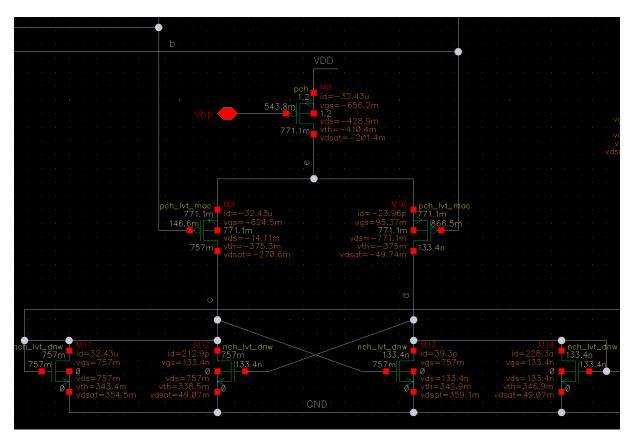

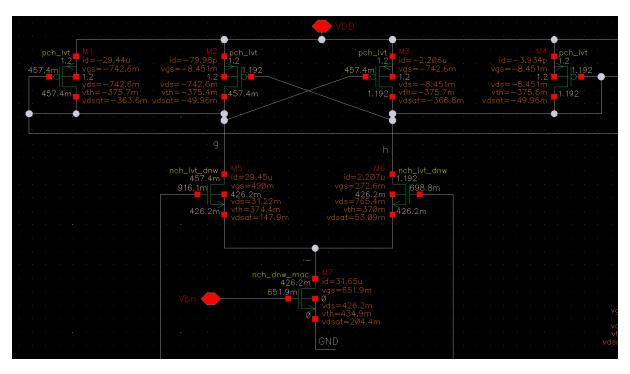

### 5.3.2. Rezessiver Zustand im Komparator mit PMOS Eingangsstufe

Im rezessiven Zustand liegt die Busspannung vor der Spannungsteilung bei 2,5 V auf CAN\_H und CAN\_L. Nach der Spannungsteilung liegt das Potential auf dem Potentialpunkt a bei 916 mV und das Potential auf dem Potentialpunkt b bei 698 mV. Das Potential des Netzwerks b stellt sich in diesem Fall auf 1,09 V ein. Mit dieser Eingangsbeschaltung befindet sich Transistor M10, mit einer Sättigungsspannung von 84,59 mV, in moderater Inversion. Transistor M9 befindet sich in schwacher Inversion und wird durch seine niedrige Gate-Source Spannung geöffnet.

In diesem Zustand wird ein hoher Strom in das Netzwerk d geführt. Das zugeführte Potential im Netzwerk d schließt den gegenüberliegenden Transistor M12, welcher den kompletten Strom der im Netz c fließt, nach Masse ableitet. Das niedrige Potential im Netzwerk c öffnet den gegenüberliegenden Transistor M13. Der Strom im Netz d fließt über den Gate-Drain verbundenen Transistor M14 nach Masse. Die Potentiale c und d dienen als Eingangssignale für den folgenden Verstärker. Das Potential d nimmt ein hohes Potential an, während das Potential c ein sehr niedriges Potential annimmt. Abbildung 32 zeigt das Entscheidungsnetzwerk mit PMOS Eingangsstufe mit DC Arbeitspunkten im rezessiven Zustand.

Abbildung 32: Entscheidungsnetzwerk mit PMOS Eingangsstufe. Arbeitspunkt im rezessiven Zustand

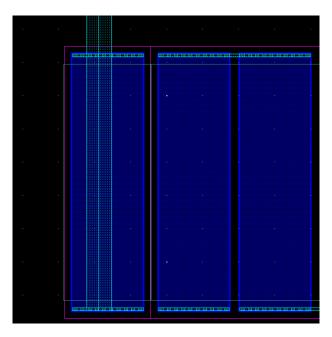

#### 5.3.3. Arbeitsbereich Transistor M8