#### **Bachelorthesis**

# Entwurf eines VHDL-Designs und einer Applikationssoftware zur Konfiguration und Kalibrierung eines optischen Winkelgebers

im Studiengang Elektrotechnik des Fachbereichs Elektrotechnik

Erstprüfer: Prof. Dr. Michael Karagounis

Zweitprüfer: Dipl.-Ing. Rolf Paulus

Abgabedatum: 11.11.2019

Vorgelegt von: Conrad Demske

#### Kurzzusammenfassung

# Entwurf eines VHDL-Designs und einer Applikationssoftware zur Konfiguration und Kalibrierung eines optischen Winkelgebers

Diese Thesis handelt von der Konfiguration und Kalibrierung eines optischen Winkelgebers, welcher mit einer Entwicklungsplatine verbunden ist. Auf dieser Platine befinden sich Bauteile, die Signale des optischen Winkelgebers erhalten. Die digitalen Ausgangssignale der Bauteile auf der Entwicklungsplatine sind wiederum mit einem FPGA verbunden. Für die Konfiguration des FPGAs wird ein VHDL-Design zur Ansteuerung dieser Bauteile entworfen. Außerdem wird eine Software zur Nutzung des VHDL-Designs entworfen.

#### **Abstract**

# VHDL design and application software for configuration and calibration of an optical angle encoder

This thesis is about the configuration and calibration of an optical angle encoder, which is connected to a development board. This board includes components that receive signals of the optical angle decoder. The digital output signals of the components on the development board are fed to an FPGA. For the configuration of the FPGA, a VHDL design will be designed to control these components. Furthermore, a software for the use of the VHDL design will be designed.

# Eidesstattliche Erklärung

| Hiermit versichere ich an Eides statt, dass die von mir v | orgelegte Prüfungsleistung selbst- |

|-----------------------------------------------------------|------------------------------------|

| ständig und ohne unzulässige fremde Hilfe erstellt wor    | den ist. Alle verwendeten Quellen  |

| sind in der Arbeit so aufgeführt, dass Art und Umfang     | der Verwendung nachvollziehbar     |

| sind.                                                     |                                    |

|                                                           |                                    |

|                                                           |                                    |

|                                                           |                                    |

|                                                           |                                    |

| Ort, Datum                                                | Unterschrift                       |

# Inhaltsverzeichnis

| Inhalt     | sverz   | eichnis                                                               | . I |

|------------|---------|-----------------------------------------------------------------------|-----|

| Abbil      | dungs   | sverzeichnis I                                                        | V   |

| Tabel      | lenve   | rzeichnisV                                                            | Ί   |

| Abkü       | rzung   | sverzeichnisV                                                         | II  |

| 1 I        | Einleit | tung                                                                  | 1   |

| 1.1        | Ei      | nführung in POLDI                                                     | 1   |

| 1.2        | K       | ommunikation zwischen Computer und POLDI                              | 2   |

| 1.3        | Zi      | el der Bachelorarbeit                                                 | 2   |

| 2 5        | Softwa  | are                                                                   | 4   |

| 2.1        | H       | DL Designer                                                           | 4   |

| 2.2        | Xi      | ilinx ISE 14.7 Design Suite                                           | 4   |

| 2.3        | Q'      | Γ-Creator                                                             | 5   |

| 2.4        | M       | ojo Loader                                                            | 7   |

| 3 I        | OACs    | und ADCs                                                              | 9   |

| 3.1        | D       | AC "AD5686"                                                           | 9   |

| 3          | 3.1.1   | Funktionsweise                                                        | 9   |

| 3          | 3.1.2   | Funktionsbeschreibung der für die FPGA-Ansteuerung relevanten Pins. 1 | 0   |

| 3          | 3.1.3   | Inhalt des 24-Bit-Eingangsschieberegisters                            | 1   |

| 3.2        | D       | AC "AD5544"1                                                          | 3   |

| 3          | 3.2.1   | Funktionsweise 1                                                      | 3   |

| 3          | 3.2.2   | Funktionsbeschreibung der für die FPGA-Ansteuerung relevanten Pins. 1 | 4   |

| 3          | 3.2.3   | Serielles Eingangsregister                                            | 5   |

| 3.3        | A]      | DC "AD7980" 1                                                         | 6   |

| л <b>У</b> | /HDI    | -Design 1                                                             | 7   |

|   | 4.1 | All    | gemeines                                  | 17 |

|---|-----|--------|-------------------------------------------|----|

|   | 4.2 | Die    | Komponente "startreset"                   | 19 |

|   | 4.3 | Die    | Komponente "avr_interface"                | 19 |

|   | 4.4 | Die    | Komponente "Zuweisung"                    | 20 |

|   | 4.  | 4.1    | Kommunikationsprotokoll                   | 20 |

|   | 4.  | 4.2    | Funktionsweise                            | 22 |

|   | 4.  | 4.3    | Simulation                                | 30 |

|   | 4.5 | Die    | Komponenten "Ansteuerung" & "AD5686"      | 34 |

|   | 4.6 | Die    | Komponente "AD5544"                       | 35 |

|   | 4.  | 6.1    | Funktionsweise                            | 35 |

|   | 4.  | 6.2    | Simulation                                | 40 |

|   | 4.7 | Die    | Komponente "AD7980"                       | 42 |

|   | 4.  | 7.1    | Funktionsweise                            | 42 |

|   | 4.  | 7.2    | Simulation                                | 50 |

|   | 4.8 | Die    | Komponente "Datensendung"                 | 54 |

|   | 4.  | 8.1    | Funktionsweise                            | 54 |

|   | 4.  | 8.2    | Simulation                                | 60 |

| 5 | Q'  | T-Anv  | wendung                                   | 61 |

|   | 5.1 | Erst   | tellung des GUIs                          | 61 |

|   | 5.2 | Die    | Klasse "communication_EvalBoard"          | 64 |

|   | 5.3 | Die    | Klasse "MojoSerial"                       | 69 |

|   | 5   | 3.1    | Allgemeines                               | 69 |

|   | 5   | 3.2    | Funktionen für das Feld "AD5686" des GUIs | 70 |

|   | 5   | 3.3    | Funktionen für das Feld "AD5544" des GUIs | 75 |

|   | 5   | 3.4    | Funktionen für das Feld "AD7980" des GUIs | 77 |

| 6 | Pr  | aktisc | he Durchführung                           | 82 |

| 7    | Zusammenfassung & Ausblick | 86 |

|------|----------------------------|----|

| Lite | raturverzeichnis           | 87 |

| Anh  | nang                       | 88 |

# Abbildungsverzeichnis

| Abbildung 1: Konzept zur Winkelmessung des POLDI Sensors [5]                  | 1  |

|-------------------------------------------------------------------------------|----|

| Abbildung 2: Kommunikation zwischen Computer und POLDI [4]                    | 2  |

| Abbildung 3: leeres GUI im QT-Creator                                         | 6  |

| Abbildung 4: Slots anzeigen im QT Creator                                     | 7  |

| Abbildung 5: Funktion einer hinzugefügten Aktion im QT Creator                | 7  |

| Abbildung 6: Benutzeroberfläche des Mojo Loaders                              | 8  |

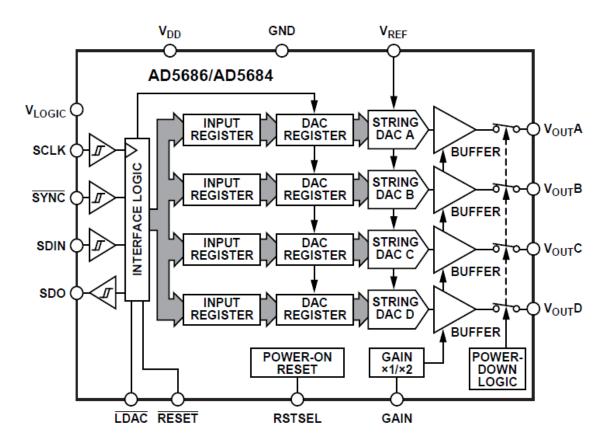

| Abbildung 7: funktionelles Blockdiagramm des DACs "AD5686" [2]                | 9  |

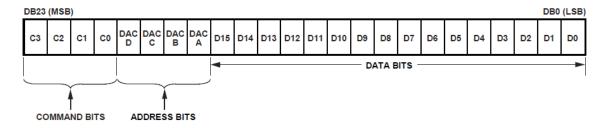

| Abbildung 8: Eingangsschieberegister des DACs "AD5686" [2]                    | 11 |

| Abbildung 9: Definitonen der Befehlsbits des DACs "AD5686" [2]                | 12 |

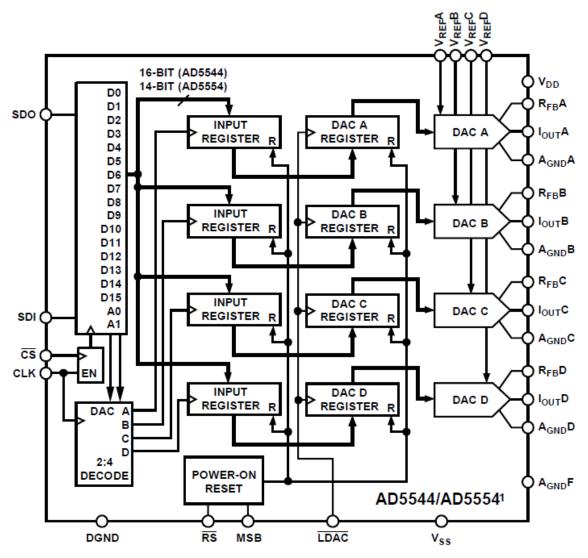

| Abbildung 10: funktionelles Blockdiagramm des DACs "AD5544" [1]               | 13 |

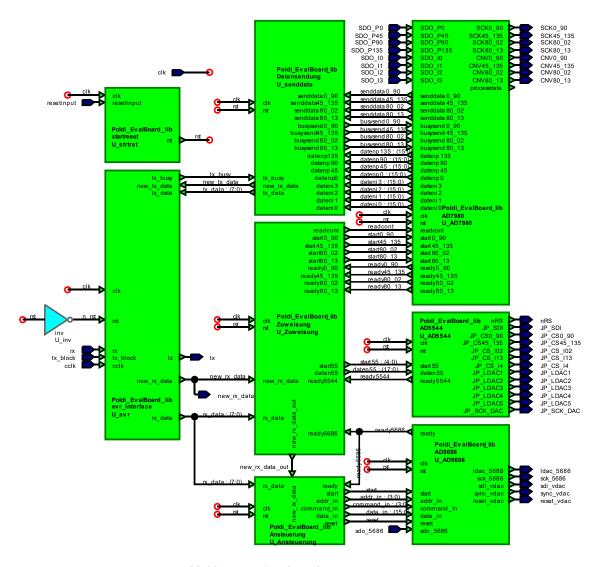

| Abbildung 11: Struktur des VHDL-Designs                                       | 17 |

| Abbildung 12: Struktur der Komponente "Zuweisung"                             | 22 |

| Abbildung 13: Zustandsmaschine "sm_Zuweisung"                                 | 24 |

| Abbildung 14: hierarchischer Zustand "sync" der Komponente "sm_Zuweisung"     | 25 |

| Abbildung 15: hierarchischer Zustand "AD5686" der Komponente "sm_Zuweisung"   | 26 |

| Abbildung 16: hierarchischer Zustand "readcont" der Komponente "sm_Zuweisung" | 27 |

| Abbildung 17: hierarchischer Zustand "AD5544" der Komponente "sm_Zuweisung"   | 29 |

| Abbildung 18: Simulation 1 der Komponente "Zuweisung"                         | 31 |

| Abbildung 19: Simulation 2 der Komponente "Zuweisung"                         | 31 |

| Abbildung 20: Simulation 3 der Komponente "Zuweisung"                         | 32 |

| Abbildung 21: Simulation 4 der Komponente "Zuweisung"                         | 33 |

| Abbildung 22: Struktur der Komponente "AD5544"                                | 35 |

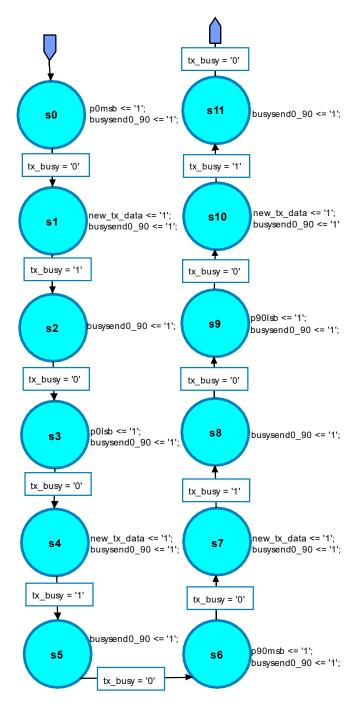

| Abbildung 23: Zustandsmaschine "sm_AD5544"                                    | 37 |

| Abbildung 24: hierarchischer Zustand "DAC1" der Komponente "sm AD5544"        | 38 |

| Abbildung 25: Zeitablaufdiagramm der Ansteuerung eines DACs vom Typ "AD5544" [1]        |

|-----------------------------------------------------------------------------------------|

| Abbildung 26: Simulation der Komponente "AD5544"                                        |

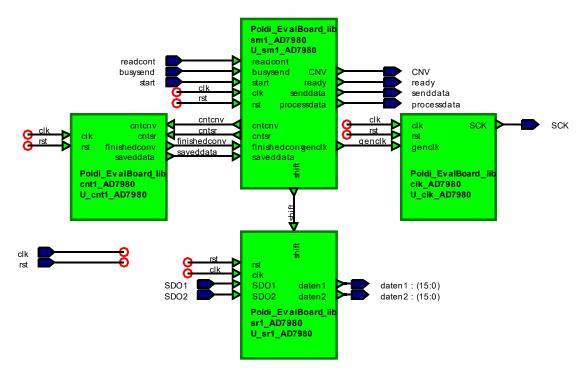

| Abbildung 27: Struktur der Komponente "AD7980"                                          |

| Abbildung 28: Struktur der Komponente "sm_AD7980"                                       |

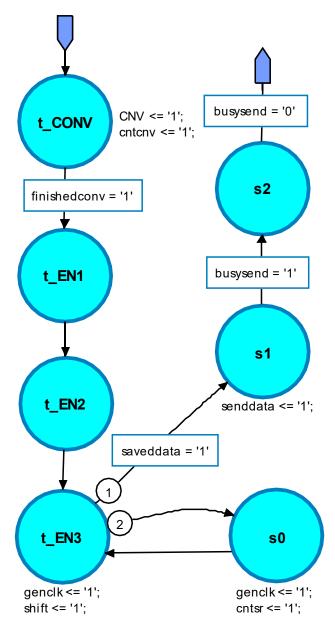

| Abbildung 29: Zustandsmaschine "sm1_AD7980"                                             |

| Abbildung 30: hierarchischer Zustand "readsend" der Komponente "sm1_AD7980" 46          |

| Abbildung 31: hierarchischer Zustand "readcont" der Komponente "sm1_AD7980" 48          |

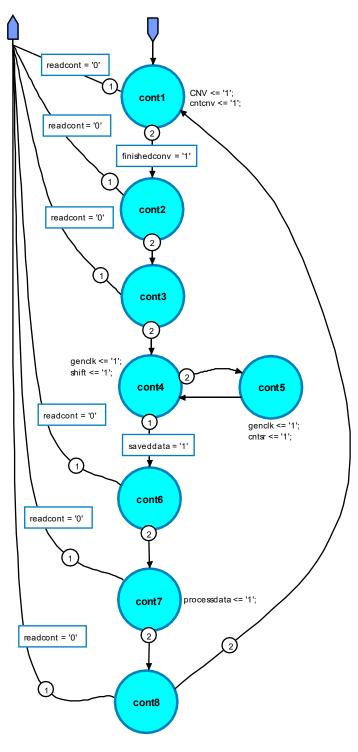

| Abbildung 32: Ablauf eines Auslesevorganges eines ADCs vom Typ "AD7980" [3] 50          |

| Abbildung 33: Simulation 1 der Komponente "AD7980"                                      |

| Abbildung 34: Simulation 2 der Komponente "AD7980"                                      |

| Abbildung 35: Struktur der Komponente "Datensendung"                                    |

| Abbildung 36: Zustandsmaschine "sm_Datensendung"                                        |

| Abbildung 37: hierarchischer Zustand "P0_P90" der Komponente "sm_Datensendung"          |

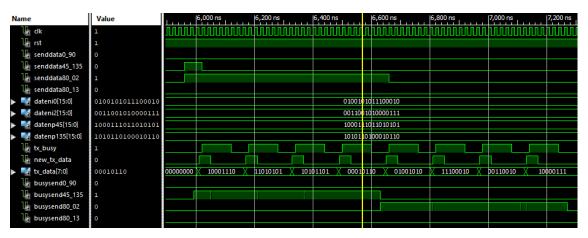

| Abbildung 38: Simulation der Komponente "Datensendung"                                  |

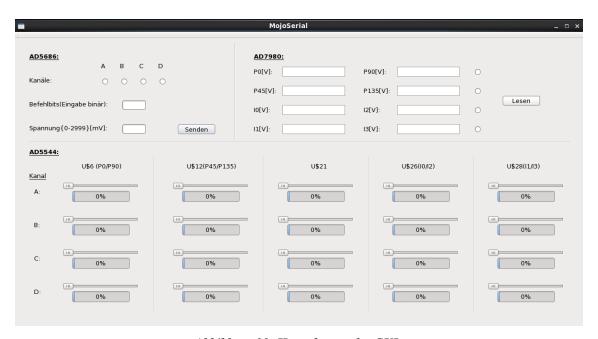

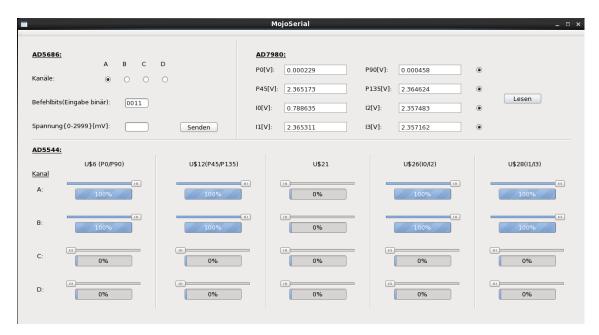

| Abbildung 39: Hauptfenster des GUIs                                                     |

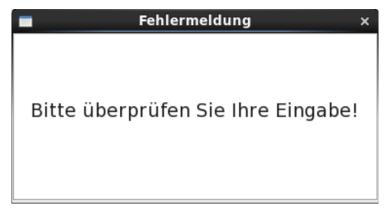

| Abbildung 40: Dialog "Fehlermeldung" des GUIs                                           |

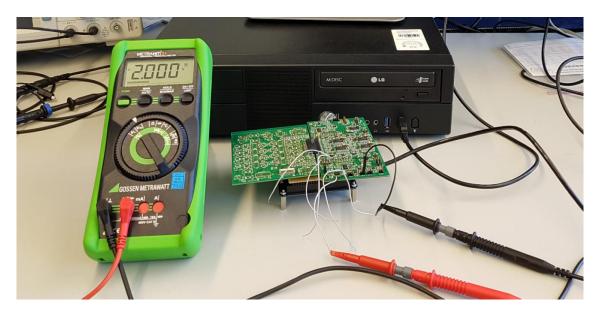

| Abbildung 41: Messung der Ausgangsspannung des DAC-Kanals "B" des DACs vom Typ "AD5686" |

| Abbildung 42: das Hauptfenster des GUIs bei einem Test                                  |

# **Tabellenverzeichnis**

| Tabelle 1: Eingangsschieberegister des DACs "AD5544" [1]                       | . 15 |

|--------------------------------------------------------------------------------|------|

| Tabelle 2: Definitionen der Adressbits des DACs "AD5544" [1]                   | . 15 |

| Tabelle 3: Format des Kommunikationsprotokolls                                 | . 20 |

| Tabelle 4: Kommunikationsprotokoll: Befehlscodes zur Auswahl der DACs          | . 20 |

| Tabelle 5: Kommunikationsprotokoll: Befehlscodes zur Auswahl der ADCs          | . 21 |

| Tabelle 6: Differenz der gesendeten und gemessenen Werte des DACs vom "AD5686" | • •  |

| Tabelle 7: alle Befehlscodes des Kommunikationsprotokolls                      | . 89 |

# Abkürzungsverzeichnis

**ADC** Analog Digital Converter

**CentOS** Community Enterprise Operating System

**DAC** Digital Analog Converter

**FPGA** Field Programmable Gate Array

GUI Graphical User Interface

LSB Least Significant Bit

MSB Most Significant Bit

**POLDI** POLarisierende Photo-DIoden

**USB** Universal Serial Bus

VHDL Very High Speed Integrated Circuit Hardware Description

Language

1 Einleitung 1

### 1 Einleitung

#### 1.1 Einführung in POLDI

Im Projekt POLarisierende Photo-DIoden (POLDI) soll ein berührungsloser Winkelsensor entwickeln werden, welcher mithilfe von polarisierter Lichtstrahlung einen Winkel mit einer Genauigkeit von mindestens 0,1° bestimmt. Winkelsensoren finden in vielen verschiedenen Anwendungen Gebrauch wie in der Automobilindustrie, in der Medizin oder in der Robotik. Durch die Integration von Sensor und Elektronik auf einem gemeinsamen Chip in CMOS-Technologie wird erreicht, dass der POLDI Winkelsensor energieeffizient, miniaturisiert und kostengünstig ist. [5]

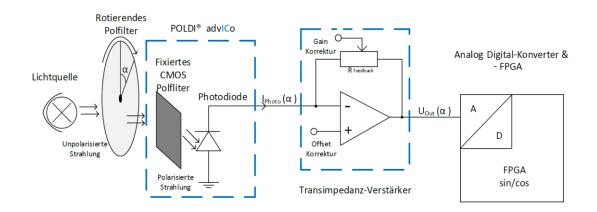

Abbildung 1: Konzept zur Winkelmessung des POLDI Sensors [5]

Abbildung 1 zeigt das Konzept zur Winkelmessung des POLDI Sensors. Durch parallele Leiterbahnen, welche sich auf der Oberfläche der Photodiode befinden, ist es möglich, integrierte Polarisationsfilter zu implementieren. Wird diese Kombination aus Photodiode und Polarisationsfilter mit linear polarisiertem Licht bestrahlt, so hängt die Intensität des auf die Dioden auftreffenden Lichtes vom Winkel der Lichtquelle ab. Der Photostrom der Dioden wird dann durch einen Transimpedanzverstärker in eine definierte Spannung gewandelt, welche an einem Analog Digital Converter (ADC) anliegt. [5]

Der POLDI Winkelsensor besteht aus vier solcher Photodioden, wobei die Polarisationsfilter der einzelnen Photodioden einen Winkel von jeweils 0°, 45°, 90° und 135° zueinander haben. Somit liefert jede Photodiode einen unterschiedlichen Photostrom. Jeder Photostrom fließt in einen separaten Transimpedanzverstärker. Die demnach unterschiedlich

1 Einleitung 2

definierten Spannungen liegen jeweils an separaten ADCs an und werden einem Field Programmable Gate Array (FPGA) zur Verfügung gestellt, welcher mit Algorithmen der digitalen Signalverarbeitung den Winkel des einfallenden Lichtes berechnen kann. [5]

#### 1.2 Kommunikation zwischen Computer und POLDI

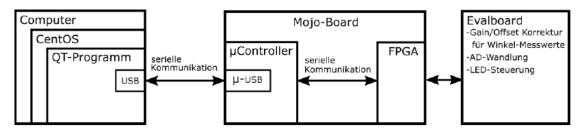

Die für die Auslesung nötigen Bauelemente wie ADCs und Digital Analog Converters (DACs) zur Einstellung der Referenzspannung der ADCs, die Gain- und Offsetkorrektur sowie weitere Elemente befinden sich auf einer Platine, welche Evalboard genannt wird. Auf dem sogenannten Mojoboard befinden sich wiederum der FPGA und ein Mikrocontroller, welcher den Datenaustausch zwischen dem FPGA und dem Computer verwaltet. Die Kommunikation des Mikrocontrollers mit dem Computer und mit dem FPGA erfolgt seriell. Für den Datenaustausch zwischen dem Computer und dem Mikrocontroller wird der Universal Serial Bus (USB)-Port des Computers mit der Micro-USB-Schnittstelle des Mikrocontrollers verbunden. Auf dem Computer wird unter der Linux-Distribution Community Enterprise Operating System (CentOS) die Entwicklungsumgebung QT-Creator verwendet, welche die Erstellung von C++-Programmen mit Graphical User Interfaces (GUIs) ermöglicht. Abbildung 2 zeigt schematisch den in diesem Kapitel beschriebenen Aufbau des Systems. [4]

Abbildung 2: Kommunikation zwischen Computer und POLDI [4]

#### 1.3 Ziel der Bachelorarbeit

Im Rahmen dieser Arbeit soll für das Projekt POLDI eine Ansteuerung aller sich auf dem Evalboard befindenden DACs und ADCs entworfen werden. Es befinden sich fünf DACs vom Typ "AD5544", ein DAC vom Typ "AD5686" und acht ADCs vom Typ "7980" auf dem Evalboard. Die Ansteuerung besteht aus einer QT-Anwendung und einem Very High Speed Integrated Circuit Hardware Desription Language (VHDL)-Design, welches auf dem FPGA des Mojoboards implementiert wird.

1 Einleitung 3

Die zu erstellende QT-Anwendung soll dem Anwender ermöglichen, über ein GUI die verschiedenen Kanäle der DACs einzustellen. Außerdem sollen verschiedene ADCs ausgewählt werden können, deren anliegende Spannungen bzw. die entsprechenden digitalen Ausgangssignale im GUI angezeigt werden. Die QT-Anwendung muss dafür die in einem Kommunikationsprotokoll des VHDL-Designs festgelegten Daten zur Synchronisation sowie dort festgelegte Daten zur Kennung des ausgewählten DACs bzw. der ausgewählten ADCs an den FPGA senden. Soll ein DAC angesteuert werden, muss zusätzlich die vom Anwender ausgewählte Einstellung des DACs in einen Binärcode umgewandelt und gesendet werden. Außerdem muss die QT-Anwendung die vom FPGA ausgelesenen Daten der ADCs empfangen, diese in Spannungen, die an den jeweiligen ADCs anliegen, umrechnen und im GUI anzeigen.

Das VHDL-Design soll das o.g. Kommunikationsprotokoll enthalten, welches mit den empfangenen Daten für eine Synchronisation sorgt und anhand der Daten die unterschiedlichen DACs und ADCs auswählt. Es sollen alle DACs angesteuert und alle ADCs ausgelesen werden können. Zur Auslesung der ADCs soll es zwei verschiedene Modi geben. In einem Modus soll es möglich sein, unterschiedlich viele ADCs auszulesen, die ausgelesenen Daten abzuspeichern und diese an den PC zu senden. Da die Winkelberechnung letztendlich auf dem FPGA stattfinden wird, soll es einen Modus geben, in dem alle ADCs kontinuierlich ausgelesen werden, ohne dass die ausgelesenen Daten an den PC gesendet werden.

#### 2 Software

#### 2.1 HDL Designer

"HDL Designer" ist eine Software zur Erstellung von HDL-Designs. Dabei können Module grafisch erzeugt und miteinander verbunden werden. Dadurch ist ein erstelltes Design deutlich übersichtlicher, als wenn es nur in Textform erstellt wird. Die Verschaltung von Modulen miteinander kann in dieser Software grafisch erfolgen. Die Software erstellt eine "vhd"-Datei, die die grafisch erzeugten Verbindungen der Module miteinander enthält.

Zudem lassen sich in dieser Software Zustandsmaschinen grafisch entwerfen. "HDL Designer" erzeugt aus den grafischen Zustandsmaschinen HDL-Code. Dabei kann ausgewählt werden, in welchen Zustand die Zustandsmaschine bei einem Reset übergehen soll, ob Zustände mit steigenden oder fallenden Taktflanken erreicht werden und wie viel Prozesse die Zustandsmaschine haben soll. Außerdem gibt es hierarchische Zustände, die wiederum Zustände enthalten, was die Übersicht verbessert.

In dieser Bachelorarbeit wurde die Software genutzt, um Komponenten miteinander zu verschalten und um Zustandsmaschinen grafisch zu erstellen. Alle Zustandsmaschinen sind 3-Prozess-Zustandsmaschinen und erreichen andere Zustände mit steigenden Taktflanken. Die Zustandsmaschinen wurden als Moore-Automaten entworfen. Die Ausgabe der Automaten hängt also nur von den Zuständen ab.

### 2.2 Xilinx ISE 14.7 Design Suite

Die Entwicklungsumgebung "Xilinx ISE" ermöglicht mithilfe von Hardwarebeschreibungssprachen wie VHDL oder Verilog, digitale Schaltungen zu entwerfen und auf Xilinx FPGAs zu implementieren. Außerdem ist es möglich, entworfene Designs zu simulieren und die Schaltbilder der Designs anzeigen zu lassen. Im Rahmen der Bachelorarbeit wurde "Xilinx ISE" genutzt, um Simulationen durchzuführen und eine "bin"-Datei des VHDL-Designs für die FPGA Konfiguration zu generieren.

Nachdem ein Projekt geöffnet wurde, können unten links die Schaltflächen "Start", "Design", "Files" und "Libraries" angeklickt werden. Unter "Files" lassen sich die Quelltexte

der einzelnen Dateien öffnen und bearbeiten. Unter Designs lässt sich oben zwischen "Implementation" und "Simulation" wechseln. Wenn "Implementation" ausgewählt wurde, kann das ausgewählte Modul mit einem Doppelklick auf "Synthesize - XST" synthetisiert und mit einem Doppelklick auf "Implement Design" implementiert werden. Um das Schaltbild eines Moduls anzeigen zu lassen, muss erst eine Synthese stattfinden. Das Schaltbild kann eingesehen werden, indem auf das kleine "+"-Zeichen neben "Synthesize - XST" geklickt wird und "View RTL Schematic" mit einem Doppelklick ausgewählt wird. Wenn zu "Simulation" gewechselt wird, kann dort oben links "Behavioral" oder "Post-Route" ausgewählt werden und eine Behavioral oder Timing Simulation gestartet werden.

### 2.3 QT-Creator

Die Entwicklungsumgebung QT-Creator ermöglicht die Erstellung von C++-Programmen mit GUIs. In dieser Arbeit wird die Entwicklungsumgebung genutzt, um eine Anwendung zu entwerfen, welche die grafische Eingabe von Daten und die Versendung dieser Daten an den FPGA erlaubt.

Zur Erstellung eines neuen Projektes wird nach dem Start des QT-Creators die Option "neues Projekt" angeklickt. Es öffnet sich ein Fenster, in welchem ausgewählt werden muss, was für ein Projekt erstellt werden soll. Da in dieser Bachelorarbeit eine Anwendung mit einem GUI erzeugt werden soll, wird unter "Projekte" -> "Anwendung" -> "Qt-Widgets-Anwendung" ausgewählt. Durch einen Klick auf "Auswählen" erscheint eine neue Maske, in welcher ein Projektname und Speicherort festgelegt wird. Nachdem auf "Weiter" geklickt wird, erscheint die Kit-Auswahl, in welcher schon das richtige Kit ausgewählt ist. Es wird wieder "Weiter" angeklickt. Die nächsten Masken "Details" und "Zusammenfassung" können ohne Änderungen mit einem Klick auf "Weiter" bzw. "abschließen" übersprungen werden.

Oben links ist nun ein Ordnersymbol mit dem entsprechenden Namen des Projektes zu sehen. Dieser Ordner kann mit einem Klick auf den kleinen Pfeil ausgeklappt werden, sodass die "pro"-Datei sowie die Unterordner "Header-Dateien", "Quelldateien" und "Formulardateien" erscheinen, welche weiter ausgeklappt werden können. Unter den einzelnen Ordnern erscheinen die zugehörigen Dateien, welche sich mit einem Doppelklick öffnen und bearbeiten lassen. Das Hinzufügen einer neuen Header-, Quell- oder

Formulardatei geschieht mit einem Rechtsklick auf ein Ordnersymbol oben links und das Anklicken von "Hinzufügen". Es öffnet sich ein neues Fenster, in welchem sich verschiedene Dateien und Klassen auswählen lassen.

Mit einem Doppelklick auf die Datei unter dem Ordner "Formulardateien" erscheint das GUI, welches sich mit vorgegebenen Objekten gestalten lässt. Um zurück zu den Ordnersymbolen zu gelangen, muss am linken grauen Rand "Editieren" angeklickt werden.

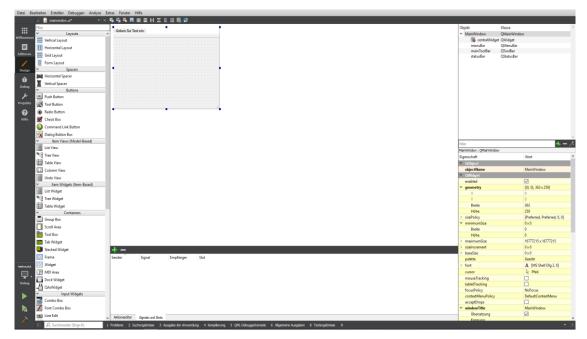

Abbildung 3: leeres GUI im QT-Creator

Auf der linken Seite im weißen Feld in Abbildung 3 gibt es verschiedene Objekte, die per Drag & Drop auf dem GUI, welches sich mittig befindet, platziert werden können. Beispielsweise sind verschiedene Buttons, Eingabefelder und Anzeigeobjekte verfügbar. Oben rechts befindet sich eine Übersicht mit allen Objekten. Das GUI und alle hinzugefügten Elemente lassen sich in ihren Eigenschaften verändern. Möglich ist dies auf der rechten Seite unter der Übersicht der Objekte unter "Eigenschaften". Um die Eigenschaften eines Objektes zu verändern, muss dieses entweder im GUI oder in der Übersicht der Objekte angeklickt werden. Im GUI direkt lassen sich z. B. auch die Größe, der Name oder die Position verändern.

Per Rechtsklick auf ein Objekt -> "Slots anzeigen" lassen sich den Objekten verschiedene Aktionen hinzufügen, welche Signale auslösen. Nach dem Hinzufügen einer Aktion öffnet sich die Quelldatei mit dem Projektnamen und der Endung "cpp", in welcher automatisch ein Quelltext mit einer der Aktion entsprechenden Funktion generiert wurde. In

diesen Rahmen kann dann der Programmcode eingefügt werden, der ausgeführt wird, wenn die Aktion im GUI ausgelöst wird. Die folgenden zwei Abbildungen zeigen dies exemplarisch für einen "Radio Button" und die Aktion "clicked()".

Abbildung 5: Funktion einer hinzugefügten Aktion im QT Creator

Um ein aktuelles Projekt auszuführen, muss am linken grauen Rand der Benutzeroberfläche unten auf den oberen grünen Pfeil geklickt werden. Um eine Anwendung zu erstellen, muss auf das Hammersymbol zwei Symbole unter dem grünen Pfeil geklickt werden.

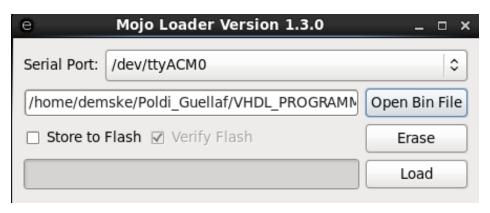

#### 2.4 Mojo Loader

Um mit dem implementierten Design den FPGA zu konfigurieren, wird der Mojo Loader benötigt. Die mit ISE 14.7 erzeugte "bin"-Datei des VHDL-Designs wird mit dem Mojo Loader auf das Mojoboard übertragen. Nachdem das Programm gestartet wurde, muss eine serielle Schnittstelle ausgewählt werden. Dafür muss auf das Feld neben "Serial Port:" geklickt werden. Durch einmalige Selektion per Mausklick wird die richtige serielle Schnittstelle gefunden, wenn das Mojoboard mit dem Computer verbunden ist. Soll die "bin"-Datei nicht im Flash-Speicher des Boards gespeichert werden, muss der Haken bei "Store to Flash" entfernt werden. Mit einem Klick auf "Open Bin File" kann die gewünschte "bin"-Datei ausgewählt werden. Die Übertragung beginnt mit einem Klick auf "Load". Abbildung 6 zeigt die Benutzeroberfläche des Mojo Loaders mit einer ausgewählten seriellen Schnittstelle und ausgewählten "bin"-Datei.

Abbildung 6: Benutzeroberfläche des Mojo Loaders

#### 3 DACs und ADCs

#### 3.1 DAC "AD5686"

#### 3.1.1 Funktionsweise

Der DAC "AD5686" besitzt vier verschiedene Kanäle und funktioniert mit einer Versorgungsspannung von 2,7 V bis 5,5 V. Er gibt eine gepufferte Spannung mit einer 16-Bit Auflösung aus. [2]

Abbildung 7: funktionelles Blockdiagramm des DACs "AD5686" [2]

In Abbildung 7 sind die vier verschiedenen Kanäle des DACs zu erkennen. Ist der "GAIN"-Pin am "GND"-Pin angeschlossen, entspricht die maximale Ausgangsspannung aller DAC-Kanäle der Versorgungsspannung. Wenn der "GAIN"-Pin mit dem "VLO-GIC"-Pin verbunden ist, entspricht die maximale Ausgangsspannung der doppelten Versorgungsspannung. Der "RSTSEL"-Pin ermöglicht, die Ausgangsspannung der DAC-Kanäle direkt nach dem Einschalten des DACs auf 0 V oder auf die halbe Versorgungsspannung einzustellen. Soll die Ausgangsspannung 0 V betragen, muss der "RST-SEL"-Pin mit dem "GND"-Pin verbunden werden, für die halbe Versorgungsspannung

muss der "RSTSEL"-Pin mit dem " $V_{LOGIC}$ "-Pin verbunden werden. In diesem Projekt ist der "GAIN"-Pin mit dem "GND"-Pin und der "RSTSEL"-Pin mit dem " $V_{LOGIC}$ "-Pin verbunden. [2]

Daten werden über eine serielle 3-Draht-Schnittstelle, bestehend aus "SDIN", "SCLK" und "SYNC", in einem 24-Bit-Wortformat in den DAC geschrieben. Die serielle Schnittstelle arbeitet mit Taktraten von bis zu 50 MHz. Die Daten werden in die für die einzelnen Kanäle zuständigen Eingangsschieberegister geschrieben, von welchen sie in DAC-Register weitergeleitet werden. Von dort aus werden sie in Strings (Widerstandsketten) geschrieben. Die geschriebenen Daten bestimmen darüber, von welchem Knoten des Strings die Spannung abgegriffen wird, sodass unterschiedliche Spannungen generiert werden können. Die abgegriffene Spannung wird einem Verstärker zugeführt. Das Ausgangssignal des Verstärkers liegt dann am Ausgang des DACs an. [2]

## 3.1.2 Funktionsbeschreibung der für die FPGA-Ansteuerung relevanten Pins

**SCLK** ist der serielle Eingang für den Takt. Daten werden mit fallenden Flanken des Taktes übernommen. Daten können mit einer Frequenz von bis zu 50 MHz übertragen werden. [2]

**SDIN** ist der Eingang des 24-Bit-Eingangsschieberegisters und bietet die Möglichkeit, seriell Daten mit fallenden Flanken von "SLCK" in das Empfangsschieberegister zu schreiben. [2]

**SYNC** ist ein Synchronisationssignal für Eingangsdaten. Bei einem Low-Pegel des Signals "SYNC" werden Daten auf dem "SDIN" Bus mit den nächsten 24 fallenden Flanken von "SLCK" empfangen. [2]

**SDO** kann genutzt werden, um mehrere AD5686- oder AD5684-DACs in Reihe zu schalten oder um die eingelesenen Daten seriell zurück zu lesen, wobei sie mit der steigenden Flanke von "SCLK" übertragen werden und bei der fallenden Flanke des Taktes gültig sind. [2]

**LDAC** kann synchron oder asynchron verwendet werden. Bei einem anliegenden Low-Pegel aktualisieren sich die DAC-Register, deren Eingangsregister neue Daten erhalten haben. "LDAC" kann auch dauerhaft low gehalten werden. [2]

**RESET** reagiert auf Pegel des am "RESET"-Pin anliegenden Signals und ist asynchron zum Takt. Wenn ein Low-Pegel erkannt wird, wird das Eingangs- und das DAC-Register auf null oder auf den halben Wert gehalten, je nach Verbindung des "GAIN"-Pins (siehe Kapitel 3.1.1). Wenn "RESET" low gehalten wird, werden alle "LDAC" -Impulse ignoriert. [2]

#### 3.1.3 Inhalt des 24-Bit-Eingangsschieberegisters

Abbildung 8: Eingangsschieberegister des DACs "AD5686" [2]

Das Eingangsschieberegister, in welches seriell Daten geschrieben werden, füllt seine 24 Bits (DB23 bis D0) beginnend vom Most Significant Bit (MSB) in absteigender Reihenfolge bis hin zum Least Significant Bit (LSB). Wenn der Pin SYNC low wird, werden mit den nächsten 24 fallenden Flanken des Takteingangs Daten in das Eingangsschieberegister geschrieben und mit der ansteigenden Flanke von SYNC aktualisiert. [2]

Die ersten vier Bits sind Befehlsbits (C3, C2, C1, C0) zur Ausführung unterschiedlicher Befehle, die nachfolgenden vier (DAC D, DAC C, DAC B, DAC A) bilden eine Adresse und ermöglichen die Ansteuerung eines oder mehrerer DAC-Kanäle. Die letzten 16 Bits sind Daten (D15 bis D0), welche die Ausgangsspannung bestimmen. [2]

| Command Bits |    | ts         |    |                                                            |  |

|--------------|----|------------|----|------------------------------------------------------------|--|

| <b>C3</b>    | C2 | <b>C</b> 1 | CO | Description                                                |  |

| 0            | 0  | 0          | 0  | No operation                                               |  |

| 0            | 0  | 0          | 1  | Write to Input Register n (dependent on LDAC)              |  |

| 0            | 0  | 1          | 0  | Update DAC Register n with contents of Input<br>Register n |  |

| 0            | 0  | 1          | 1  | Write to and update DAC Channel n                          |  |

| 0            | 1  | 0          | 0  | Power down/power up DAC                                    |  |

| 0            | 1  | 0          | 1  | Hardware LDAC mask register                                |  |

| 0            | 1  | 1          | 0  | Software reset (power-on reset)                            |  |

| 0            | 1  | 1          | 1  | Reserved                                                   |  |

| 1            | 0  | 0          | 0  | Set up DCEN register (daisy-chain enable)                  |  |

| 1            | 0  | 0          | 1  | Set up readback register (readback enable)                 |  |

| 1            | 0  | 1          | 0  | Reserved                                                   |  |

|              |    |            |    | Reserved                                                   |  |

| 1            | 1  | 1          | 1  | No operation, daisy-chain mode                             |  |

Abbildung 9: Definitonen der Befehlsbits des DACs "AD5686" [2]

Abbildung 9 zeigt verschiedene Kombinationen der Befehlsbits und die dazugehörige Beschreibung. Im Rahmen der Bachelorarbeit sollen die Daten für einen oder mehrere DAC-Kanäle übertragen und direkt aktualisiert werden, weshalb die Kombination "0011" genutzt wird.

Zur Ansteuerung eines einzelnen DAC-Kanals muss das dazugehörige Adressbit den Wert eins und die anderen Adressbits den Wert null annehmen. Es ist auch möglich, mehrere Kanäle anzusteuern. Dafür müssen die Adressbits der gewünschten Kanäle logisch eins und die anderen Adressbits bzw. das andere Adressbit logisch null sein. Wenn alle Kanäle angesteuert werden sollen, müssen alle Adressbits den Wert eins haben. [2]

Die folgende Übertragungsfunktion des DACs zeigt, wie die 16 Datenbits die Ausgangsspannung V<sub>OUT</sub> beeinflussen. [2]

$$V_{OUT} = V_{REF} * Gain\left[\frac{D}{2^N}\right]$$

[2]

V<sub>REF</sub> steht dabei für die Versorgungs- bzw. Referenzspannung, Gain für den Verstärkungsfaktor, welcher in diesem Projekt den Wert eins besitzt. N ist die Auflösung des DACs, also in diesem Fall 16, und D das dezimale Äquivalent der 16 Datenbits. Eine Ausgangspannung von 0 V ergibt sich, wenn alle Datenbits den Wert null haben. Das dezimale Äquivalent nimmt dann auch den Wert 0 an und somit ergibt die ganze

Gleichung null. Haben alle Datenbits den Wert eins, ist das dezimale Äquivalent und somit auch die Ausgangsspannung am größten. Laut der Formel entspricht dieser Wert nahezu der Referenzspannung. [2]

#### 3.2 DAC "AD5544"

#### 3.2.1 Funktionsweise

Der DAC "AD5544" besitzt vier verschiedene Kanäle und funktioniert mit einer Versorgungsspannung von 2,7 V bis 5,5 V. Er gibt Ströme mit einer 16-Bit Auflösung aus, wobei die einzelnen Ausgangsströme maximal 2,5 mA groß sein können. [1]

Abbildung 10: funktionelles Blockdiagramm des DACs "AD5544" [1]

Abbildung 10 zeigt das funktionelle Blockdiagramm des DACs. Wie oben rechts zu erkennen ist, hat jeder Kanal einen eigenen Pin für die Referenzspannung. Die

Referenzspannung eines Kanals bestimmt den Bereich, den der Ausgangsstrom des Kanals annehmen kann. Der unten mittig zu sehende Block "Power-On Reset" sorgt dafür, dass die Ausgangsströme nach dem Einschalten entweder 0 A oder der Hälfte des maximalen Ausgangsstromes entsprechen. Wenn am "MSB"-Pin ein Signal mit einem High-Pegel anliegt, nimmt der Wert den halben maximalen Ausgangsstrom an. Wenn dort ein Low-Signal anliegt, beträgt der Wert 0 A. In diesem Projekt liegt am "MSB"-Pin ein Low-Signal an. [1]

Daten werden über eine doppelt gepufferte serielle 3-Draht-Schnittstelle, bestehend aus "SDI", "CLK" und "CS", in das Eingangsschieberegister geschrieben. Vom Eingangsschieberegister werden die Daten in das Eingangsregister eines Kanals geschrieben, wobei ein 2-4-Dekodierer mithilfe der Adressbits erkennt, welches Eingangsregister der vier Kanäle ausgewählt wurde. Von den Eingangsregistern werden die Daten in DAC-Register weitergeleitet. Die empfangenen Daten bestimmen über die Verschaltung eines Widerstandsnetzwerkes und somit über die Größe des Ausgangsstromes. [1]

### 3.2.2 Funktionsbeschreibung der für die FPGA-Ansteuerung relevanten Pins

RS sorgt bei anliegendem Low-Signal dafür, dass alle Eingangs- und DAC-Register je nach anliegender Spannung am MSB-Pin auf null oder auf die Hälfte des Maximalwertes gesetzt werden. Die Register werden auf null gesetzt, wenn an "MSB" ein Low-Signal anliegt und auf die Hälfte des Maximalwertes, wenn dort ein High-Signal anliegt. [1]

CS deaktiviert die Datenübertragung in das Schieberegister, wenn an diesem Pin ein Signal mit einem High-Pegel anliegt. Bei einer steigenden Flanke von "CS/LDAC" werden die letzten 18 Bits, die in das Schieberegister geschrieben worden sind, in das Eingangsregister übertragen. [1]

**CLK** ist der Takteingang. Die Taktfrequenz kann bis zu 20 MHz betragen. [1]

**SDI** ist der Eingang des Schieberegisters. Mit den steigenden Flanken von "CLK" werden die am "SDI"-Pin anliegenden Daten seriell in das Schieberegister geschrieben. [1]

**SDO** ermöglicht, die Daten des Schieberegisters auszulesen. Die Daten erscheinen 19 Takte nachdem sie am "SDI"-Pin eingelesen worden sind. [1]

**LDAC** überträgt die Daten der Eingangsregister in die DAC-Register, wenn an diesem Pin ein Signal mit einem Low-Pegel anliegt. [1]

#### 3.2.3 Serielles Eingangsregister

Tabelle 1: Eingangsschieberegister des DACs "AD5544" [1]

| MSB |     |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    | LSB |

|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|-----|

| B17 | B16 | B15 | B14 | B13 | B12 | B11 | B10 | В9 | В8 | В7 | B6 | В5 | B4 | В3 | B2 | B1 | В0  |

| A1  | A0  | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0  |

In Tabelle 1 ist der Inhalt des 18-Bit-Schieberegisters des DACs zu sehen. Daten werden seriell in das Schieberegister geschrieben, wobei die 18 Bits vom MSB bis hin zum LSB in absteigender Reihenfolge gefüllt werden. Die ersten zwei Bits sind Adressbits (A1, A0) und ermöglichen, einen der vier Kanäle anzusteuern. Tabelle 2 zeigt, mit welchen Bitkombinationen die unterschiedlichen Kanäle angesteuert werden können. [1]

Tabelle 2: Definitionen der Adressbits des DACs "AD5544" [1]

| A1 | A0 | Kanal |

|----|----|-------|

| 0  | 0  | A     |

| 0  | 1  | В     |

| 1  | 0  | С     |

| 1  | 1  | D     |

Die letzten 16 Bits sind Datenbits und legen die Größe des Ausgangsstromes fest. Dabei ist "D15" das MSB und "D0" das LSB. Umso größer der Wert der Datenbits ist, desto größer ist der Betrag des Ausgangsstromes. [1]

#### 3.3 ADC "AD7980"

Der ADC vom Typ "AD7980" hat eine 16 Bit Auflösung. Er wandelt die Differenz der an den "V+" und "V-"-Pins anliegenden Spannungen in Bezug auf die am "REF"-Pin anliegende Referenzspannung in einen Digitalwert um. [3]

Mit der folgenden Funktion lässt sich die Differenz der an den "V+" und "V-"-Pins anliegenden Spannungen berechnen. [3]

$$V_{IN} = V_{REF} * \frac{D}{2^N}$$

[3]

V<sub>IN</sub> steht dabei für die Differenz der an den "V+" und "V-"-Pins anliegenden Spannungen. V<sub>REF</sub> steht für die Referenzspannung, welche in diesem Projekt 3 V beträgt. N ist die Auflösung des ADCs, also in diesem Fall 16, und D das dezimale Äquivalent der 16 Bits, die mit einem Auslesevorgang erhalten werden. [3]

Die folgenden Pins sind relevant für die FPGA-Ansteuerung:

Mithilfe des **SDI**-Pins können verschiedene Modi ausgewählt werden. In diesem Projekt ist das an diesem Pin anliegende Signal immer high, sodass der  $\overline{\text{CS}}$ -Modus ausgewählt ist. [3]

CNV sorgt dafür, dass die anliegende Spannung in einen Digitalwert umgewandelt wird, wenn das an diesem Pin anliegende Signal high wird. Zudem wird erkannt, dass der CS-Modus ausgewählt ist. Dadurch wird der SDO-Pin freigegeben. [3]

**SDO** ist der Pin, an dem das Umwandlungsergebnis seriell erscheint. Dabei werden die Bits mit den fallenden Taktflanken gesetzt und sollten somit mit den steigenden Taktflanken abgespeichert werden. [3]

**SCK** ist der Takteingang. [3]

## 4 VHDL-Design

#### 4.1 Allgemeines

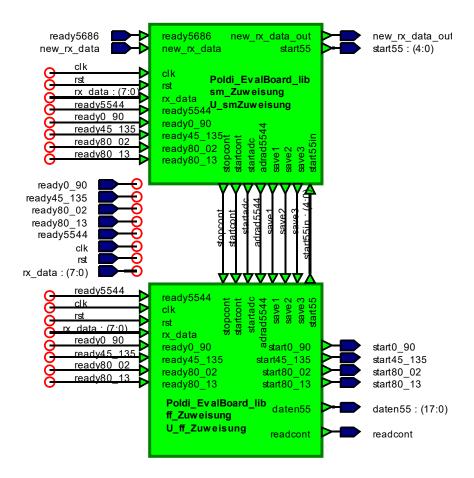

Das VHDL-Design besteht aus acht Hauptkomponenten, die miteinander verschaltet sind. Jede Komponente des VHDL-Designs enthält einen asynchronen Reset. Die Zustandsmaschinen gehen bei einem Reset in ihre Anfangszustände über.

Abbildung 11 zeigt die Verschaltung der einzelnen Hauptkomponenten miteinander.

Abbildung 11: Struktur des VHDL-Designs

Die in Abbildung 11 zu sehenden Eingangs- und Ausgangsports wurden in der Datei "mojo.ucf" Pins des Mojoboards zugewiesen, wobei der Port "clk" dem 50 MHz-Systemtakt des Mojoboards zugewiesen wurde. Die Ports der rechten drei Komponenten

wurden Pins, die mit den DACs und ADCs verbunden sind, zugewiesen. Dabei heißen diese Ports genauso wie die Pins der DACs und ADCs in den Dateien des Projektes "POLDI". Auf den Port "resetinput" sowie auf die Ports, die mit der Komponente "avr\_interface" verbunden sind, wird in Kapitel 4.3 und in Kapitel 4.2 eingegangen.

Im Folgenden wird kurz erklärt, welche Hauptfunktionen die einzelnen Hauptkomponenten haben. Die Funktionsweise dieser Komponenten werden in den nachfolgenden Kapiteln der jeweiligen Komponenten detailliert erklärt.

- "startreset" sorgt dafür, dass die restlichen Komponenten nach einer Konfiguration des FPGAs zurückgesetzt werden.

- "avr\_interface" wird vom Hersteller des Mojoboards zur Verfügung gestellt und verwaltet die Kommunikation zwischen dem Mikrocontroller und dem FPGA.

- "Zuweisung" enthält ein Kommunikationsprotokoll und empfängt die Daten von "avr\_interface". Es sorgt für eine Synchronisation zwischen der Applikationssoftware und der FPGA Logik und übergibt den für die Ansteuerung der DACs und ADCs zuständigen Komponenten Steuersignale und Daten.

- "Ansteuerung" und "AD5686" sind für die Ansteuerung des DACs vom Typ "AD5686" zuständig.

- "AD5544" steuert die fünf verschiedenen DACs vom Typ "AD5544" an.

- "AD7980" liest die acht verschiedenen ADCs aus und speichert die ausgelesenen Daten ab.

- Mit "Datensendung" können die von "AD7980" gespeicherten Daten an die Komponente "avr\_interface" übergeben werden, welche die Daten mithilfe des Mikrocontrollers an den PC sendet.

Erklärungen der einzelnen Ein- und Ausgangssignale der Komponenten sind in den Kapiteln der jeweiligen Komponenten zu finden. Da fast alle Komponenten die Eingangssignale "clk" und "rst" haben, werden diese zur Vereinfachung einmalig erklärt:

- "clk" ist der Systemtakt und beträgt 50MHz.

- "rst" wird von der Komponente "startreset" erzeugt. Es leitet das Signal der Resettaste des Mojoboards an die anderen Komponenten weiter und sorgt nach Implementierung des VHDL-Designs auf dem FPGA dafür, dass die anderen Komponenten zurückgesetzt werden.

### 4.2 Die Komponente "startreset"

Das Eingangssignal "resetinput" dieser Komponente ist mit dem Port "resetinput" verbunden (siehe Abbildung 11). Dieser Port wurde der Resettaste des Mojoboards zugewiesen. Diese Komponente hat die Aufgabe, nach einer Konfiguration des FPGAs alle Komponenten des FPGAs zurückzusetzen. Zusätzlich leitet sie das Signal der Resettaste des Mojoboards weiter an die anderen Komponenten. Dazu nutzen alle anderen Komponenten das Ausgangssignal "rst" dieser Komponente als Reseteingang. Die anderen Komponenten werden zurückgesetzt, wenn "rst" gleich null ist. Das Ausgangssignal "rst" wird von dieser Komponente nach 50.000 Takten nach einer Konfiguration des FPGAs für 100 Takte gleich null gesetzt, sodass alle anderen Komponenten zurückgesetzt werden.

### 4.3 Die Komponente "avr\_interface"

Die Komponente "avr\_interface" wird vom Hersteller des Mojoboards zur Verfügung gestellt und verwaltet die serielle Kommunikation zwischen dem Mikrocontroller und dem FPGA. Die Ports in Abbildung 11, die mit den Ein- und Ausgängen der Komponente "avr\_interface" verbunden sind, entsprechen den Pins des Mojoboards, die mit dem Mikrocontroller verbunden sind. Dies ist notwendig, damit die Kommunikation zwischen dem Mikrocontroller und dem FPGA stattfinden kann. [4]

Die Komponente ist ein Top-Modul und fügt die Module "cclk\_detector", "spi\_slave", "serial\_rx" und "serial\_tx" zusammen und ergänzt sie um einige Eigenschaften, wobei "cclk\_detector" dafür sorgt, dass der FPGA erst nach seiner Konfiguration die serielle Schnittstelle zur Kommunikation nutzen kann. Daten können über die serielle Schnittstelle mithilfe von "serial\_rx" empfangen und mithilfe von "serial\_tx" versendet werden. Bei dem Modul "spi\_slave" handelt es sich um eine SPI-Schnittstelle [4], welche in diesem Projekt jedoch nicht verwendet und deswegen entfernt wurde.

Zudem wurde das Top-Modul "avr\_interface" so bearbeitet, dass nichts mehr enthalten ist, was für die Steuerung des Moduls "spi slave" zuständig ist.

Die für die serielle Kommunikation relevanten Ein- und Ausgangssignale, die nicht mit Ports verbunden sind, haben folgende Bedeutungen:

- "new\_rx\_data" ist gleich eins, wenn neue Daten empfangen werden, die der 8-Bit-Vektor "rx\_data" enthält. [4]

- "tx\_busy" zeigt an, ob Daten an den Mikrocontroller gesendet werden können.[4]

- "new\_tx\_data" muss gleich eins gesetzt werden, wenn "tx\_busy" gleich null ist und Daten gesendet werden sollen. Die zu sendenden Daten werden dem Modul über den 8-Bit-Vektor "tx\_data" übergeben. Wenn "tx\_busy" gleich eins ist, sollte das Signal "new tx data" wieder gleich null gesetzt werden. [4]

#### 4.4 Die Komponente "Zuweisung"

#### 4.4.1 Kommunikationsprotokoll

Tabelle 3: Format des Kommunikationsprotokolls

| Synch    | Synch    | Synch    | Synch    | Befehlscode | Daten    | Daten    | Daten    |

|----------|----------|----------|----------|-------------|----------|----------|----------|

| (8 Bits)    | (8 Bits) | (8 Bits) | (8 Bits) |

Tabelle 3 zeigt das Format des in dieser Komponente enthaltenen Kommunikationsprotokolls. Die Daten der Komponente "avr\_interface" werden byteweise empfangen. Zur Synchronisation müssen nacheinander vier Bytes empfangen werden, welche nur Einsen enthalten. Falls dies der Fall ist, entspricht das nächste empfangene Byte einem Befehlscode, der entscheidet, welcher DAC konfiguriert wird bzw. welche ADCs ausgelesen werden und was mit den ausgelesenen Daten passiert. Tabelle 4 zeigt, welcher DAC mit welchem Befehlscode ausgewählt wird, wobei die Bezeichnungen in der Tabelle den Bezeichnungen der Schaltpläne des Projektes POLDI entsprechen.

Tabelle 4: Kommunikationsprotokoll: Befehlscodes zur Auswahl der DACs

| Befehlscode | ausgewählter DAC | einstellbare Signale      |

|-------------|------------------|---------------------------|

| 00000000    | U\$6 (AD5544)    | SIN0, SIN90               |

| 0000001     | U\$12 (AD5544)   | SIN45, SIN135             |

| 00000010    | U\$26 (AD5544)   | VOH0, VOH2                |

| 00000011    | U\$28 (AD5544)   | VOH1, VOH3                |

| 00000100    | U\$21 (AD5544)   | V_FREE, REF_INTENSITY     |

| 00000101    | U\$7 (AD5686)    | SHIELD, VT_INTEN, VT_POLA |

Wird nach einer erfolgreichen Synchronisation mit dem nächsten Byte ein DAC ausgewählt, sind die nächsten drei Bytes für das Eingangsschieberegister des ausgewählten DACs bestimmt. Bei einer Auswahl eines DACs vom Typ "AD5544" werden vom ersten Byte allerdings nur die zwei LSBs berücksichtigt, da diese DACs kein 24-Bit großes, sondern ein 18-Bit großes Eingangsschieberegister enthalten (siehe Kapitel 3.2.3).

Da die auf dem Evalboard vorhandenen ADCs immer paarweise mit einem SPI Bus verbunden sind, erlaubt die entworfene Logik die zeitgleiche Auslesung von entweder zwei, vier, sechs oder acht ADCs, wobei die ausgelesenen Daten anschließend an den PC gesendet werden. Alternativ kann die kontinuierliche Auslesung aller ADCs gestartet bzw. anschließend wieder gestoppt werden. Die kontinuierliche Auslesung kann nach einer Synchronisation mit dem Byte "10000111" gestartet und mit "00000111" wieder gestoppt werden.

Falls ADCs ausgelesen und die ausgelesenen Daten anschließend an den PC gesendet werden sollen, müssen nach einer Synchronisation die vier LSBs des nächsten Bytes gleich "0110" sein. Mit den vier MSBs dieses Bytes wird eine Auswahl der ADCs getroffen. Mit Variation der vier MSBs des Bytes können unterschiedliche ADCs ausgelesen werden, deren Daten anschließend an den PC gesendet werden. Mit einem Bit der vier MSBs werden zwei ADCs ausgewählt. Tabelle 5 zeigt Variationen des Befehlscodes, aus denen hervorgeht, welches der vier MSBs des Befehlscodes welche ADCs auswählt. Dabei folgen die Bezeichnungen in der Tabelle den Bezeichnungen der Schaltpläne des Projektes POLDI. Die vier MSBs können dabei beliebig variiert werden.

Tabelle 5: Kommunikationsprotokoll: Befehlscodes zur Auswahl der ADCs

| Befehlscode | ausgewählte ADCs           | Signale, die mit den "V+"-Pins |

|-------------|----------------------------|--------------------------------|

|             |                            | der ADCs verbunden sind        |

| 00010110    | U\$19, U\$18               | VOH1, VOH3                     |

| 00100110    | U\$17, U\$16               | VOH0, VOH2                     |

| 01000110    | U\$15, U\$14               | SIN45, SIN135                  |

| 10000110    | U\$13, U\$5                | SIN0, SIN90                    |

| 11110110    | U\$13, U\$5, U\$15, U\$14, | SIN0, SIN90, SIN45, SIN135,    |

|             | U\$17, U\$16, U\$19, U\$18 | VOH0, VOH2, VOH1, VOH3         |

In Tabelle 7 im Anhang sind alle implementierten Befehlscodes des Kommunikationsprotokolls und deren Bedeutungen zu finden.

#### 4.4.2 Funktionsweise

Abbildung 12: Struktur der Komponente "Zuweisung"

Abbildung 12 stellt die Struktur der Komponente "Zuweisung" dar. Sie besteht aus der Komponente "sm\_Zuweisung", welche als Zustandsmaschine entworfen worden ist, und aus der Komponente "ff\_Zuweisung", welche nur synchronisierte Speicherelemente bzw. Flipflops beinhaltet.

#### Eingangssignale der Komponente "Zuweisung":

- Wenn "new\_rx\_data" gleich eins ist, bedeutet dies, dass neue Daten empfangen werden.

- "rx\_data" ist ein 8-Bit-Vektor und beinhaltet die empfangenen Daten.

- "ready5686" zeigt an, ob die Komponente "AD5686" bereit ist, neue Daten zu empfangen.

- "ready5544" zeigt an, ob die Komponente "AD5544" neue Daten erhalten kann.

• "ready0\_90", "ready45\_135", "ready80\_02" und "ready80\_13" geben an, ob die Komponente "AD7980" bereit ist, Signale zu verarbeiten, die bestimmen, welche ADCs ausgelesen und deren Daten anschließend an den PC gesendet werden.

#### Ausgangssignale der Komponente "Zuweisung":

- "new\_rx\_data\_out" teilt der Komponente "Ansteuerung" mit, ob sie die Daten, die der Vektor "rx\_data" der Komponente "avr\_interface" enthält, verarbeiten soll.

- "start55" ist ein 5-Bit-Vektor, welcher der Komponente "AD5544" mitteilt, für welchen DAC vom Typ "AD5544" die Daten, die der 18-Bit-Vektor "daten55" enthält, bestimmt sind.

- "start0\_90", "start45\_135", "start80\_02" und "start80\_13" sind Startsignale für die Komponente "AD7980". Mit dem Setzen eines dieser Signale wird die Auslesung von zwei ADCs und die anschließende Versendung der ausgelesenen Daten an den PC gestartet.

- Mit "readcont" wird die kontinuierliche Auslesung aller ADCs gestartet und gestoppt.

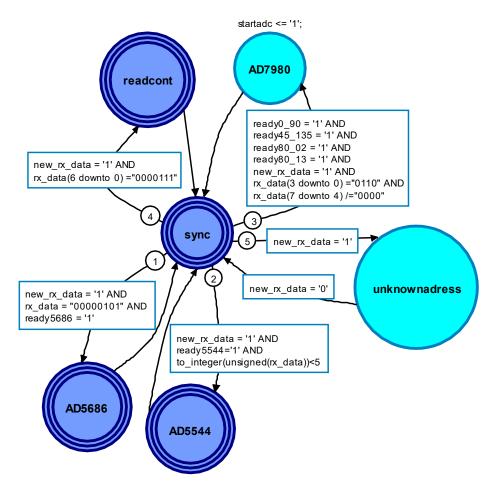

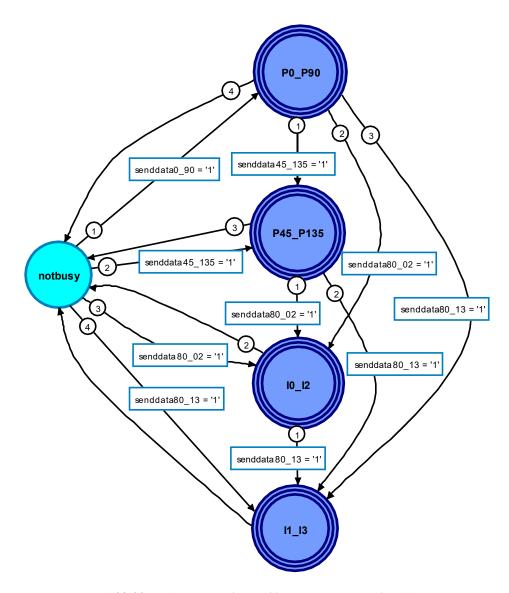

Abbildung 13: Zustandsmaschine "sm\_Zuweisung"

Abbildung 13 zeigt das Zustandsdiagramm der Komponente "sm\_Zuweisung". Es besteht aus den hierarchischen Zuständen "sync", "AD5686". "AD5544", "readcont" und aus den Zuständen "AD7980" und "unknownaddress".

Nachdem die in Kapitel 4.4.1 erklärte Synchronisation im hierarchischen Zustand "sync" abgeschlossen ist, entscheidet u.a. das nächste empfangene Byte über den nächsten Zustand. Die Übergangsbedingungen werden jeweils in den Abschnitten, die den hierarchischen Zuständen zugeordnet sind, erläutert. Die Bedingung für den Übergang der Zustandsmaschine in den Zustand "AD7980" sowie der Zustand an sich werden im Abschnitt beschrieben, der den hierarchischen Zustand "readcont" erklärt, da die beiden Zustände logisch zusammenhängen.

In Abbildung 13 sind die Bedingungen zu sehen, mit denen die Zustandsmaschine vom letzten Zustand des hierarchischen Zustands "sync" mit der nächsten steigenden Taktflanke in einen anderen Zustand übergeht. Falls die Bedingungen mit den vier höchsten Prioritäten nicht erfüllt sind, aber dennoch neue Daten anliegen, wechselt die

Zustandsmaschine in den Zustand "unknownadress". Sie geht erst wieder in "sync" über, wenn keine neuen Daten mehr anliegen.

Die Zustandsmaschine nimmt bis auf einige begründete Ausnahmen jedes Mal bevor die Bedingung abgefragt wird, ob ein neues Byte anliegt, einen Zustand an mit der Bedingung, dass keine neuen Daten anliegen. Dies ist notwendig, da das Signal "new\_rx\_data" länger als einen Takt gleich eins ist und somit ansonsten mehrere Zustände mit der Bedingung, dass "new\_rx\_data" gleich eins ist, nacheinander mit demselben Byte erreicht werden könnten, obwohl nur ein einziges neues Byte empfangen wurde.

Der Anfangszustand der Zustandsmaschine befindet sich im hierarchischen Zustand "sync".

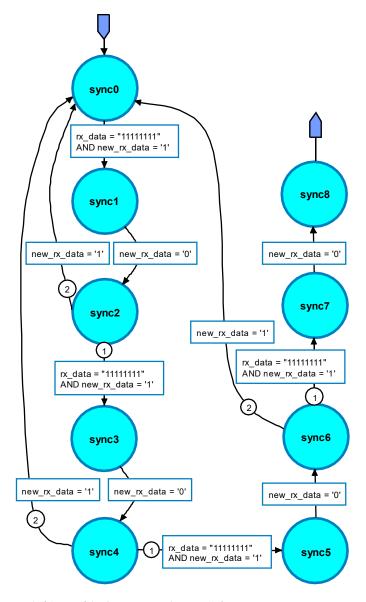

Abbildung 14: hierarchischer Zustand "sync" der Komponente "sm\_Zuweisung"

In Abbildung 14 ist das Zustandsdiagramm des hierarchischen Zustands "sync" zu sehen. Dieser Zustand dient zur Synchronisation. Der Anfangszustand der Komponente "sm\_Zuweisung" ist "sync0". Der Zustand "sync1" wird mit einer steigenden Taktflanke erreicht, wenn ein neues Byte empfangen wird, welches nur mit Einsen gefüllt ist. Von "sync1" wird "sync2" mit einer steigenden Taktflanke erreicht, wenn keine neuen Daten anliegen. Die erläuterten Bedingungen, um von "sync0" zu "sync1" und von "sync1" zu "sync2" zu gelangen, müssen vier Mal nacheinander erfüllt werden, um den Zustand "sync8" zu erreichen. Falls in den Zuständen "sync2", "sync4" oder "sync6" ein neues Byte empfangen wird, welches nicht nur Einsen enthält, wird mit der nächsten steigenden Taktflanke in den Zustand "sync0" gewechselt, um zu gewährleisten, dass eine vollständige Synchronisation mit vier Bytes, welche vollständig mit Einsen gefüllt sind, stattgefunden hat, bevor der hierarchische Zustand "sync" verlassen wird.

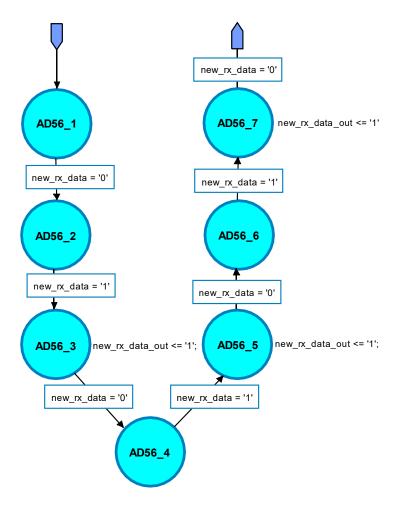

Abbildung 15: hierarchischer Zustand "AD5686" der Komponente "sm\_Zuweisung"

Der hierarchische Zustand "AD5686", welcher in Abbildung 15 dargestellt ist, wird mit einer steigenden Taktflanke nach einer Synchronisation erreicht, wenn ein neues Byte mit

dem Inhalt "00000101" empfangen wird und die Komponente "AD5686" bereit ist, neue Daten zu empfangen. Vom Zustand "AD56\_1" wird mit einer steigenden Taktflanke in den Zustand "AD56\_2" übergegangen, wenn keine neuen Daten anliegen. Danach müssen dreimal hintereinander abwechselnd neue und dann keine neuen Daten anliegen, damit die Zustandsmaschine wieder in den hierarchischen Zustand "sync" gelangt. In den Zuständen, die erreicht werden, wenn neue Daten anliegen, wird das Signal "new\_rx\_data\_out" gleich eins gesetzt. Dadurch weiß die Komponente "Ansteuerung", dass sie die Daten, die der Vektor "rx\_data" der Komponente "avr\_interface" enthält, verarbeiten und mithilfe der Komponente "AD5686" in das Eingangsschieberegister des DACs vom Typ "AD5686" schreiben soll.

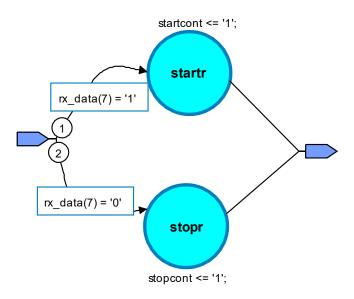

Abbildung 16: hierarchischer Zustand "readcont" der Komponente "sm Zuweisung"

In Abbildung 16 ist der hierarchische Zustand "readcont" zu sehen. Dieser wird mit einer steigenden Taktflanke erreicht, wenn die sieben LSBs des nach einer Synchronisation empfangenen Bytes gleich "0000111" sind (siehe Abbildung 13). Das MSB des Bytes bestimmt über den Nachfolgezustand. Ist dieses gleich eins, wechselt die Zustandsmaschine in den Zustand "startr" und das Signal "startcont" wird gleich eins gesetzt und die Komponente "ff\_Zuweisung" setzt mit der nächsten steigenden Taktflanke das Signal "readcont" high, sodass die Komponente "AD7980" weiß, dass eine kontinuierliche Auslesung aller ADCs gestartet werden soll. Ist das MSB des Bytes allerdings gleich null, so wird das Signal "stopcont" im Zustand "stopr" gleich eins gesetzt, was zur Folge hat, dass die Komponente "ff Zuweisung" das Ausgangssignal "readcont" mit der nächsten

steigenden Taktflanke gleich null setzt. Dadurch wird der Komponente "AD7980" mitgeteilt, dass die kontinuierliche Auslesung gestoppt werden soll.

Sowohl vom Zustand "stopr" als auch vom Zustand "startr" wird ohne Bedingung mit der nächsten steigenden Taktflanke in den hierarchischen Zustand "sync" übergegangen. Es muss also nicht abgewartet werden, bis keine neuen Daten mehr anliegen, da diese Zustände nur erreicht werden können, wenn das empfangene Byte ungleich "11111111" ist. Somit ist sichergestellt, dass das Byte nicht dazu führt, dass es als ein Byte zur Synchronisation genutzt wird. Dasselbe gilt auch für den in Abbildung 13 dargestellten Zustand "AD7980", da dieser Zustand nur erreicht werden kann, wenn das nach einer Synchronisation empfangene Byte nicht voller Einsen ist.

Damit der Zustand "AD7980" nach einer Synchronisation mit einer steigenden Taktflanke erreicht wird, muss ein neues Byte empfangen werden, bei welchem die vier LSBs gleich "0110" und die vier MSBs ungleich "0000" sind. Zudem muss die Komponente "AD7980" bereit sein, die Signale, die die Auslesung der ADCs und die Versendung der ausgelesenen Daten an den PC einleiten, zu verarbeiten. Im Zustand "AD7980" wird das Signal "startade" high gesetzt. Dadurch verarbeitet die Komponente "ff\_Zuweisung" mit der nächsten steigenden Taktflanke die vier MSBs des empfangenen Bytes. Sie trifft mithilfe dieser vier MSBs eine Auswahl der Ausgangssignale "start0\_90", "start45\_135", "start80\_02" und "start80\_13", die sie solange gleich eins setzt, bis die Signale von der Komponente "AD7980" verarbeitet worden sind. Es werden die Signale gleich eins gesetzt, welche die Auslesung der ausgewählten ADCs und die anschließende Versendung der ausgelesenen Daten an den PC einleiten (siehe Tabelle 5).

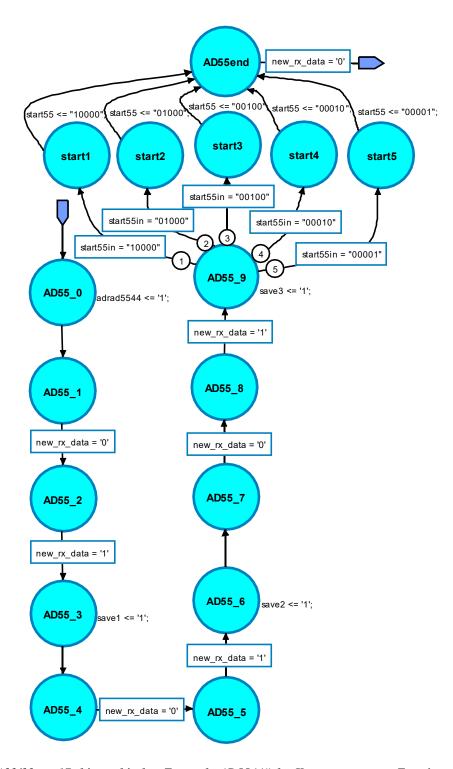

Abbildung 17: hierarchischer Zustand "AD5544" der Komponente "sm\_Zuweisung"

Abbildung 17 zeigt den hierarchischen Zustand "AD5544" der Zustandsmaschine, welcher mit einer steigenden Taktflanke erreicht wird, wenn das dezimale Äquivalent des nach einer Synchronisation empfangenen Bytes kleiner als fünf ist. Im ersten Zustand "AD55\_0" wird das Signal "adrad5544" gleich eins gesetzt. Dadurch wird der Komponente "ff\_Zuweisung" mitgeteilt, dass mit dem empfangenen Befehlscode ein DAC vom Typ "AD5544" ausgewählt worden ist. Die Komponente "ff\_Zuweisung" setzt

dann mit der nächsten steigenden Taktflanke die Bits ihres Ausgangsvektors "start55", um den adressierten DAC auszuwählen. Der Ausgangsvektor "start55" ist mit dem Eingangsvektor "start55in" der Komponente "sm. Zuweisung" verbunden.

Mit den nächsten drei empfangenen Bytes setzt die Zustandsmaschine jeweils unterschiedliche Signale gleich eins. Dadurch speichert die Komponente "ff\_Zuweisung" die drei Bytes an der korrekten Stelle im Vektor "daten55" ab, wobei vom ersten Byte nur die zwei LSBs berücksichtigt werden (siehe Kapitel 4.4.1). Im Zustand "AD55\_9" wird durch das Setzen des entsprechenden Signals das letzte für das Eingangsschieberegister des ausgewählten DACs bestimmte Byte abgespeichert. Von diesem Zustand aus wird entsprechend des Inhalts des Eingangsvektors "start55in" in den passenden Zustand gewechselt, der die Bits des Ausgangsvektor "start55" gemäß des Eingangsvektors "start55in" setzt. Dadurch wird der Komponente "AD5544" mitgeteilt, dass sie die im Vektor "daten55" abgespeicherten Daten in den mit dem Befehlscode adressierten DAC vom Typ "AD5544" schreiben soll. Ausgehend vom Zustand, der den Ausgangsvektor "start55" setzt, wird mit der nächsten steigenden Taktflanke in den Zustand "AD55end" gewechselt. Mit einer steigenden Taktflanke wird dieser letzte Zustand und damit auch insgesamt der hierarchische Zustand "AD5544" verlassen, sobald der Empfang neuer Daten nicht mehr angezeigt wird.

### 4.4.3 Simulation

In den folgenden Simulationen werden nur die für die Funktionsweise des jeweils gezeigten Ablaufs relevanten Signale der Komponente "Zuweisung" dargestellt. Die Bits des Vektors "rx\_data" sind in jeder Abbildung einzeln dargestellt, um nachvollziehen zu können, welche Daten zu welchem Zeitpunkt empfangen werden.

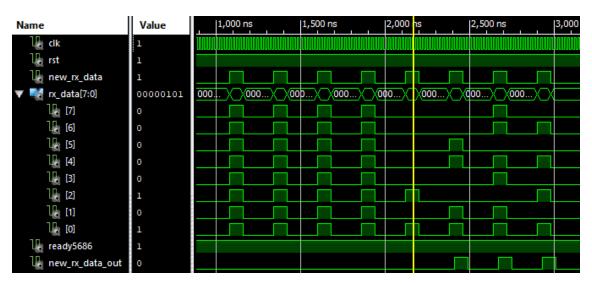

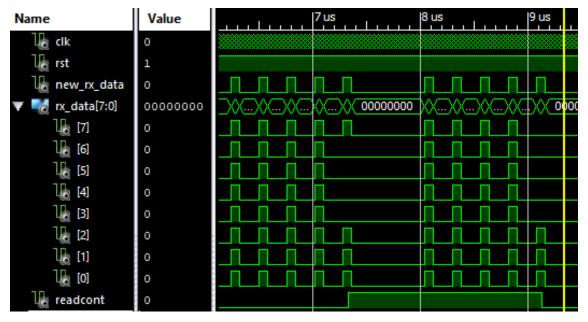

Abbildung 18: Simulation 1 der Komponente "Zuweisung"

In Abbildung 18 ist zu erkennen, dass vier neue Bytes voller Einsen nacheinander empfangen werden. Damit ist die Synchronisation abgeschlossen. Da das Signal "ready5686" gleich eins und das nächste empfangene Byte gleich "00000101" ist, wird damit (siehe Kapitels 4.4.1) der DAC vom Typ "AD5686" ausgewählt. Da das Signal "ready5686" gleich eins ist, wird mit den nächsten drei empfangenen Bytes das Ausgangssignal "new\_rx\_data\_out" gleich eins gesetzt, wodurch der Komponente "Ansteuerung" mitgeteilt wird, dass sie die empfangenen Bytes verarbeiten soll und mithilfe der Komponente "AD5686" in das Eingangsschieberegister des DACs vom Typ "AD5686" schreiben soll.

Abbildung 19: Simulation 2 der Komponente "Zuweisung"

Wie in Abbildung 19 zu sehen ist, werden vier Bytes voller Einsen zur Synchronisation empfangen. Das nächste Byte ist gleich "00000011". Da das Signal "ready5544" gleich eins ist, wird damit ein DAC vom Typ "AD5544" ausgewählt (siehe Kapitel 4.4.1). Die

zwei LSBs des nächsten empfangenen Bytes und die zwei darauf empfangenen Bytes werden im Vektor "daten55" abgespeichert. Die Daten unter "Value" oben links beziehen sich auf den Zeitpunkt, an dem sich der gelbe Marker befindet. Es lässt sich erkennen, dass die Daten richtig im Vektor "daten55" abgespeichert wurden. Zudem ist der Vektor "start55" zu diesem Zeitpunkt für einen Takt gleich "00010", um der Komponente "AD5544" mitzuteilen, dass die im Vektor "daten55" abgespeicherten Daten in den adressierten DAC vom Typ "AD5544" geschrieben werden sollen.

Abbildung 20: Simulation 3 der Komponente "Zuweisung"

Abbildung 20 zeigt, dass das Signal "readcont", welches der Komponente "AD7980" mitteilt, dass eine kontinuierliches Auslesung aller ADCs stattfinden soll, nach erfolgter Synchronisation mit dem Befehlscode "10000111" gesetzt und mit dem Befehlscode "00000111" zurückgesetzt wird.

Abbildung 21: Simulation 4 der Komponente "Zuweisung"

In Abbildung 21 ist zu sehen, dass vier Bytes voller Einsen zur Synchronisation empfangen werden. Danach wird ein Befehlscode mit dem Inhalt "01110110" empfangen, mit dem sechs ADCs gleichzeitig für die Auslesung ausgewählt werden. Da die zu sehenden "ready"-Signale alle gleich eins sind, nehmen drei "start"-Signale einen High-Pegel an und leiten damit die Auslesung der adressierten ADCs und die Versendung der ausgelesenen Daten an den PC ein. Nachdem die dazugehörigen "ready"-Signale nicht mehr gleich eins sind, nehmen die drei "start"-Signale wieder den Wert null an.

# 4.5 Die Komponenten "Ansteuerung" & "AD5686"

Die Komponenten "Ansteuerung" und "AD5686" wurden von der Bachelorarbeit [6] übernommen und in dieses VHDL-Design integriert. Sie dienen der Ansteuerung des DACs vom Typ "AD5686". Die Funktionsweise kann dieser Bachelorarbeit entnommen werden. Das Eingangssignal "new rx data" der Komponente "Ansteuerung" war in dieser Arbeit mit dem Ausgangssignal "new rx data" der Komponente "avr interface" verbunden. Zudem war der Eingangsvektor "rx data" der Komponente "Ansteuerung" mit dem Ausgangsvektor "rx data" der Komponente "avr interface" verbunden. Die Komponente "Ansteuerung" verarbeitet die Daten des Vektors "rx data" nur, wenn das Eingangssignal "new rx data" gleich eins ist [6]. Da in diesem VHDL-Design aber nicht alle Daten für den DAC vom Typ "AD5686" bestimmt sind, wird das Eingangssignal der Komponente "Ansteuerung" "new rx data" mit dem Ausgangssignal "new rx data out" der Komponente "Zuweisung" verbunden. Dieses Signal wird nur dann high gesetzt, wenn Daten empfangen worden sind, die für den DAC vom Typ "AD5686" bestimmt sind.

Außerdem verfügten die Komponenten "Ansteuerung" und "AD5686" über keine asynchronen Resets, weshalb welche hinzugefügt worden sind.

## 4.6 Die Komponente "AD5544"

### 4.6.1 Funktionsweise

Die Komponente "AD5544" dient der Ansteuerung der fünf DACs vom Typ "AD5544". Die Takt- und Dateneingänge der fünf DACs sind jeweils mit denselben Pins des Mojoboards verbunden. Die Auswahl des zu beschreibenden DACs erfolgt über individuelle Chip-Select (CS) Signale. Folglich können während eines Schreibvorganges keine unterschiedlichen Daten in verschiedene DACs geschrieben werden und die Konfiguration der DACs muss dementsprechend einzeln und sequentiell erfolgen.

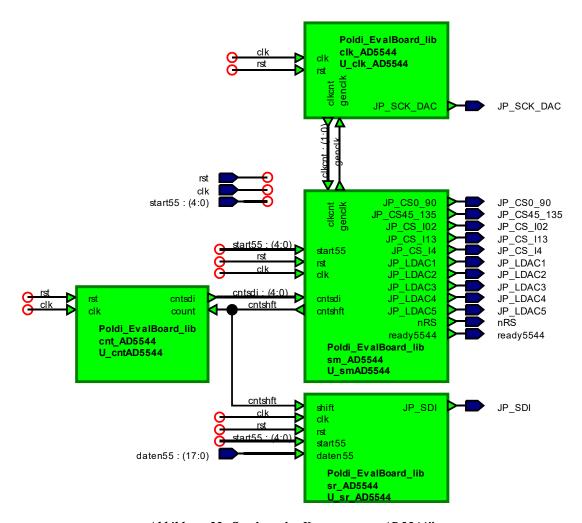

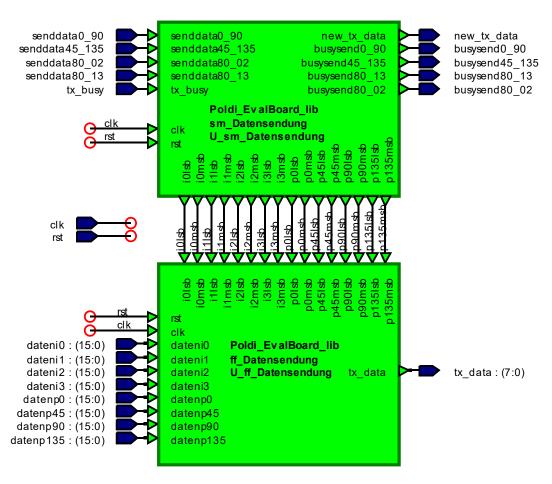

Abbildung 22: Struktur der Komponente "AD5544"

Abbildung 22 visualisiert die Struktur der Komponente "AD5544". Die Komponente besteht aus vier Modulen, wobei "cnt\_AD5544" einem Zähler, sr\_AD5544" einem Schieberegister, "clk\_AD5544" einem Taktgenerator und "sm\_AD5544" einer Zustandsmaschine entspricht.

### Eingangssignale der Komponente "AD5544":

• "start55" gibt an, welcher der fünf DACs vom Typ "AD5544" angesteuert werden soll. Dieser Vektor sollte nur für einen Takt ungleich "00000" gesetzt werden.

• "daten55" ist ein 18 Bit großer Vektor und enthält die Daten, die in das Eingangsschieberegister des ausgewählten DACs geschrieben werden sollen.

### Ausgangssignale der Komponente "AD5544":

- "ready5544" signalisiert, ob die Komponente bereit ist, einen DAC vom Typ "AD5544" anzusteuern.

- "nRS" ist ein Signal für die "RS"-Pins der DACs vom Typ "AD5544" und bleibt konstant high, sodass die Register dieser DACs nie durch dieses Signal auf null gesetzt werden.

- "JP\_CS\_0\_90", "JP\_CS\_45\_135", "JP\_CS\_I02", "JP\_CS\_I13" und "JP\_CS\_I4" sind Signale für die "CS"-Pins der DACs vom Typ "AD5544".

- "JP\_LDAC1", "JP\_LDAC2", "JP\_LDAC3", "JP\_LDAC4" und "JP\_LDAC5" sind Signale für die "LDAC"-Pins der DACs vom Typ "AD5544".

- "JP\_SDI" ist das Signal für die "SDI"-Pins der DACs vom Typ "AD5544".

- "JP\_SCK\_DAC" ist das Signal für die "CLK"-Pins der DACs vom Typ "AD5544".

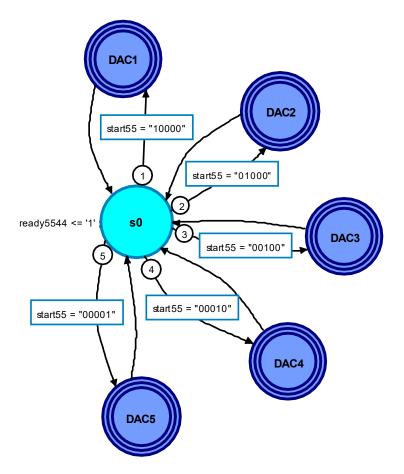

Abbildung 23: Zustandsmaschine "sm\_AD5544"

Abbildung 23 zeigt das Zustandsdiagramm der Komponente "sm\_AD5544". Wenn der Vektor "start55" mit einer der in der Abbildung zu sehenden Übergangsbedingungen übereinstimmt, wechselt die Zustandsmaschine mit der nächsten steigenden Taktflanke vom Anfangszustand "s0" in einen der fünf hierarchischen Zustände. Dabei bestimmt der Vektor "start55", in welchen der fünf hierarchischen Zustände "DAC1" bis "DAC5" gewechselt und somit, welcher der fünf DACs vom Typ "AD5544" angesteuert wird. Wenn der Vektor "start55" ungleich "00000" ist, schreibt die Komponente "sr\_AD5544" mit der nächsten steigenden Taktflanke das MSB des Vektors "daten55" auf das Signal "JP SDI". Das Signal "ready5544" wird nur im Anfangszustand "s0" gleich eins gesetzt.

Die hierarchischen Zustände sind jeweils für die Aktivierung der Signale, die alleinig an einem der fünf DACs vom Typ "AD5544" anliegen, zuständig. Deshalb haben diese Zustände auch ein sehr ähnliches Aussehen. Die Signale "JP\_SDI" für die Daten und "JP\_SCK\_DAC" für den Takt, die an allen DACs vom Typ "AD5544" gleichzeitig anliegen, werden durch die Komponenten "sr AD5544" und "clk AD5544" generiert.

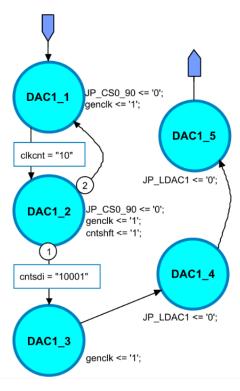

Abbildung 24: hierarchischer Zustand "DAC1" der Komponente "sm\_AD5544"

Da die fünf hierarchischen Zustände gleich aufgebaut sind, wird nur der hierarchische Zustand "DAC1" erläutert, welcher in Abbildung 24 zu sehen ist. Wenn das Signal "genclk" high ist, inkrementiert "clk\_AD5544" den Vektor "clkcnt" mit jeder steigenden Taktflanken um eins. Der Vektor wird mit dem Anfangswert "00" initialisiert, wird dann bis "11" hochgezählt und fällt dann wieder auf den Wert "00". Dementsprechend wird mithilfe dieses Vektors ein 12,5 MHz Takt für die Takteingänge der DACs vom Typ "AD5544" generiert. Wenn das Signal "genclk" nicht gleich eins ist, setzt die Komponente "clk\_AD5544" den Vektor "clkcnt" gleich "00". Der generierte 12,5 MHz Takt hat einen Low-Pegel, wenn der Vektor "clkcnt" gleich "00" oder "01" ist und einen High-Pegel, wenn der Vektor "clkcnt" gleich "10" oder "11" ist. Das Signal "genclk" wird in den ersten drei Zuständen in Abbildung 24 high gesetzt. Außerdem wird in den ersten zwei Zuständen das zur Ansteuerung des DACs notwendige Signal "JP\_CS0\_90" gleich "0" gesetzt.

Wenn der Vektor "clkcnt" gleich "10" ist, wird mit der nächsten steigenden Taktflanke in den Zustand "DAC1\_2" gewechselt. Dort wird das Signal "cntshft" high gesetzt. Immer, wenn das Signal "cntshft" gleich eins ist, inkrementiert mit der nächsten steigenden Taktflake das Modul "cnt\_AD5544" den Vektor "cntsdi", ausgehend vom Anfangswert "00000" um eins bis der Wert "10001" erreicht ist. Gleichzeitig wird durch das Modul

"sr\_AD5544" das Signal "JP\_SDI" mit dem jeweiligen Bit des Vektors "daten55" aktualisiert. Dadurch entspricht das Signal "JP\_SDI" immer, wenn der Vektor "clkcnt" den Wert "00" annimmt, d.h. mit jeder fallenden Flanke des erzeugten 12,5 MHz Taktes, dem nächsten Bit des Vektors "daten55".

Vom Zustand "DAC1\_2" wird, sofern der Vektor "cntsdi" nicht gleich "10001" ist, mit der nächsten steigenden Taktflanke in den Zustand "DAC1\_1" gewechselt. Ist der Vektor "cntsdi" gleich "10001", wechselt die Zustandsmaschine mit der nächsten steigenden Taktflanke vom Zustand "DAC1\_2" in den Zustand "DAC1\_3". Wenn das Signal "cntshft" gleich eins ist, obwohl der Vektor "cntsdi" gleich "10001" ist, setzt die Komponente "cnt\_AD5544" den Vektor "cntshf" mit der nächsten steigenden Taktflanke gleich null, sodass er wieder gleich seinem Anfangswert ist. Dies passiert also gleichzeitig mit dem Wechsel vom Zustand "DAC1\_2" in den Zustand "DAC1\_3". Wenn sich die Zustandsmaschine im Zustand "DAC1\_3" befindet, sind 18 steigende Taktflanken des 12,5 MHz Taktes generiert worden. Somit hat das Signal "JP\_SDI" jedem Bit des Vektors "daten55" entsprochen.

Vom Zustand "DAC1\_3" wird der Zustand "DAC1\_4" mit der nächsten und von diesem der Zustand "DAC1\_5" mit der übernächsten steigenden Taktflanken erreicht. In den beiden zuletzt genannten Zuständen wird das für die Ansteuerung erforderliche Signal "JP\_LDAC1" high gesetzt. Der Zustand "DAC1\_3" ist notwendig, um eine gewisse benötigte Zeit zwischen der letzten fallenden Flanke des 12,5 MHz Taktes und dem Setzen des Signals "JP\_LDAC1" auf einen Low-Pegel verstreichen zu lassen. Aus dem Zustand "DAC1\_5" wird mit der nächsten steigenden Taktflanke der hierarchische Zustand "DAC1" verlassen und in den Anfangszustand "s0" gewechselt.

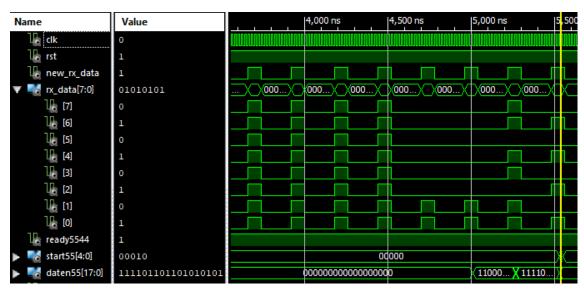

### 4.6.2 Simulation

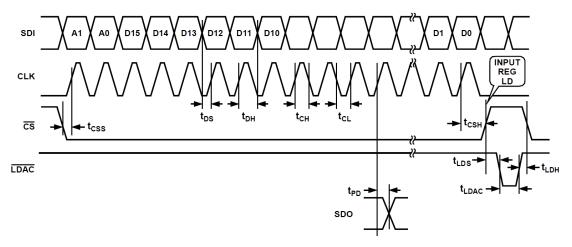

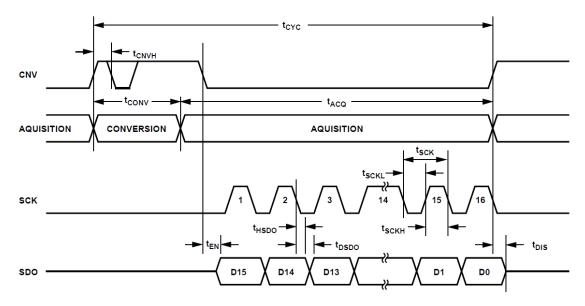

Abbildung 25: Zeitablaufdiagramm der Ansteuerung eines DACs vom Typ "AD5544" [1]

In Abbildung 25 ist zu sehen, wie die Signale, die an den Pins eines DACs vom Typ "AD5544" anliegen, für eine erfolgreiche Ansteuerung verlaufen müssen. Zusammen mit zusätzlichen Informationen des DAC Datenblatts wird der Verlauf erklärt. Zuerst muss das am "CS"-Pin anliegende Signal low gesetzt werden. Danach sollte am "CLK"-Pin ein maximal 20 MHz schnelles Taktsignal anliegen. Das erste Bit, was am "SDI"-Pin anliegt, muss mindestens 20 ns vor der ersten steigenden Taktflanke anliegen. Das am "SDI"-Pin anliegende Signal wird mit der steigenden Flanke des Taktsignals übernommen, weswegen es mit der fallenden Flanke des Signals gesetzt werden muss. Nach 18 steigenden und fallenden Flanken, muss das Taktsignal wieder konstant gleich null sein und das Signal, welches am "CS"-Pin anliegt, muss wieder high werden. Dies darf frühestens 25 ns nach der letzten steigenden Taktflanke geschehen. Nachdem dieses Signal wieder high ist, müssen mindestens 5 ns vergehen, bis das am "LDAC"-Pin anliegende Signal für mindestens 25 ns low und anschließend wieder high ist. Diese Sequenz führt zu einer erfolgreichen Ansteuerung des DACs. [1]

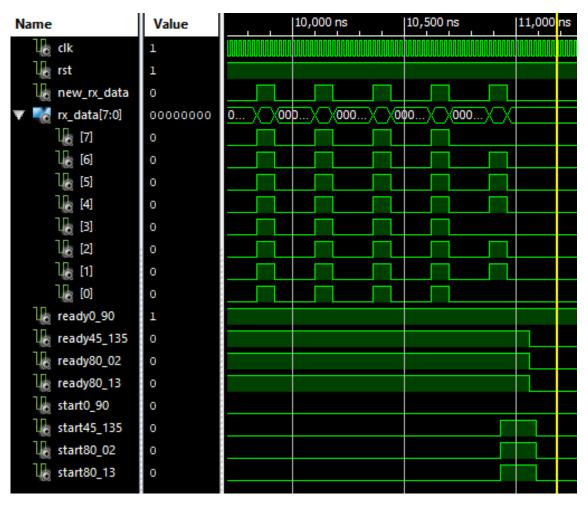

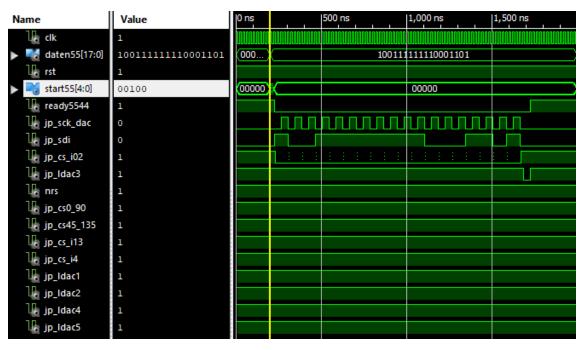

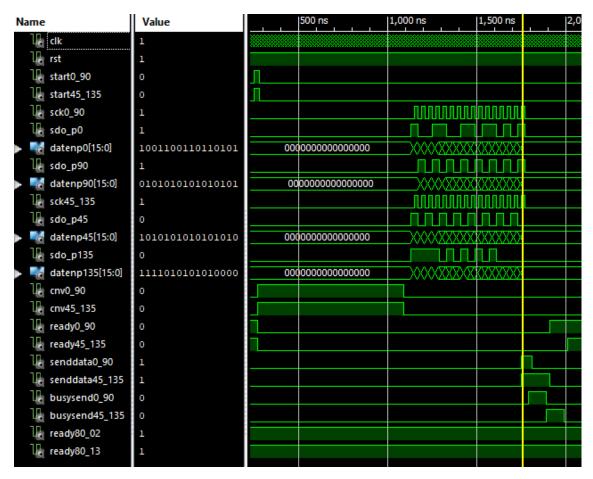

Abbildung 26: Simulation der Komponente "AD5544"

In Abbildung 26 ist eine Simulation der Komponente "AD5544" zu sehen. Nachdem der Vektor "start55" für einen Takt gleich "00100" ist, beginnt die Ansteuerung des mit diesem Signal ausgewählten DACs vom Typ "AD5544". Als erstes nimmt das Signal für den "CS"-Pin des ausgewählten DACs einen Low-Pegel und das Signal "JP\_SDI" den Pegel des MSBs des Vektors "daten55" an. Gleichzeitig wird das Signal "ready5544" gleich null gesetzt. Nach 40 ns liegt am Signal "JP\_SCK\_DAC" für den "CLK"-Pin die erste steigende Taktflanke des folgenden 12,5 MHz Taktes an. Es lässt sich erkennen, dass mit jeder weiteren fallenden Flanke des "JP\_SCK\_DAC"-Signals das Signal "JP\_SDI" den Pegel des nächst minderwertigeren Bits des Vektors "daten55" annimmt. 40 ns nach der letzten steigenden Taktflanke nimmt das Signal für den "CS"-Pin des ausgewählten DACs wieder einen High-Pegel an. Nach weiteren 20 ns nimmt das Signal für den "LDAC"-Pin des ausgewählten DACs für 40 ns einen Low-Pegel an. Danach ist das Signal "ready5544" wieder high.

Der Simulationsverlauf entspricht somit dem für eine erfolgreiche Ansteuerung erforderlichen Verlauf.

# 4.7 Die Komponente "AD7980"

### 4.7.1 Funktionsweise

Die Komponente "AD7980" dient der Auslesung der ADCs und beinhaltet hierfür zwei Modi. Bei einem Modus erfolgt eine einmalige Auslesung, während beim alternativen Modus eine kontinuierliche Auslesung der ADCs erfolgt. Die Pins von je zwei ADCs, die die Umwandlung einer an einem ADC anliegenden Spannung in einen Digitalwert steuern, sind immer mit demselben Pin des Mojoboards verbunden. Dasselbe gilt auch für die Pins des Taktes zweier ADCs. Die Ansteuerung der ADCs erfolgt demnach immer paarweise. Aus diesem Grund ist es sinnvoll, dass immer entweder zwei, vier, sechs oder acht ADCs ausgelesen werden. Im Modus der einmaligen Auslesung werden die ausgelesenen Daten anschließend mithilfe der Komponente "Datensendung" an den PC gesendet.

Im kontinuierlichen Modus beginnt nach Vollendung eines Auslesevorganges direkt der nächste. In diesem Modus werden die ausgelesenen Daten nicht an den PC gesendet, da für die Applikation eine Vorverarbeitung der Daten im FPGA vorgesehen ist. Außerdem werden in diesem Modus alle ADCs ausgelesen.

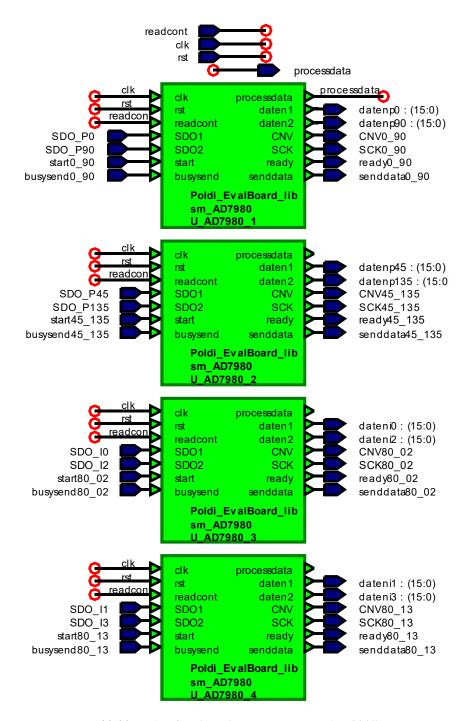

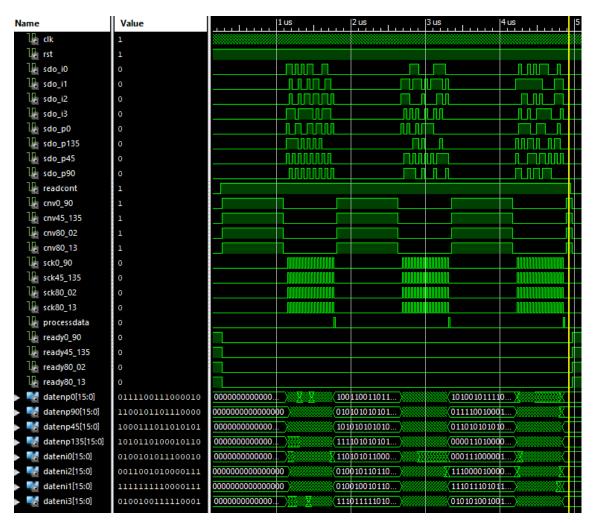

Abbildung 27: Struktur der Komponente "AD7980"

Abbildung 27 zeigt die Struktur der Komponente "AD7980". Zu sehen ist, dass diese Komponente vier Instanzen des Moduls "sm\_AD7980" nutzt. Jede der vier Instanzen ist für die Auslesung von zwei ADCs zuständig.

Abbildung 28: Struktur der Komponente "sm\_AD7980"

In Abbildung 28 ist die Struktur der Komponente "sm\_AD7980" zu sehen. Diese Komponente steuert die zwei am Anfang dieses Kapitels erwähnten Auslesungsmodi für zwei ADCs und besteht aus vier Komponenten, wobei "cnt1\_AD7980" einem Zähler, "sm1\_AD7980" einer Zustandsmaschine, "clk\_AD7980" einem Taktgenerator und "sr1\_AD7980" einem Schieberegister entspricht.

### Eingangssignale der Komponente "sm AD7980":

- Mit "readcont" kann die kontinuierliche Auslesung der ADCs gestartet und gestoppt werden. Da bei der kontinuierlichen Auslesung alle ADCs zeitgleich ausgelesen werden sollen, wird, wie in Abbildung 27 zu sehen ist, "readcont" allen vier Instanzen der Komponente "sm\_AD7980" zugeführt. Die kontinuierliche Auslesung bleibt so lange, wie dieses Signal high ist, aktiviert.

- "busysend" zeigt an, ob die Komponente "Datensendung" damit beschäftigt ist, die ausgelesenen Daten der Komponente "sm AD7980" an den PC zu senden.

- Wenn "start" high ist, sollen die zwei ADCs ausgelesen und die ausgelesenen Daten anschließend mithilfe der Komponente "Datensendung" an den PC gesendet werden. Dieses Signal sollte wieder low werden, sobald das Signal "ready" dieser Komponente gleich null ist.

• "SDO1" und "SDO2" werden von den "SDO"-Pins zweier ADCs getrieben, an denen jeweils die Daten eines ADCs anliegen.

### Ausgangssignale der Komponente "sm\_AD7980":

- "CNV" treibt die "CNV"-Pins von jeweils zwei ADCs.

- "SCK" treibt die Takteingänge "SCK" von jeweils zwei ADCs.

- "ready" zeigt an, ob die Komponente bereit ist, einen neuen Auslesevorgang mit anschließender Sendung der ausgelesenen Daten an den PC durch die Komponente "Datensendung" zu starten.

- "senddata" signalisiert der Komponente "Datensendung", dass sie die Daten von zwei ausgelesenen ADCs an den PC senden soll. Dabei beinhaltet der 16-Bit Vektor "daten1" die Daten des ADCs, der mit dem Eingangssignal "SDO1" verbunden ist und der 16-Bit-Vektor "daten2" die Daten des ADCs, der mit dem Eingangssignal "SDO2" verbunden ist.

- "processdata" zeigt an, dass ein Auslesevorgang im Modus der kontinuierlichen Auslesung abgeschlossen worden ist. Da die vier genutzten Instanzen des Moduls "sm\_AD7980" in diesem Modus gleichzeitig arbeiten, wird nur das Ausgangssignal einer der Instanzen mit dem Signal "processdata" in Abbildung 27 verknüpft.

Abbildung 29: Zustandsmaschine "sm1\_AD7980"

Abbildung 29 zeigt das Zustandsdiagramm der Komponente "sm1\_AD7980". Nur im Anfangszustand "dflt" wird das Signal "ready" high gesetzt. Wenn das Signal "start" in diesem Zustand gleich eins ist, wechselt die Zustandsmaschine mit der nächsten steigenden Taktflanke in den hierarchischen Zustand "readsend". Wenn das Signal "readcont" gleich eins ist, wechselt sie vom Anfangszustand "dflt" mit der nächsten steigenden Taktflanke in den hierarchischen Zustand "readcont".

Abbildung 30: hierarchischer Zustand "readsend" der Komponente "sm1\_AD7980"

Abbildung 30 zeigt den hierarchischen Zustand "readsend" der Komponente "sm1\_AD7890", welche im Zusammenspiel mit den anderen Modulen der Komponente "sm\_AD7980" zwei ADCs ausliest und die ausgelesenen Daten mithilfe der Komponente "Datensendung" an den PC sendet. Im Zustand "t CONV" wird das für die Ansteuerung

der ADCs notwendige Signal "CNV" high gesetzt. Außerdem wird das Signal "cntcnv" gleich eins gesetzt. Dadurch zählt die Komponente "cnt1\_AD7980" ab diesem Zeitpunkt die steigenden Taktflanken mit und setzt mit der vierzigsten steigenden Taktflanke das Signal "finishedconv" gleich eins. Wenn dies der Fall ist, wechselt die Zustandsmaschine mit der nächsten steigenden Taktflanke in den Zustand "t\_EN1", in welchem das Signal "CNV" nicht mehr gleich eins ist.

Im Zustand "t\_EN1" sowie im nächsten Zustand "t\_EN2", der mit der nächsten steigenden Taktflanke erreicht wird, wird kein Signal gesetzt. Dies ist für die erfolgreiche Auslesung der ADCs notwendig. Von "t\_EN2" wird in den Zustand "t\_EN3" mit der nächsten steigenden Taktflanke übergegangen. Dort werden die Signale "genclk" und "shift" gleich eins gesetzt. Solange das Eingangssignal "saveddata" nicht gleich eins ist, wird von "t\_EN3" immer mit einer steigenden Taktflanke in den Zustand "s0" übergegangen. In diesem Zustand werden die Signale "genclk" und "cntsr" high gesetzt und es wird mit der nächsten steigenden Taktflanke in den Zustand "t\_EN3" gewechselt.

Wenn das Signal "genclk" high ist, erzeugt die Komponente "clk\_AD7980" mit dem Ausgangssignal "SCK" einen 25 MHz Takt für den Takteingang der ADCs. Wenn das Signal "shift" gleich eins ist, speichert die Komponente "sr1\_AD7980" mit der nächsten steigenden Taktflanke den Wert, den das Signal "SDO1" zu diesem Zeitpunkt hat, im Vektor "daten1" und den Wert, den das Signal "SDO2" zu diesem Zeitpunkt hat, im Vektor "daten2" ab. Die Werte werden in die LSBs der Vektoren "daten1" und "daten2" geschoben, wobei zeitgleich die alten 15 LSBs der Vektoren jeweils ein Bit an Wertigkeit gewinnen, sodass nach Abspeichern aller 16 Bits die zuerst abgespeicherten Werte den MSBs und die zuletzt abgespeicherten Werte den LSBs der Vektoren "daten1" und "daten2" entsprechen. Die Abspeicherung geschieht zeitgleich mit den steigenden Taktflanken des 25 MHz Taktes.