# Fachhochschule Dortmund

University of Applied Sciences and Arts

## **Bachelorarbeit**

Fachbereich: Informations- und Elektrotechnik (A&A)

# Entwurf und Layout einer Treiberstufe für die Verwendung in einem synchronen Abwärtswandler

Yassine Choukri

Matr.-Nr.: 7085341

Erstprüfer: Prof. Dr.-Ing. Michael Karagounis

Zweitprüfer: M. Eng. Andreas Stiller

## Kurzfassung

In dieser Arbeit wird eine Treiberstufe für die Verwendung in einem synchronen Abwärtswandler entwickelt.

Der Abwärtswandler hat das Ziel, eine Eingangsspannung von 3,3 V in eine Ausgangsspannung von 1,2 V umzuwandeln. Der Schalter der Treiberstufe wird in einer 180nm CMOS Technologie entworfen und durch die Firma UMC (United Microelectronics Corporation) produziert.

Der entwickelte Schalter der Treiberstufe wird in einem synchronen Abwärtswandlers integriert und wird für alle Funktionen verifiziert.

Für den Entwurf und das Layout der Schaltung des Treibers wird die Software "Virtuoso 6.1-64b" des Herstellers "Cadence Design Systems" verwendet. Diese Software bietet Simulationsmodelle für alle im Abwärtswandler verwendeten Bauteile.

#### **Abstract**

In this thesis a driver stage switch is developed for use in a synchronous step-down converter.

The step-down converter aims to convert an input voltage of 3.3 V to an output voltage of 1.2 V, designed in a 180nm CMOS technology and produced by UMC (United Microelectronics Corporation).

The developed driver stage switch is integrated in a synchronous step-down converter and is verified for all functions.

For the design and layout of the driver circuit, the software "Virtuoso 6.1-64b" of the manufacturer "Cadence Design Systems" is used. This software provides simulation models for all components used in the step-down converter

.

Inhaltsverzeichnis

## Inhaltsverzeichnis

| Inl              | haltsverzeichnis                                                      | I  |

|------------------|-----------------------------------------------------------------------|----|

| ΑŁ               | obildungsverzeichnis                                                  | II |

| Ta               | abellenverzeichnis                                                    | IV |

| ΑŁ               | okürzungsverzeichnis                                                  | V  |

| 1                | Einleitung                                                            | 1  |

| 2                | Aufbau und Funktion des Abwärtswandlers                               | 2  |

| 3                | Grundlagen der CMOS Technologie                                       | 5  |

| 4                | Komponentenbeschreibungen des CMOS Gatter                             | 8  |

|                  | 4.1 CMOS Inverter-Gatter                                              | 8  |

|                  | 4.2 CMOS NOR-Gatter                                                   | 10 |

|                  | 4.3 CMOS NAND-Gatter Funktion                                         | 12 |

| 5                | Entwurf der Schaltung für die Treiberstufe                            | 16 |

|                  | 5.1 Schaltungsvariante I                                              | 16 |

|                  | 5.2 Schaltungsvariante II                                             | 20 |

| 6                | Integration der Treiberstufe im Tiefsetzsteller                       | 24 |

|                  | 6.1 PVT-Simulation der Treiberstufe                                   | 24 |

|                  | 6.2 Hauptschaltung des Tiefsetzstellers mit integrierter Treiberstufe | 26 |

|                  | 6.3 Simulation des Abwärtswandlers                                    | 28 |

| 7                | Layout                                                                | 29 |

|                  | 7.1 Layout-Erstellung für einen Inverter                              | 29 |

|                  | 7.1.1 Erstellung einer Zelle                                          | 29 |

|                  | 7.1.2 Einfügen und Verbinden der Bauelemente                          | 32 |

|                  | 7.1.3 Überprüfung des Layouts                                         | 38 |

|                  | 7.2 Erstellung des Gesamtlayouts                                      | 40 |

| 8                | Fazit                                                                 | 44 |

| l i <del>t</del> | taraturvarzaichnis                                                    | 15 |

## Abbildungsverzeichnis

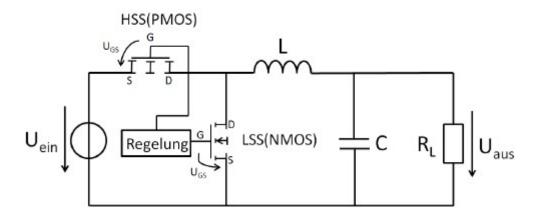

| Abbildung 2.1: | Grundaufbau des synchronen Abwärtswandlers                | 2  |

|----------------|-----------------------------------------------------------|----|

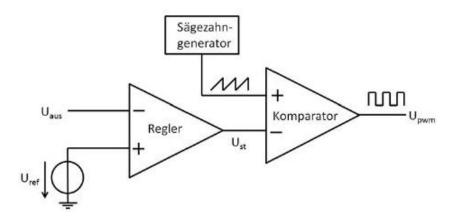

| Abbildung 2.2: | Aufbau der Regelung                                       | 3  |

| Abbildung 2.3: | PID-Regler                                                | 3  |

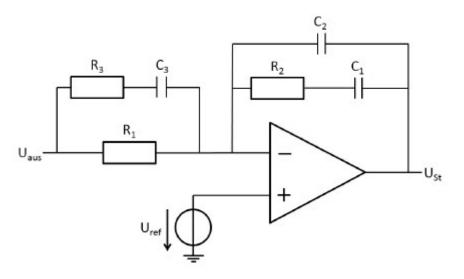

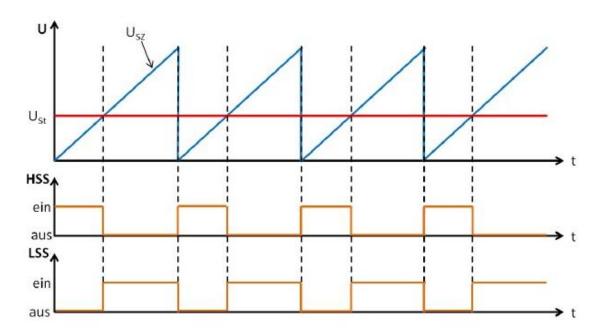

| Abbildung 2.4: | Erzeugung PWM-Signal im Komparator                        | 4  |

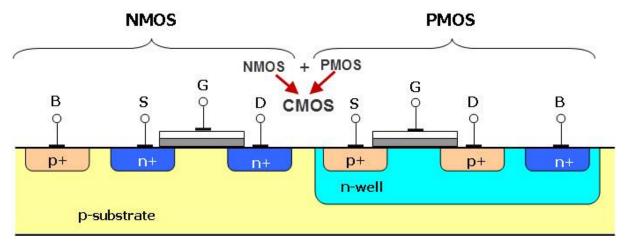

| Abbildung 3.1: | Schaltbild und Erläuterung zu NMOS und PMOS               | 5  |

| Abbildung 3.2: | NMOS Transistor [1]                                       | 6  |

| Abbildung 3.3: | PMOS Transistor [1]                                       | 6  |

| Abbildung 3.4: | Der CMOS Inverter, Schaltplan, und logisch Symbol [2]     | 7  |

| Abbildung 4.1: | Inverter-Symbol                                           | 8  |

| Abbildung 4.2: | Schematic CMOS-Iverter-Gatter                             | 9  |

| Abbildung 4.3: | INV-Gatter Simulation Ergebnisse                          | 10 |

| Abbildung 4.4: | NOR-Gatter Symbol                                         | 10 |

| Abbildung 4.5: | Schematic NOR-Gatter                                      | 11 |

| Abbildung 4.6: | NOR-Gatter Simulation Ergebnisse                          | 12 |

| Abbildung 4.7: | NAND-Gatter Symbol                                        | 13 |

| Abbildung 4.8: | Schematic NAND-Gatter                                     | 14 |

| Abbildung 4.9: | NAND-Gatter Simulationsergebnisse                         | 15 |

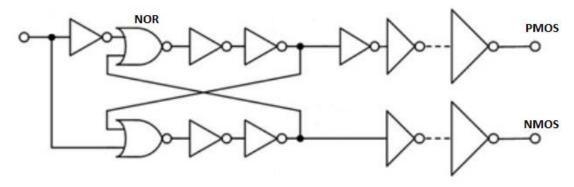

| Abbildung 5.1: | Konzept Treiberschaltung mit interner Totzeit             | 16 |

| Abbildung 5.2: | Umsetzung der Schaltungsvariante I                        | 18 |

| Abbildung 5.3: | Simulation Schaltungsvariante I                           | 19 |

| Abbildung 5.4: | Konzept Schaltung II                                      | 20 |

| Abbildung 5.5: | Die zweite vorgeschlagene Schaltung des Treibers          | 22 |

| Abbildung 5.6: | Simulation Schaltungsvariante II                          | 23 |

| Abbildung 6.1: | Tiefsetzsteller mit integriertem Treiber                  | 27 |

| Abbildung 6.2: | Simulation des Tiefsetzstellers                           | 28 |

| Abbildung 7.1: | Dialog für die Spezifikation eines neuern Layout-Fensters | 30 |

| Abbildung 7.2: | Fenster Layout L Editor                                   | 30 |

| Abbildung 7.3: | Layer-Auswahlfenster (LSW)                                | 31 |

| Abbildung 7.4: | Fenster Anzeigeoptionen (Display Options)                 | 32 |

| Abbildung 7.5: | Einfügen des PMOS und NMOS                                | 33 |

| Abbildung 7.6: | Verbindung der Gate-Elektroden                            | 34 |

| Abbildung 7.7: | Erstellen der Kontakte M1_PIIFF für NMOS und M1_NWEL fü   | ır |

|                | PMOS                                                      | 34 |

| Abbildung 7.8: | Verbindung von Gates und Drains                           | 35 |

| Abbildung 7.9: | Erstellen Via M1_POLY                                     | 36 |

| Abbildung 7.10: Erstellen von Labels                             | 37 |

|------------------------------------------------------------------|----|

| Abbildung 7.11: Vollständiges Inverter-Layout                    | 37 |

| Abbildung 7.12 Results Viewing Environment des Design Rule Check | 38 |

| Abbildung 7.13: Results Viewing Environment des LVS-Check        | 39 |

| Abbildung 7.14: Layout NOR- und NAND-Gatter                      | 40 |

| Abbildung 7.15: Dialog zum Entfernen der Hierarchien             | 40 |

| Abbildung 7.16: Beschneiden von Layern.                          | 41 |

| Abbildung 7.17: Zelle mit drei Invertern in Reihe                | 42 |

| Abbildung 7.18: Layout der vollständigen Treiberstufe            | 43 |

Tabellenverzeichnis IV

## **Tabellenverzeichnis**

| Tabelle 4.1: Wahrheit   | tstabelle Inverter-Gatter                    | 9   |

|-------------------------|----------------------------------------------|-----|

| Tabelle 4.2: Wahrheit   | tstabelle NOR-Gatter                         | 12  |

| Tabelle 4.3: Wahrheit   | tstabelle NAND-Gatter                        | 14  |

| Tabelle 5.1: Anstiegs-  | - und Abfallzeiten für Schaltungsvariante I  | 20  |

| Tabelle 5.2: Anstiegs-  | - und Abfallzeiten für Schaltungsvariante II | 23  |

| Tabelle 6.1: Ergebnis   | se PVT-Simulation der Treiberstufe           | 25  |

| Tabelle 6.2: Simulierte | e Zeiten bei Standardbetriebsbedingungen     | 25  |

| Tabelle 6.3: Simulierto | e Zeiten bei Minimal- und Maximalbedingunger | ı26 |

## Abkürzungsverzeichnis

CMOS Complementary metal-oxide-semiconductor

DRC Design Rule Check

EN Enable Signal

HSS High Side Switch

LSS Low Side Switch

LSW Layer Selection Window

LVS Layout versus Schematic

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NMOS n-Kanal metal-oxide-semiconductor

PID: proportional-integral-derivative Controller

PMOS p-Kanal metal-oxide-semiconductor

PVT Process, Voltage, Temperaturen

RVE Results Viewing Environment

S1 Schalter 1

S2 Schalter 2

RVE Results Viewing Environment

LC-Glied Kombination von Induktivität und Kapazität

PWM Pulsweitenmodulator

SZ Sägezahn

1 Einleitung

## 1 Einleitung

Für viele elektrische Geräte ist es notwendig, eine hohe Gleichspannung des Netzteils oder der Batterie in eine niedrige Ausgangsspannung umzuwandeln. Als Beispiele können die Prozessorversorgungsspannungen in einem Computer oder Ladegeräten für Akkumulatoren und elektronische Displays in Automobilen genannt werden. Um diesen Spannungswandlung umzusetzen, wird oft ein Abwärtswandler, der auch als Tiefsetzsteller bezeichnet wird, eingesetzt.

In dieser Arbeit wird ein Treiber für die Schalter in einem synchronen Abwärtswandler entwickelt. Der synchrone Abwärtswandler wird in CMOS Technologie aufgebaut. Die CMOS Technologie stellt sowohl einen p-Kanal-Transistor als auch einen n-Kanal-Transistor zur Verfügung. Bei einem integrierten Tiefsetzsteller wird dies ausgenutzt indem der High-Side Schalter(HSS) durch einen PMOS Transistor und der Low-Side Schalter(LSS) durch einen NMOS Transistor implementiert wird, mit dem Ziel die gewünschte Ausgangsspannung zu generieren.

Der Ein- und Ausschaltvorgang der beiden Schalttransistoren muss jedoch aufeinander abgestimmt werden, um zu verhindern dass beide Transistoren gleichzeitig geschlossen sind und ein direkter Kurzschluss zwischen der Eingangsspannung und Masse entsteht. Dieser Kurzschluss führt zu einem erhöhten Stromfluss und reduziert die Effizienz des Wandlers.

Bei geringen Lastströmen kann sich bei einem synchronen Abwärtswandler auch ein negativer Spulenstrom durch den NMOS Transistor einstellen.

Dieser zusätzliche Stromfluss, der bei einem asynchronen Tiefsetzsteller auf Grund der gleichrichtenden Wirkung der Diode, welche im Low-Side Zweig üblicherweise verwendet wird, hat eine weitere Absenkung der Wandlungseffizienz zur Folge.

Aus diesem Grund wird im Rahmen dieser Arbeit eine Treiberstufe entwickelt, welche zur Vermeidung von Kurzschlüssen nicht überlappende Schaltsignale für das PMOS-NMOS-Schalttransistorpaar generiert und für die Vermeidung von negativen Strömen durch den NMOS die Abschaltung beider Schalttransistoren erlaubt.

#### 2 Aufbau und Funktion des Abwärtswandlers

Der Abwärtswandler, welcher auch Tiefsetzsteller genannt wird (englisch: Buck-Converter oder Step-Down-Converter), wandelt eine Eingangsspannung in eine niedrigere Ausgangsspannung um. Der Vorteil des Abwärtswandlers besteht darin, dass auf Grund des geschalteten Wandlungsprinzips geringe Leistungsverluste und somit hohe Wirkungsgrade erreicht werden können.

#### Aufbau

Wie in Abbildung 2.1 dargestellt, besteht der synchrone Abwärtswandler aus zwei Leistungs-MOSFETs, einer vom n-Typ (NMOS) und einer vom p-Typ (PMOS), einer Ausgangsspule und einem Ausgangskondensator sowie der Regelung der beiden Halbleiterschalter. Dabei wird der PMOS auch als HSS (High Side Switch) und der NMOS als LSS (Low Side Switch) bezeichnet.

Abbildung 2.1: Grundaufbau des synchronen Abwärtswandlers

Der PMOS ist direkt an die Eingangsspannung der Schaltung angeschlossen. Wenn der PMOS geschlossen ist, wird die Eingangsspannung an die Spule durchgeschaltet. Während dieser Zeit ist der NMOS ausgeschaltet und der Strom durch die Spule steigt an, wodurch das LC-Glied aufgeladen wird. Wenn der PMOS geöffnet ist, wird der NMOS geschlossen, wodurch die Spule mit Masse verbunden wird. In diesem Schaltzustand nimmt der Strom durch die Spule ab, wodurch das LC-Glied entladen wird.

Das LC-Glied besteht aus einer Induktivität und einem Kondensator. Es speichert und liefert Energie an die Last und glättet die Ausgangspannung. Das LC-Glied entspricht einem Tiefpass zweiter Ordnung.

Zur Reglung des Abwärtswandlers werden ein PID Regler, ein Komparator und ein Sägezahngenerator benötigt.

Abbildung 2.2: Aufbau der Regelung

Das Ziel der Regeleinheit ist es, dass die 3.3-V-Eingangsspannung in eine 1.2-V-Ausgangsspannung gewandelt wird. Hierfür wird die Ausgangsspannung an den in Abbildung 2.3 dargestellten PID Regler zurückgeführt und mit einer Referenzspannung verglichen. Im eingeschwungenen Zustand entspricht die zurückgeführte Spannung der Referenzspannung.

Abbildung 2.3: PID Regler

Der PID Regler besteht aus einem Operationsverstärker, welcher als invertierender Verstärker verschaltet ist. Er verwendet drei Kondensatoren und drei Widerstände um die proportionale, differentiale und integrale Wirkung des Reglers zu erreichen. Die Ausgangsspannung des Reglers wird über einen Komparator mit einer Sägezahnspannung verglichen. Der Vergleich erzeugt ein pulsweitenmoduliertes Signal am Komparator-Ausgang, welches für die Schaltung der Leistungstransistoren verwendet wird (siehe Abbildung 2.4).

Abbildung 2.4: Erzeugung PWM-Signal im Komparator

Der Pulsweitenmodulator wurde durch eine Schaltung bestehend aus einem Komparator und einem Sägezahngenerator implementiert.

Wenn die Steuerspannung größer als die Sägezahnspannung wird, dann gibt der Komparator eine logische "0" aus. Als Folge wird der HSS (PMOS) geschlossen und der LSS (NMOS) geöffnet und die Ausgangsspannung des Abwärtswandlers nimmt zu.

Wenn die Steuerspannung kleiner als die Sägezahnspannung wird, dann gibt der Komparator eine logische "1" aus. Als Folge wird der HSS (PMOS) geöffnet und der LSS (NMOS) geschlossen und die Ausgangsspannung des Abwärtswandlers nimmt ab.

## 3 Grundlagen der CMOS Technologie

Der Begriff CMOS steht für "Complementary Metal Oxide Semiconductor". Die CMOS Technologie ist die am häufigsten eingesetzte Technologie in der Computerchip-Design-Industrie. Sie wird insbesondere für hochintegrierte Schaltungen wie Mikroprozessoren, Mikrocontroller-Chips und Speicher d. h. RAM, ROM, EEPROM eingesetzt und wird auch bei anwendungsspezifischen integrierten Schaltungen (ASICs) in zahlreichen und vielfältigen Anwendungen eingesetzt. Heutige Computerspeicher, CPUs und Mobiltelefone nutzen diese Technologie auf Grund mehrerer Vorteile. Bei dieser Technologie stehen zwei MOSFETs, einer vom n-Typ (NMOS) und einer vom p-Typ (PMOS) zur Verfügung.

Abbildung 3.1: Schaltbild und Erläuterung zu NMOS und PMOS [1]

Ein MOSFET ist ein aktives Bauelement mit drei Anschlüssen (Elektroden), die mit Gate(G), Source(S) und Drain(D) bezeichnet werden.

#### NMOS Transistor

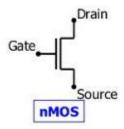

Der NMOS basiert auf einem p-artigen Substrat mit zwei n-artigen Implantationen welche die Source und die Drain Elektrode bilden. Beim NMOS entsprechen Elektronen den Majoritätsladungsträgern. Wenn eine positive Spannung an das Gate angelegt wird, invertiert der Halbleiterbereich unterhalb des Gates und NMOS leitet. Im Gegensatz leitet der NMOS nicht wenn eine niedrige Spannung an das Gate angelegt wird. Der NMOS Transistor gilt als schneller als der PMOS Transistor, da es sich bei den Ladungsträgern im NMOS um Elektronen handelt, welche eine zwei bis drei Mal so hohe Ladungsträgerbeweglichkeit als Löcher besitzen. Das Schaltsymbol des NMOS Transistors ist in Abbildung 3.2 dargestellt und deutet an, dass die Gate Elektrode durch ein Oxyd vom Transistorkanal isoliert ist.

Abbildung 3.2: NMOS Transistor [1]

#### PMOS Transistor

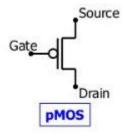

Für die Implementierung eines p-Kanal-MOSFET im gleichen Substrat mit NMOS Transistoren wird zuerst die Implantation einer tiefen N-Wanne benötigt. In diese N-Wanne werden zwei p-artige Implantationen als Source und Drain Elektrode eingebracht. Wenn eine hohe Spannung an das Gate angelegt wird, ist der PMOS nicht leitend, während bei einer niedrigen Spannung am Gate der Halbleiter unterhalb der Gate-Elektrode von n- zu p-Typ invertiert und leitend wird. Auf Grund der N-Wanne sind PMOS Transistoren durch einen in Sperrrichtung betriebenen pn-Übergang vom globalen Substrat isoliert und sind damit störunempfindlicher als NMOS Transistoren. In Abbildung 3.3 ist das Schaltsymbol des PMOS Transistors dargestellt. Auch beim PMOS Transistor ist die Gate-Elektrode durch ein Oxyd vom Transistorkanal isoliert, was durch das Schaltsymbol zum Ausdruck gebracht wird. Darüber hinaus wird die zum NMOS inverse Ansteuerung durch einen kleinen Kreis am Gate verdeutlicht.

Abbildung 3.3: PMOS Transistor [1]

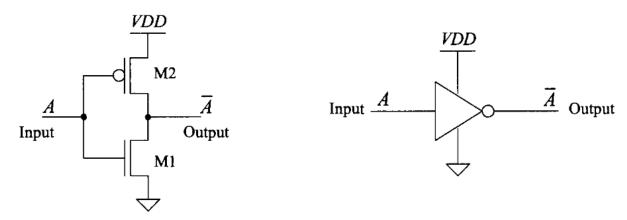

Das Konzept der CMOS Schaltungstechnik ist in der Abbildung 3.4 am Beispiel einer Inverterschaltung dargestellt. Bei der Inverterschaltung wird das Eingangssignal (Input) mit den Gate-Elektroden beider Transistoren verbunden, um den Transistor eines Typs einzuschalten und den des anderen Typs auszuschalten. Dementsprechend ist immer nur ein Transistor geöffnet und der andere geschlossen. Darüber hinaus fließen keine dauerhaften Ströme in die Gate-Elektroden der verwendeten Transistoren, da diese vom Kanal des Transistors isoliert sind. Diese Eigenschaft ermöglicht die Konstruktion von

Logikbausteinen ohne, bzw. mit nur sehr geringer statischer Stromaufnahme, bei denen die MOS Transistoren als einfache Schalter abstrahiert werden können.

Abbildung 3.4: Der Schaltplan vom CMOS Inverter, Inverter-Symbol [2]

n-Kanal Transistor (M1):

Der n-Kanal Transistor leitet, wenn am Gate eine hohe Spannung bzw. eine logische "1" anliegt. Er sperrt, wenn am Gate eine niedrige Spannung bzw. eine logische "0" anliegt. p-Kanal Transistor (M2):

Der p-Kanal Transistor verhält sich genau komplementär zum n-Kanal Transistor. Er leitet, wenn an seinem Gate eine niedrige Spannung bzw. eine logische "0" anliegt und sperrt bei einer hohen Spannung bzw. einer logischen "1" am Gate.

CMOS bietet eine relativ hohe Geschwindigkeit, geringe Verlustleistung, hohe Rauschgrenzen in beiden Zuständen und arbeitet über einen großen Bereich von Quell- und Eingangsspannungen. Zum besseren Verständnis des ergänzenden Metalloxid-Halbleiter-Arbeitsprinzips wird das CMOS-Logikgatter nachfolgend in Kapitel 4 erläutert.

## 4 Komponentenbeschreibungen der CMOS Gatter

Für die Implementierung des Treibers werden CMOS-Logikgatter verwendet, welche durch die entsprechende Verschaltung, die geforderte Logikfunktion für die Schaltung der Leistungstransistoren generieren. Diese benötigten Logikgatter werden im Folgenden vorgestellt.

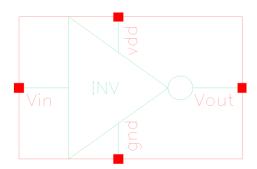

#### 4.1 CMOS Inverter-Gatter

Allgemein hat ein Inverter-Gatter die Funktion ein Logiksignal zu invertieren, d. h. aus einer logischen "1" eine logische "0" und umgekehrt zu erzeugen. Das Logiksymbol des Inverters besteht, wie in Abbildung 4.1 dargestellt, aus einem Dreieck mit einem kleinen Kreis am Ausgang. Der Kreis soll dabei die invertierende Wirkung des Gatters verdeutlichen.

Abbildung 4.1: Inverter-Symbol

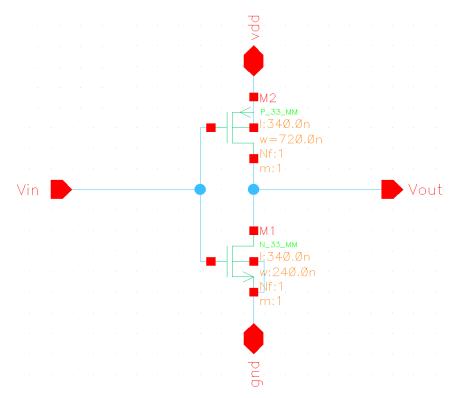

Wie in Abbildung 4.2 dargestellt, wird ein Inverter in CMOS-Technologie mithilfe eines PMOS-Transistors (M2) und eines NMOS-Transistors(W1) implementiert. Die Gates und die Drains beider Transistoren sind jeweils miteinander verbunden, während die Source des PMOS Transistors mit der Versorgungsspannung (VDD) und die Source des NMOS Transistors mit Masse (GND) verbunden ist.

Abbildung 4.2: Schaltplan CMOS-Inverter-Gatter [3]

Für eine Eingangsspannungspegel von "1" (VDD) sperrt der p-Kanal-Transistor und der n-Kanal Transistor leitet. In Folge gibt es eine leitende Verbindung zwischen dem Gatterausgang Vout und Masse (GND). Es stellt sich damit eine Spannung am Ausgang von 0 V ein, was dem Logikpegel "0" entspricht. Bei einer "0" am Eingang leitet der p-Kanal Transistor und der n-Kanal Transistor sperrt. Der Ausgang (Vout) wird also über den p-Kanal Transistor mit (VDD) verbunden, wodurch sich ein Ausgangspegel "1" einstellt.

| Funktion |      |      |      |     |  |  |

|----------|------|------|------|-----|--|--|

| ln       | U(V) | PMOS | NMOS | Out |  |  |

| 0        | 0    | L    | S    | 1   |  |  |

| 1        | 3.3  | S    | L    | 0   |  |  |

Tabelle 4.1: Wahrheitstabelle Inverter-Gatter

In Tabelle 4.1 ist die Wahrheitstabelle des Inverters dargestellt, wobei die Angabe "S" für "sperrt" und die Angabe "L" für "leitet" steht. Wie der Wahrheitstabelle zu entnehmen ist, leitet entweder der PMOS oder der NMOS, während der jeweils andere Transistor gesperrt ist.

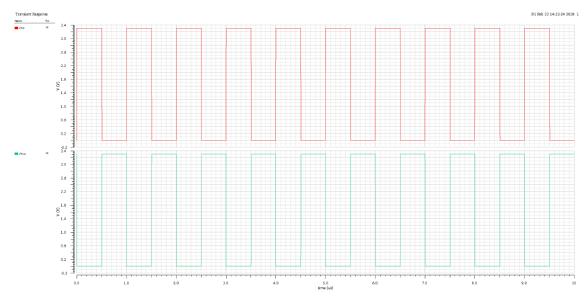

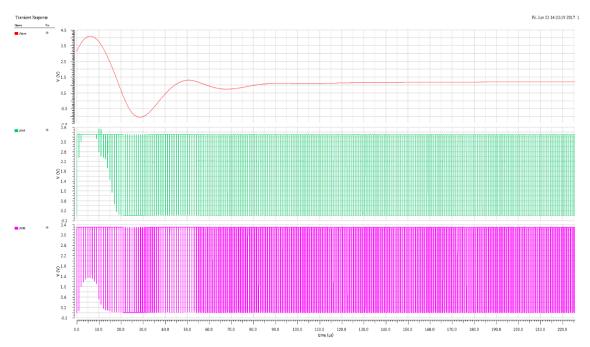

Im Folgenden ist eine transiente Simulation des Schaltverhaltens des Inverters bei nominalen Bedingungen, d. h. dem typischen Prozesscorner, Raumtemperatur und einer Versorgungsspannung von 3.3 V dargestellt.

Abbildung 4.3: INV-Gatter Simulation Ergebnisse

Das Eingangssignal (rote Kurve im oberen Teil der Abbildung) ist eine Rechtschwingung mit einer Periode von 1 µs. Am Ausgang entsteht eine exakt invertierte Schwingung mit derselben Periode (grüne Kurve).

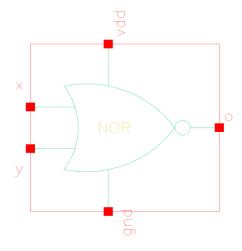

#### 4.2 CMOS NOR-Gatter

In diesem Abschnitt wird das NOR-Gatter vorgestellt. Das NOR-Gatter führt eine Oder-Logikfunktion mit anschließender Invertierung durch. Die NOR-Funktion ist unter Verwendung der CMOS-Technologie leichter zu implementieren als die OR-Funktion. Daher wird für den Fall, dass eine OR-Funktionalität benötigt wird, dies durch ein NOR-Gatter und einen nachgeschalteten Inverter realisiert. Das Symbol des NOR-Gatters ist in Abbildung 4.4 dargestellt. Das Symbol zeichnet sich durch die runde Eingangsseite und die spitze Ausgangsseite aus. Des Weiteren besitzt auch das NOR Gatter einen kleinen Kreis am Ausgang, was auf die invertierende Funktion des Gatters hinweist.

Abbildung 4.4: NOR-Gatter Symbol

Die Schaltung besteht aus zwei in Reihe geschalteten PMOS Transistoren und zwei parallel geschalteten NMOS Transistoren. Durch jeden der beiden Eingänge wird jeweils ein PMOS und ein NMOS geschaltet. Wenn zumindest einer der beiden Eingänge auf logisch "1" ist, wird infolge der Sperrung des zugehörigen PMOS die Verbindung des Ausgangs o zur Spannungsversorgung (VDD) unterbrochen. Gleichzeitig ist zumindest einer der NMOS leitend, sodass der Ausgang mit Masse (GND) verbunden ist. Nur wenn beide Eingänge auf logisch "0" liegen, sind beide PMOS leitend und dadurch der Ausgang mit der Versorgungsspannung verbunden. In diesem Fall sind beide NMOS Transistoren geöffnet, sodass sich eine logische "1" am Ausgang ergibt.

Abbildung 4.5: Schematic NOR-Gatter

Die Wahrheitstabelle der Schaltfunktion ist in Tabelle 4.2 dargestellt. Wird die Spalte des Ausgangssignals invertiert, ergibt sich für alle Signalkombinationen bis auf die, bei der beide Eingangssignale auf "0" liegen eine logische Eins. Dies entspricht dem Verhalten der Oder-Logikfunktion.

|        | Funktion                                    |   |   |   |   |   |   |   |  |

|--------|---------------------------------------------|---|---|---|---|---|---|---|--|

| Ux [V] | Ux [V] Uy [V] NMOS3 NMOS4 PMOS1 PMOS2 x y o |   |   |   |   |   |   |   |  |

| 0      | 0                                           | S | S | L | L | 0 | 0 | 1 |  |

| 0      | 3.3                                         | S | L | L | S | 0 | 1 | 0 |  |

| 3.3    | 0                                           | L | S | S | L | 1 | 0 | 0 |  |

| 3.3    | 3.3                                         | L | L | S | S | 1 | 1 | 0 |  |

Tabelle 4.2: Wahrheitstabelle NOR-Gatter

In der Folgenden Abbildung 4.6 ist eine transiente Simulation des Schaltverhaltens des NOR-Gatters bei nominalen Bedingungen, d. h. dem typischen Prozesscorner, Raumtemperatur und einer Versorgungsspannung von 3.3 V dargestellt. Am Eingang x liegt eine Rechteckschwingung mit einer Periode 20 ns (rote Kurve) und am Eingang y eine gleichartige Schwingung mit 15 ns (grüne Kurve) an.

Abbildung 4.6: NOR-Gatter Simulation Ergebnisse

Der Simulation ist zu entnehmen, dass der Ausgang (violette Kurve) nur dann auf "1" geht, wenn beide Eingangssignale auf "0" liegen.

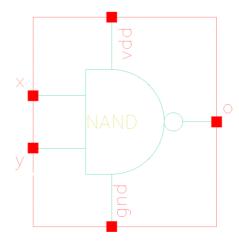

#### 4.3 CMOS NAND-Gatter Funktion

Das NAND Gatter führt eine Und-Logikfunktion mit anschließender Invertierung durch. Ähnlich wie beim NOR-Gatter, ist die NAND-Funktion in der CMOS-Technologie leichter zu implementieren als die AND-Funktion. Daher wird ähnlich wie bei der OR-Funktion

eine AND-Funktionalität erzeugt, indem ein NAND-Gatter mit einem nachgeschalteten Inverter kombiniert wird. Das Symbol des NAND-Gatters ist in Abbildung 4.7 dargestellt. Das Symbol zeichnet sich durch die gerade Eingangsseite und die runde Ausgangsseite aus. Außerdem befindet sich am Ausgang des NAND-Gatters auch wieder ein kleiner Kreis, der auf die invertierende Funktion des Gatters hinweist.

Abbildung 4.7: NAND-Gatter Symbol

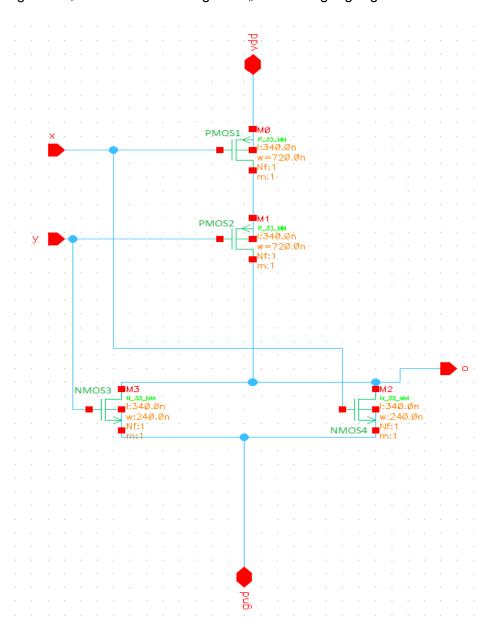

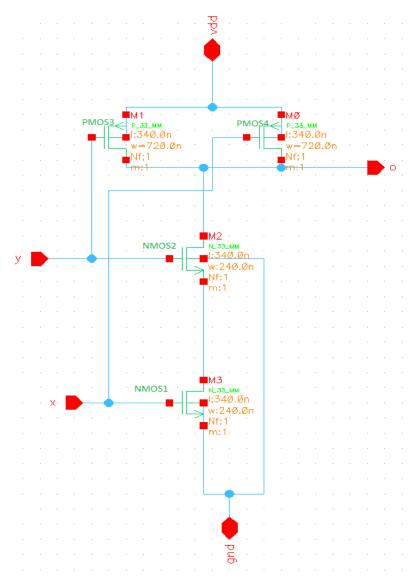

Die Schaltung besteht aus zwei parallel geschalteten PMOS Transistoren und zwei in Reihe geschalteten NMOS Transistoren. Durch die Eingänge x und y wird jeweils ein PMOS und ein NMOS geschaltet (siehe Abbildung 4.8). Liegt an beiden Eingängen eine logische "0" an, werden beide NMOS leitend und der Ausgang ist mit Masse (GND) verbunden, wobei gelichzeitig beide PMOS gesperrt sind. Liegt zumindest ein Eingang auf logisch "1", dann ist zumindest ein NMOS sperrend, sodass die Verbindung des Ausgangs zur Masse unterbrochen ist. Gleichzeitig ist zumindest einer der beiden PMOS leitend, sodass der Ausgang mit der Spannungsversorgung verbunden ist.

Abbildung 4.8: Schaltplan NAND-Gatter [3]

Die Wahrheitstabelle der Schaltfunktion ist in Tabelle 3 dargestellt. Wird die Spalte des Ausgangssignals invertiert, ergibt sich für alle Signalkombinationen bis auf jene, bei der beide Eingangssignale auf "1" liegen eine logische "0". Dies entspricht dem Verhalten der UND-Logikfunktion.

|        | Funktion                                    |   |   |   |   |   |   |   |  |

|--------|---------------------------------------------|---|---|---|---|---|---|---|--|

| Ux [V] | Ux [V] Uy [V] NMOS1 NMOS2 PMOS3 PMOS4 x y o |   |   |   |   |   |   |   |  |

| 0      | 0                                           | S | S | L | L | 0 | 0 | 1 |  |

| 0      | 3.3                                         | S | L | L | S | 0 | 1 | 1 |  |

| 3.3    | 0                                           | L | S | S | L | 1 | 0 | 1 |  |

| 3.3    | 3.3                                         | L | L | S | S | 1 | 1 | 0 |  |

Tabelle 4.3: Wahrheitstabelle NAND-Gatter

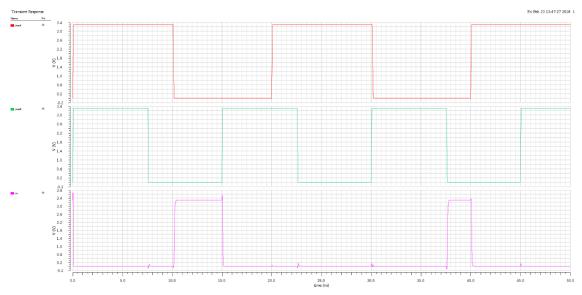

Im Folgenden ist eine transiente Simulation des Schaltverhaltens des NAND Gatters bei nominalen Bedingungen d.h. der typischen Prozesscorner, Raumtemperatur und einer Versorgungsspannung von 3.3V dargestellt. Der Simulation ist zu entnehmen, dass der Ausgang nur dann auf "0" geht, wenn beide Eingangssignale auf "0" liegen.

Abbildung 4.9: NAND-Gatter Simulationsergebnisse

## 5 Entwurf der Schaltung für die Treiberstufe

Die Treiberstufe der Leistungstransistoren im Tiefsetzsteller muss zwei wichtige Funktionen erfüllen. Zum einen muss das Steuersignal so stark verstärkt werden, dass die doppelten Schalttransistoren in einer relativ kurzen Zeit ein- bzw. ausgeschaltet werden können. Hierfür werden üblicherweise Ketten aus Invertern verwendet, deren Treiberstärke zum Ende der Kette, d. h. dem Gate des Schalttransistors, zunimmt. In Abbildung 5.1 und Abbildung 5.2 wird die zunehmende Treiberstärke durch größere Symbole verdeutlicht. Zum anderen hat die Treiberschaltung die Funktion, Kurzschlüsse zwischen der Eingangsspannung und Masse im Schaltmoment zu vermeiden. Hierfür werden zwei verschiedene Schaltungsansätze untersucht.

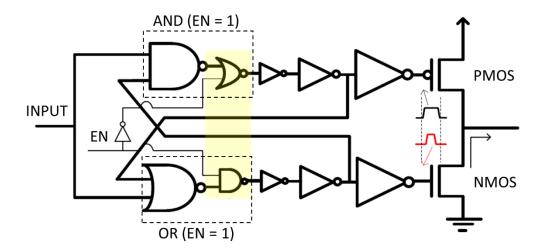

## 5.1 Schaltungsvariante I

Das Konzept der Schaltung ist in Abbildung 5.1 dargestellt. In dieser Schaltung wird das Eingangssignal (Input) gleichzeitig an ein NAND-Gatter mit nachgeschaltetem NOR-Gatter und ein NOR-Gatter mit nachgeschaltetem NAND-Gatter geführt. Die nachgeschalteten Gatter erhalten am zweiten Eingang das Enable-Signal (EN) bzw. dessen Invertierung. Durch dieses Signal wird die Schaltung aktiviert.

Abbildung 5.1: Konzept Treiberschaltung mit interner Totzeit (modifiziert übernommen von [4])

Ist das Signal EN = 0 so sind die Ausgänge der beiden in Abbildung 5.1 gelb markierten Komponenten unabhängig von den Signalen am Eingang der ersten Gatter bei "0" (NAND-NOR) bzw. "1" (NOR-NAND). Dementsprechend ist die Gate-Spannung am PMOS auf "high" und am NMOS auf "low", d. h. beide Transistoren sind sperrend. Wenn

die Schaltung aktiviert wird (EN = 1), dann hat die NAND-NOR-Kombination die Funktion eines AND-Gatters und die NOR-NAND-Kombination bildet ein OR-Gatter ab.

Durch die Rückführung des zweimal invertierten Ausgangssignals zum Eingang des jeweils anderen Gatters wird eine Schaltverzögerung erreicht. Ist beispielsweise das Eingangssignal ein logische "0" ergibt sich sowohl am Ausgang der OR-Schaltung als auch am Ausgang der AND-Schaltung eine logische "0". Nach mehrstufiger Verstärkung und Invertierung sind dementsprechend beide Gate-Spannungen auf "high", d. h. der NMOS leitet und der PMOS sperrt. Ändert sich das Eingangssignal in Richtung logischer "1", d. h. erscheint eine positive Flanke im Eingangssignal, hat das zunächst keine Wirkung auf den Ausgang des AND-Gatters. Hingegen ändert sich unmittelbar der Ausgang des OR-Gatters auf "1", was eine Sperrung des NMOS nach sich zieht. Erst nachdem diese logische "1" zweifach invertiert bzw. verstärkt und zurückgeführt wurde, kommt es zu einer Änderung des zweiten Eingangs des AND-Gatters. Dies hat dann zur Folge, dass sich dessen Ausgang ebenfalls auf "1" ändert und dementsprechend der PMOS leitend wird.

Ein analoger Ablauf ergibt sich wenn sich das Eingangssignal von "1" auf "0" ändert. Zunächst ändert sich nur der Ausgang des AND-Gatters und dementsprechend der Schaltzustand des PMOS. Erst nachdem dieses geänderte Signal an das OR-Gatter zurückgeführt worden ist, ändert sich dessen Ausgangssignal und der NMOS wird auf leitend gestellt. Die Verzögerungszeit zwischen den beiden Schaltvorgängen ist dieselbe wie im zuvor beschriebenen Fall. Somit bewirkt diese Schaltung, dass zwischen den Schaltzuständen, bei denen jeweils einer der gesteuerten MOSFETs leitet und einer sperrt, für eine bestimmte Übergangsphase beide Transistoren auf sperrend gestellt werden. Dadurch werden Kurzschlüsse infolge von gleichzeitiger Leitung der beiden gesteuerten Transistoren wirksam unterbunden.

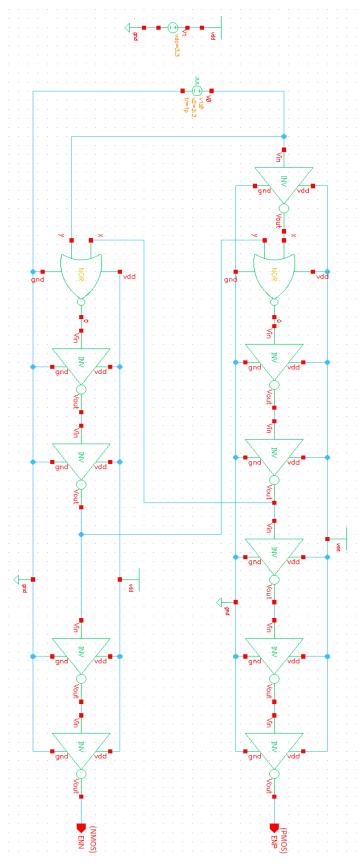

In Abbildung 5.2 ist der tatsächliche Aufbau der Schaltung zu sehen, wie er in den Tiefsetzsteller eingebaut werden soll. Die Schaltung besteht aus einer Kette aus fünf Invertern im oberen und unteren Signalpfad, welche jeweils eine erhöhte Treiberstärke durch die Parallelschaltung von mehreren Invertern besitzen. Oben von links nach rechts gesehen sind 9, 27, 243 und 2187 Gatter parallelgeschaltet. Unten von links nach rechts gesehen sind 3, 9, 81 und 729 Gatter parallelgeschaltet.

Abbildung 5.2: Umsetzung der Schaltungsvariante I [3]

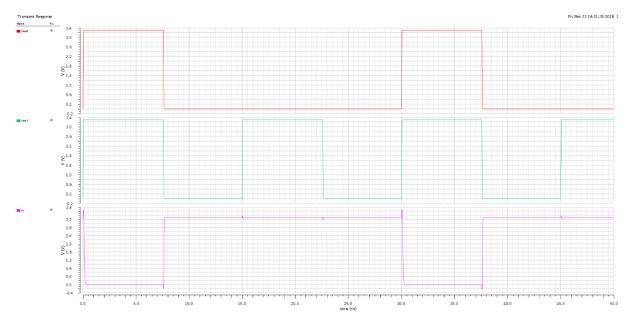

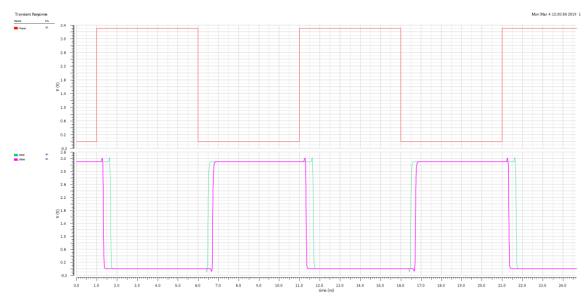

Die Parallelschaltung von Invertern dient dazu, die Treiberstärke zu erhöhen. Durch die serielle Verschaltung der Inverter ergibt sich eine Optimierung der Leistungsaufnahme für die gewünschte Treiberstärke und führt eine Schaltverzögerung ein. Die Zielsetzung bei der Wahl der Verzögerungszeiten besteht darin, bei beiden Schaltvorgängen, d. h. sowohl für eine positive Flanke ("0"  $\rightarrow$  "1") als auch für eine negative Flanke ("1"  $\rightarrow$  "0"), am Eingangssignal dieselbe Verzögerungszeit zwischen den beiden Ausgangssignalen der Treiberstufe zu erhalten. Die dargestellte Schaltung ist das Ergebnis einer schrittweisen Verbesserung des Treibers anhand von Simulationen für das Schaltverhalten. Das Simulationsergebnis ist in Abbildung 5.3 dargestellt. Simuliert wurde das Schaltungsverhalten bei der Nominaltemperatur von 27°C, wenn am Eingang eine Rechteckschwingung zwischen 0 V und der Versorgungsspannung VDD = 3,3 V anliegt.

Abbildung 5.3: Simulation Schaltungsvariante I

Im oberen Teil sind das konstante Enable-Signal mit EN = 1 (rot) und das variierende Input-Signal (grün) zu sehen. Das simulierte transiente Verhalten der Schaltung wird anhand der Gate-Spannungen für PMOS (ENP in magenta) und NMOS (ENN in blau) im unteren Teil angezeigt. Es ist zu erkennen, dass beim Wechsel des Inputs von "1" nach "0" zuerst ENP ansteigt und erst anschließend ENN auf "1" geht, was dazu führt, dass erst der PMOS Transistor geöffnet wird, bevor der NMOS Transistor geschlossen wird. Beim Wechsel des Inputs von "0" nach "1" ergibt sich ein umgekehrtes Verhalten. Erst fällt ENN ab und danach ENP, d. h. der NMOS wird geöffnet, bevor der PMOS geschlossen wird. Infolge dieser beiden Verzögerungen sind die Impulse des ENP-Signals breiter als jene des ENN-Signals.

Eine wichtige Größe bei der Bewertung des Treibers ist die Anstiegs- und Abfallzeit der Ausgangssignale. Die Anstiegszeit  $t_r$  (rise time) und Abfallzeit  $t_f$  (fall time) definieren

sich als die Zeit, die beim Übergang von 10 % auf 90 % der maximalen Signalamplitude verstreicht. Die simulierten Werte für diese beiden Zeiten sind in Tabelle 5.1 zusammengefasst.

|       | ENN      | ENP      |

|-------|----------|----------|

| $t_r$ | 2,576 ns | 2,555 ns |

| $t_f$ | 2,654 ns | 2,599 ns |

Tabelle 5.1: Anstiegs- und Abfallzeiten für Schaltungsvariante I

Eine weitere wichtige Treibereigenschaft ist die Verzögerungszeit zwischen den Ausgangssignalen der Treiberschaltung, welche die beiden LeistungsMOSFETs. Für die sichere Öffnung des jeweils geschlossenen Schalters ist eine ausreichende zeitliche Verzögerung zum Schließen des geöffneten Schalters notwendig. Die Verzögerungszeit berechnet sich aus der Differenz zwischen den Zeitpunkten, an denen die jeweiligen Signale auf 50 % ihres Maximalwertes angestiegen bzw. abgefallen sind.

Die Zeitverzögerung zwischen dem PMOS-Steuersignal zum NMOS-Steuersignal bei steigender Flanke des Inputsignals liegt bei 1.33ns. Die Zeitverzögerung zwischen dem PMOS- und NMOS-Steuersignal bei der fallenden Flanke liegt bei 1.556ns.

## 5.2 Schaltungsvariante II

Das zweite Schaltungskonzept welches im Hinblick auf seine Eignung untersucht wird, kommt ohne ein eigenes Steuersignal für die Aktivierung der Schaltung aus. Dadurch vereinfacht sich die Schaltung auf zwei NOR-Gatter mit jeweils zwei nachgeschalteten Invertern. Hierbei wird das Input-Signal zum NOR-Gatter, welches den PMOS steuert, zusätzlich invertiert. (siehe Abbildung 5.4).

Abbildung 5.4: Konzept Schaltung II [5]

Zu beachten ist, dass im stationären Zustand die Ausgänge der beiden NOR-Gatter unterschiedliche logische Werte aufweisen. Liegt beispielsweise der Input auf "0" ist im

stationären Zustand der Ausgang des oberen Gatters auf "0" und jener des unteren Gatters auf "1". Im Fall das Input den Wert "1" annimmt, gehen beide Ausgänge in den jeweils zum vorherigen Zustand invertierten logischen Wert über. Da aber für die Steuerung des Tiefsetzstellers der PMOS und der NMOS das gleiche Signal erhalten müssen, wird eine unterschiedliche Anzahl an Invertern nachgeschaltet. Zwischen dem oberen NOR-Gatter und dem PMOS ist eine ungerade Anzahl Inverter platziert, während sich zwischen dem unteren NOR-Gatter und dem durch ihn geschalteten NMOS eine gerade Anzahl an Invertern befindet.

Wie in Schaltungsvariante I wird das Ausgangssignal über eine gerade Anzahl an Invertern geleitet und anschließend zum jeweils anderen Gatter zurückgeführt. Dadurch ergibt sich die gewünschte Schaltverzögerung zwischen dem Schließen des einen MOSFET-Schalters und dem Öffnen des anderen. Die Funktionsweise ähnelt stark der Schaltungsvariante I. Ist der Input beispielsweise auf "0" und ändert sich auf "1", so ändert sich der zugehörige Eingang des oberen NOR-Gatters von "0" auf "1", der andere Eingang erhält noch das "alte" Ausgangsignal des unteren NOR-Gatters, welcher wie bereits erwähnt eine "1" ist. Somit ändert sich am Ausgang des oberen Gatters zunächst nichts und der PMOS bleibt gesperrt. Im Gegensatz dazu führt die Änderung des Inputs von "0" nach "1" am unteren NOR-Gatter unmittelbar zur Änderung des Ausgangs von "1" nach "0", wodurch der NMOS gesperrt wird. Erst nach der Rückführung dieses Ausgangssignals an das obere NOR-Gatter ändert sich dessen Ausgang und der PMOS wird leitend.

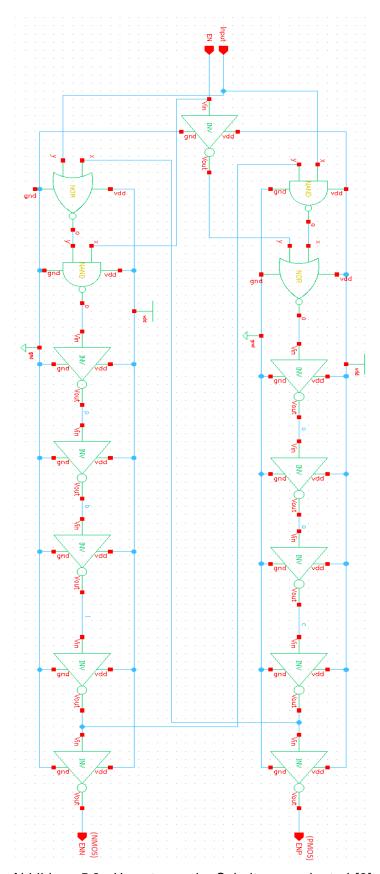

In Abbildung 5.2 ist der tatsächliche Aufbau der Schaltung zu sehen, wie er in den Tiefsetzsteller eingebaut werden soll. Die Schaltung besteht aus zwei NOR-Gattern und zwei Inverterketten, wobei die Inverterkette im PMOS Pfad aus drei Invertern und die Inverterkette im NMOS Pfad aus zwei Invertern besteht.

Abbildung 5.5: Die zweite vorgeschlagene Schaltung des Treibers [3]

In der nachfolgenden Abbildung 5.6 sind die Simulationsergebnisse für diese Schaltungsvariante II dargestellt. Das Eingangssignal entspricht einer Rechteckschwingung mit einer Periodendauer von 10ns (rote Kurve). Im unteren Teil sind die Steuersignale ENN für den NMOS (violet) und ENP für den PMOS-Transistor (grün) dargestellt.

Abbildung 5.6: Simulation Schaltungsvariante II

Prinzipiell ist ein ähnlicher Verlauf wie bei Schaltungsvariante I zu erkennen, d. h. die Schaltimpulse für den PMOS sind breiter als jene für den NMOS. Im Unterschied zur Schaltungsvariante I zeigen sich jedoch bei der Schaltungsvariante II kürzere An- und Abfallzeiten, die darauf zurückzuführen sind, dass weniger Bauelemente zwischen Einund Ausgang der Schaltung in Reihe geschaltet sind.

|       | ENN       | ENP       |

|-------|-----------|-----------|

| $t_r$ | 6,764 ns  | 6,532 ns  |

| $t_f$ | 11,307 ns | 11,662 ns |

Tabelle 5.2: Anstiegs- und Abfallzeiten für Schaltungsvariante II

Jedoch beträgt die Verzögerung zwischen der steigenden Flanke von ENP und ENN bei nominalen Bedingungen von 0.207ns während sich die Verzögerung zwischen der fallenden Flanke der Signale ENN und ENP auf 0.343ns beläuft.

Prinzipiell ist diese Schaltung zwar auch geeignet Kurzschlüsse zu unterbinden, jedoch ist sie wegen der ausgeprägten Asymmetrie in den Schaltverzögerungen weniger geeignet als die Schaltungsvariante I. Daher wird für die weitere Entwicklung der Schaltung die erste Variante verwendet.

## 6 Integration der Treiberstufe im Tiefsetzsteller

Die im Kapitel 5 entwickelte Treiberstufe bildet die Grundlage für die im Tiefsetzsteller verwendete Schaltung, dessen Funktion in diesem Kapitel validiert wird. Zunächst wird die Funktion der Treiberschaltung über den Bereich möglicher Betriebsbedingungen simulatorisch verifiziert. Anschließend erfolgt die Integration der Treiberstufer in die Schaltung des Tiefsetzstellers und die Simulation der Gesamtschaltung.

#### 6.1 PVT-Simulation der Treiberstufe

In den bisherigen Simulationen wurde die Treiberstufe nur bei Standardbedingungen untersucht. In der Praxis wird sie unter Umständen mit deutlich abweichenden Betriebsbedingungen konfrontiert. Um ihre ordnungsgemäße Funktion, für diese Fälle zu verifizieren, wird eine sog. PVT-Simulation durchgeführt, bei der die Prozesscorner (P), die Versorgungsspannung (V für engl. Voltage) und die Betriebstemperatur (T) variiert werden. Für die Analyse werden dabei jeweils im Wesentlichen die extremen Abweichungen sowie zum Vergleich die Standartwerte betrachtet.

Die Process Corner beschreibt die infolge von Variationen in der Fertigung auftretenden Abweichungen in der Schaltgeschwindigkeit der MOSFETs. Betrachtetet werden die Fälle:

- 1. tt (typical-typical): typischer PMOS und typischer NMOS

- 2. ss (slow-slow): langsamer PMOS und langsamer NMOS

- 3. ff (fast- fast): schneller PMOS und schneller NMOS

Für die Temperatur wird eine Variation zwischen -40°C und 160°C angenommen, d.h. es werden folgende Temperaturen betrachtet:

1. Minimaltemperatur: -40°C

2. Standradtemperatur: 27°C

3. Maximaltemperatur: 160°C

Für die Versorgungsspannung wird der Bereich zwischen 2,0 V und 3,3 V genutzt. Betrachtet werden Minimal-, Maximal- und Mittelwert. Somit ergeben sich die Fälle:

1. Minimale Versorgungsspannung: 2,0 V

Mittlere Versorgungsspannung: 2,65 V

Maximale Versorgungsspannung: 3,3 V

Die vollständigen Ergebnisse der PVT-Simulation sind in Tabelle 6.1 zusammengestellt. Die Simulationsergebnisse des typischen Falles sind in Tabelle 6.2 gelistet, während die Ergebnisse des schnellsten bzw. langsamsten Falles in Tabelle 6.3 zu finden sind.

| Corner | mm180_reg33_v114.lib.scs | temperature | ∨dd △  | tr_P   | tr_N   | tf_N   | tf_P   | td_r   | td_f   |

|--------|--------------------------|-------------|--------|--------|--------|--------|--------|--------|--------|

| C0_0   | ff                       | -40         | 2      | 3.137n | 3.151n | 3.141n | 2.84n  | 1.637n | 1.856n |

| C0_1   | ff                       | 27          | 2      | 3.672n | 3.722n | 3.529n | 3.186n | 1.92n  | 2.15n  |

| C0_2   | ff                       | 160         | 2      | 4.686n | 4.797n | 4.353n | 4.023n | 2.472n | 2.72n  |

| C0_27  | ss                       | -40         | 2      | 4.596n | 4.633n | 2.733n | 3.744n | 2.11n  | 1.928n |

| C0_28  | ss                       | 27          | 2      | 5.407n | 5.541n | 3.179n | 4.3n   | 2.522n | 2.625n |

| C0_29  | SS                       | 160         | 2      | 6.928n | 7.172n | 6.106n | 5.556n | 3.321n | 3.7n   |

| C0_36  | tt                       | -40         | 2      | 3.703n | 3.692n | 2.329n | 3.153n | 1.84n  | 1.999n |

| C0_37  | tt                       | 27          | 2      | 4.345n | 4.395n | 2.698n | 3.612n | 2.177n | 2.428n |

| C0_38  | tt                       | 160         | 2      | 5.544n | 5.691n | 5.025n | 4.575n | 2.832n | 3.127n |

| C0_3   | ff                       | -40         | 2.65   | 2.307n | 2.348n | 2.409n | 2.386n | 1.241n | 1.451n |

| C0_4   | ff                       | 27          | 2.65   | 2.701n | 2.736n | 2.712n | 2.646n | 1.443n | 1.655n |

| C0_5   | ff                       | 160         | 2.65   | 3.45n  | 3.433n | 3.47n  | 3.275n | 1.84n  | 2.086n |

| C0_30  | SS                       | -40         | 2.65   | 3.096n | 3.182n | 3.01n  | 2.951n | 1.511n | 1.768n |

| C0_31  | ss                       | 27          | 2.65   | 3.687n | 3.782n | 3.437n | 3.363n | 1.794n | 2.069n |

| C0_32  | ss                       | 160         | 2.65   | 4.805n | 4.915n | 4.435n | 4.328n | 2.364n | 2.691n |

| C0_39  | tt                       | -40         | 2.65   | 2.601n | 2.654n | 2.626n | 2.585n | 1.355n | 1.58n  |

| C0_40  | tt                       | 27          | 2.65   | 3.073n | 3.139n | 2.974n | 2.903n | 1.589n | 1.823n |

| C0_41  | tt                       | 160         | 2.65   | 3.961n | 3.989n | 3.818n | 3.666n | 2.06n  | 2.332n |

| C0_6   | ff                       | -40         | 3.3    | 2.003n | 2.007n | 2.201n | 2.194n | 1.076n | 1.281n |

| C0_7   | ff                       | 27          | 3      | 2.31n  | 2.313n | 2.459n | 2.408n | 1.23n  | 1.44n  |

| C0_8   | ff                       | 160         | 3 poin | 2.82n  | 2.77n  | 3.108n | 2.954n | 1.525n | 1.782n |

| C0_33  | ss                       | -40         | 3.3    | 2.543n | 2.585n | 2.588n | 2.649n | 1.26n  | 1.501n |

| C0_34  | ss                       | 27          | 3.3    | 2.996n | 3.048n | 2.941n | 2.95n  | 1.474n | 1.73n  |

| C0_35  | SS                       | 160         | 3.3    | 3.809n | 3.803n | 3.827n | 3.76n  | 1.901n | 2.219n |

| C0_42  | tt                       | -40         | 3.3    | 2.194n | 2.226n | 2.325n | 2.337n | 1.151n | 1.368n |

| C0_43  | tt                       | 27          | 3.3    | 2.555n | 2.576n | 2.624n | 2.599n | 1.33n  | 1.556n |

| C0_44  | tt                       | 160         | 3.3    | 3.189n | 3.169n | 3.363n | 3.234n | 1.682n | 1.959n |

Tabelle 6.1: Ergebnisse PVT-Simulation der Treiberstufe

Zur besseren Übersicht sind die Werte für Standardspannung und -temperatur für die verschiedenen Process Corners in Tabelle 6.2 zusammengefasst.

| Vdd = 3.3V                  | Process Corner |       |       |  |  |

|-----------------------------|----------------|-------|-------|--|--|

| T = 27°C                    | ff             | tt    | SS    |  |  |

| t <sub>r,PMOS</sub> [ns]    | 2.310          | 2.555 | 2.996 |  |  |

| $t_{r,NMOS}$ [ns]           | 2.313          | 2.576 | 3.048 |  |  |

| t <sub>f,PMOS</sub> [ns]    | 2.408          | 2.624 | 2.941 |  |  |

| t <sub>f,NMOS</sub> [ns]    | 2.459          | 2.599 | 2.950 |  |  |

| <i>t<sub>d,r</sub></i> [ns] | 1.230          | 1.330 | 1.474 |  |  |

| t <sub>d,f</sub> [ns]       | 1.440          | 1.556 | 1.730 |  |  |

Tabelle 6.2: Simulierte Zeiten bei Standardbetriebsbedingungen

Durch die Variation im Process Corner ändern sich die Werte für die jeweiligen Anstiegsund Abfallszeiten sowie Verzögerungszeit zwischen den Schaltvorgängen um 10 bis 15 %. Somit sind die Veränderungen gering und haben keine wesentliche Auswirkung auf die Funktionsfähigkeit des Treibers. Das sich die Verzögerungszeit analog zu Abstiegs- bzw. Abfallzeiten ändert, ist die Sicherheit vor Kurzschlüssen auch bei den betrachteten Variationen gegeben. Die Änderungen von Temperatur und Versorgungspannung wirken sich so aus, dass mit steigender Temperatur und sinkender Versorgungsspannung die Schaltzeiten der MOS-FETs zunehmen. Somit ergeben sich unter Berücksichtigung der Process Corners ein Minimal- und ein Maximalfall für die Schaltzeiten. Die für diese beiden Fälle simulierten Werte sind in Tabelle 6.3 zusammengefasst.

|                              | Min                | Max                |

|------------------------------|--------------------|--------------------|

|                              | (ff, -40°C, 3,3 V) | (ss, 160°C, 2,0 V) |

| t <sub>r,PMOS</sub> [ns]     | 2.003              | 6.982              |

| $t_{r,NMOS}$ [ns]            | 2.007              | 7.172              |

| t <sub>f,PMOS</sub> [ns]     | 2.201              | 6.106              |

| t <sub>f,NMOS</sub> [ns]     | 2.194              | 5.556              |

| <i>t</i> <sub>d,r</sub> [ns] | 1.076              | 3.321              |

| t <sub>d,f</sub> [ns]        | 1.281              | 3.700              |

Tabelle 6.3: Simulierte Zeiten bei Minimal- und Maximalbedingungen

Hier ergeben sich deutlich stärkere Abweichungen vom typischen Betriebsverhalten der Treiberstufe. Im ungünstigsten Fall sind die Anstiegs- bzw. Abfallzeiten mehr als doppelt so hoch wie im Standardfall, allerdings immer noch geringer als 10 ns und somit deutlich kleiner als die geplante Schaltperiode von 1 µs. Außerdem ist in beiden betrachteten Fällen die Verzögerungszeit ausreichend hoch, um Kurzschlüsse zu vermeiden. Somit sind die Transistoren der Treiberstufe ausreichend dimensioniert.

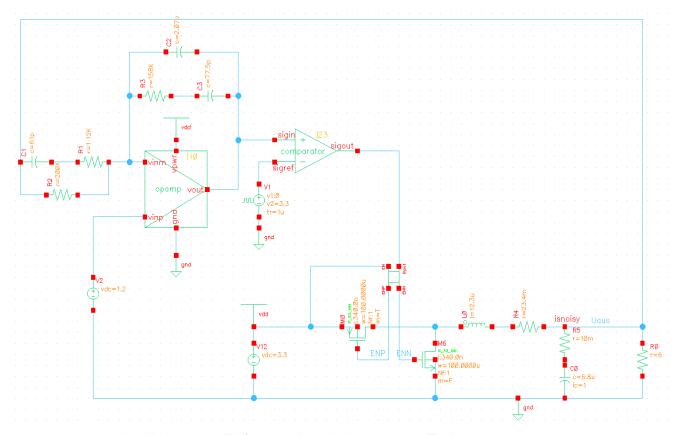

#### 6.2 Hauptschaltung des Tiefsetzstellers mit integrierter Treiberstufe

Nachdem die Funktion der entworfenen Treiberstufe erfolgreich verifiziert wurde, kann diese in die bestehende Schaltung für den Tiefsetzsteller integriert und an der vorgesehenen Stelle zwischen dem Komparator und den Leistungsschaltern im Regelkreis des Abwärtswandlers eingefügt werden. Der zugehörige Schaltplan ist in Abbildung 6.1 dargestellt.

Die wesentlichen Elemente der Schaltung wurden bereits in Kapitel 2 erläutert. Das Ausgangsignal des Tiefsetzstellers wir zum PID-Regler zurückgeführt. Dieser ist außerdem mit einer Spannungsquelle mit der Referenzspannung 1,2 V verbunden. Das Ausgangssignal wird weitergeleitet an den Komparator, welcher durch den Vergleich mit dem ebenfalls zugeführten Sägezahnsignal ein pulsweitenmoduliertes Steuersignal für die Treiberstufe generiert.

Die Treiberstufe hat zwei Eingänge: zum einen das o. g. Steuersignal ("Sigout") und zum anderen die Versorgungsspannung von 3,3 V (V12), welches als Enable-Signal für die Aktivierung der Schaltung fungiert (vgl. Kapitel 5.1).

Abbildung 6.1: Tiefsetzsteller mit integriertem Treiber

Die Ausgangssignale ENN und ENP steuern den PMOS bzw. den NMOS, indem sie mit dem Gate des jeweiligen MOSFET verbunden werden.

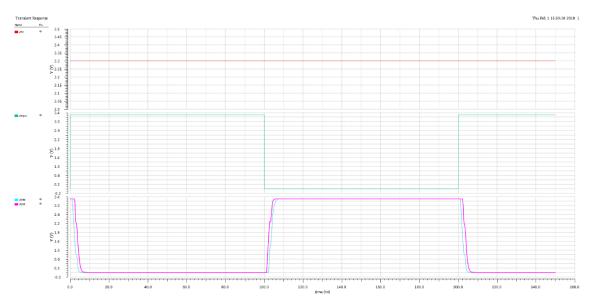

#### 6.3 Simulation des Abwärtswandlers

Abschließend wird das transiente Verhalten des Tiefsetzstellers simuliert, um zu überprüfen ob zum einen die Schaltung wie gewünscht eine Gleichspannung wandelt und zum anderen keine Kurzschlüsse auftreten. Hierzu wird das Verhalten der Schaltung untersucht, wenn durch eine Änderung des Steuersignals die Spannung am Ausgang des Tiefsetzstellers von 3,3 V auf 1,2 V umgestellt werden soll. Die zugehörigen Simulationsergebnisse sind in Abbildung 6.2 dargestellt.

Abbildung 6.2: Simulation des Tiefsetzstellers

Im oberen Teil der Abbildung 6.2 ist die Ausgangspannung des Tiefsetzstellers zu sehen. Es ist gut zu erkennen, dass sich die Spannung innerhalb von etwa 90 µs auf den neuen Ausgangwert einschwingt und dieser danach gehalten wird. Dies belegt die korrekte Steuerung des Tiefsetzstellers durch die Treiberschaltung. Im unteren Teil der Schaltung sind die Steuersignale ENP für den PMOS (grün) und ENN für den NMOS (violett) aufgetragen. Kurzschlüsse treten dabei nicht auf, da anderenfalls ein deutlicher Abfall der Ausgangsspannung auftreten würde. Somit belegt auch diese Simulation, dass die entworfene Treiberschaltung den Anforderungen entspricht.

7 Layout 29

## 7 Layout

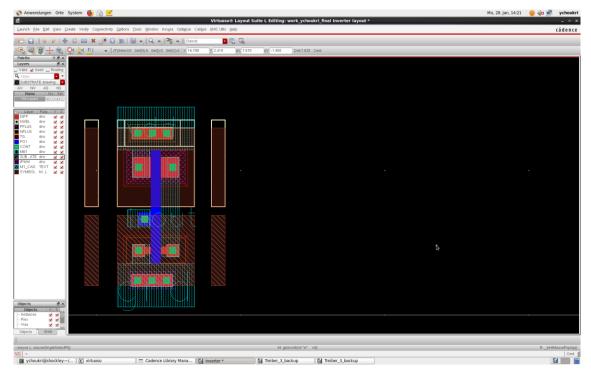

Nachdem der Schaltplan für die Treiberschaltung entworfen wurde und die Schaltung durch Simulationen auf ihre Funktion überprüft wurde, folgt im nächsten Schritt die Erstellung des Layouts. Für diese Tätigkeit wird ebenso wie für den Entwurf und die Simulation der Schaltung die Software Virtuoso verwendet.

Grundlage für das Layout bildet die in Abbildung 5.2 dargestellt Schaltung. Diese besteht neben den NAND-NOR-Gatterkombinationen, aus insgesamt 3290 Invertern. Da die komplette Erstellung des Layouts in einem Schritt für eine derart umfangreiche Schaltung wegen des hohen Aufwandes für die Suche von Fehlern unpraktikabel ist, wird die Schaltung in mehrere Teile zerlegt. Diese Teile werden separat entworfen und dann sukzessive zusammengefügt. Virtuoso unterstützt diese Vorgehensweise durch die Option einzelne Zellen mit einzelnen Teilen der Schaltung anzulegen.

Beim Entwurf des Layouts geht es im Wesentlichen darum, ein möglichst kompaktes Layout zu erstellen, wobei gleichzeitig diverse Designregeln der Prozesstechnologie, wie beispielsweise Mindestabstände oder Mindestflächen eingehalten werden müssen. Die Vorgehensweise bei der Erstellung eines Layouts gliedert sich somit im Wesentlichen in die Phasen:

- Platzierung der Bauelemente

- Erstellung der Verbindungen zwischen den Bauelementen und

- Überprüfung des Layouts.

Auf diese Weise werden die einzelnen Zellen erstellt. Danach werden die einzelnen Zellen zu größeren Zellen kombiniert, verbunden und überprüft. Dieses Verfahren wird sukzessive fortgesetzt bis sich das vollständige Layout ergibt. Im Folgenden wird beispielhaft anhand der Erstellung des Layouts für einen Inverter die Vorgehensweise unter Virtuoso erläutert. Anschließend werden die Layouts für die anderen Einzelzellen erläutert und die Erstellung des Gesamtlayouts beschrieben.

## 7.1 Layout-Erstellung für einen Inverter

#### 7.1.1 Erstellung einer Zelle

Die Erstellung eines Layouts in Virtuoso beginnt mit dem Öffnen einer neuen Layout-Ansicht. Hierzu ist in der Menüleiste *File* $\rightarrow$ *New* $\rightarrow$ *Cellview* auszuwählen. Es öffnet sich ein Dialogfenster (siehe Abbildung 7.1), indem verschiedenen Vorgaben für das zu öffnende Editor-Fenster gemacht werden können.

Abbildung 7.1: Dialog für die Spezifikation eines neuern Layout-Fensters

In diesem Fenster ist die zu verwendete Bibliothek auszuwählen sowie Namen für die Zelle, die entworfen wird, und die Ansicht einzugeben. Dabei ist darauf zu achten, dass die ausgewählte Bibliothek mit der Konstruktionsbibliothek übereinstimmt, welche bei der Erstellung des Schaltplans genutzt wurde. Wird der Dialog aus dem Schaltplan-Editor heraus geöffnet, so wird dessen Konstruktionsbibliothek im o. g. Dialog automatisch ausgewählt. Des Weiteren ist die zugehörige Anwendung – hier *LayoutL* – auszuwählen. Nach Bestätigung der Eingaben durch *OK* öffnet sich das Fenster mit dem Layout Editor.

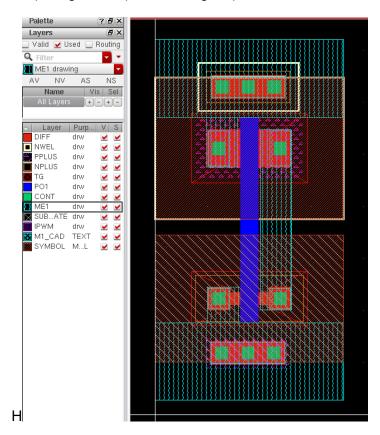

Abbildung 7.2: Fenster Layout L Editor

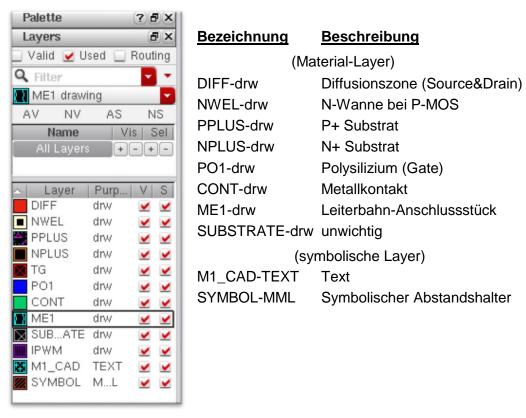

Abgesehen von den Menü- und Werkzeugleisten besteht das Fenster im Wesentlichen aus Bereichen bzw. Teilfenstern. Der Hauptbereich bildet die anfänglich noch leere Arbeitsfläche, in der das Layout erstellt wird. An der linken Seite angedockt ist ein kleineres Fenster für die Layer-Auswahl (LSW – Layer Selection Window). Dieses Fenster dient dazu einzelne Layer mit bestimmtem Material oder symbolischen Elementen für den Entwurf auszuwählen, d. h. der im aktuell im LSW selektierte Layer wird von Virtuoso automatisch für den Entwurf im Arbeitsbereich verwendet. Für die Unterscheidung hat jeder Layer ein eigenes farbiges Muster, das ebenfalls im LSW dargestellt ist. Das LSW und die Erläuterung der zu Verfügung stehenden Layer ist in Abbildung 7.3 dargestellt.

Abbildung 7.3: Layer-Auswahlfenster (LSW) [7]

Außerdem kann im LSW über ein Setzen von Häkchen in den jeweiligen Checkboxen hinter dem Layer-Eintrag festgelegt werde, ob der Layer sichtbar (*V*) und selektierbar (*S*) ist. Zusätzlich besteht durch Bedienfelder oberhalb der Layer-Liste die Möglichkeit, alle Layer einzublenden (*AV* – all visible) bzw. auszublenden sowie alle Layer auswählbar(*AS* – all selected) oder nicht auswählbar (*NS* – None selected) zu machen. Selektierbar bedeutet in diesem Zusammenhang, dass im LSW ein Layer ausgewählt werden kann, um dem Editor einen neuen Bereich hinzuzufügen, oder ein bestehender Bereich aus diesem Layer bearbeitet, z. B. verschoben, vergrößert oder gelöscht, werden kann.

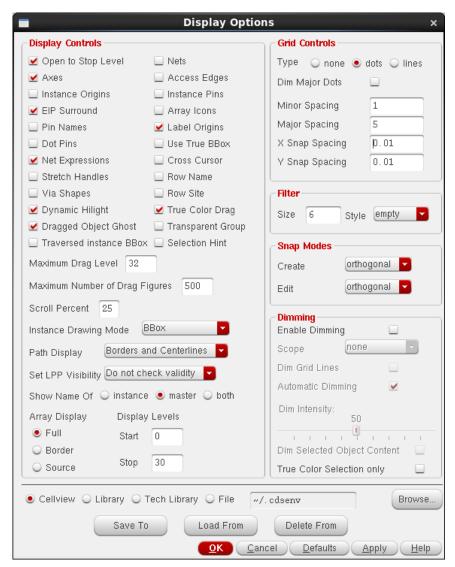

Bevor mit dem eigentlichen Entwurf einer Zelle begonnen wird, empfiehlt es sich die Eigenschaften des Rasters zu konfigurieren. Hierzu wird im Menü *Options* $\rightarrow$ *Display* ausgewählt. Es öffnet sich das in Abbildung 7.4 dargestellte Fenster. Wahlweise kann dieses auch durch Eingabe des Buchstabens "e" aufgerufen werden.

Abbildung 7.4: Fenster Anzeigeoptionen (Display Options)

In diesem Fall ist der Punktabstand mit denen die platzierten Bereiche am Raster gefangen werden (Snap Spacing) zu definieren. Für die Verwendung der Technologie UMC 180 muss unter Grid Controls ein Snap Spacing von 0,01 einzustellen.

#### 7.1.2 Einfügen und Verbinden der Bauelemente

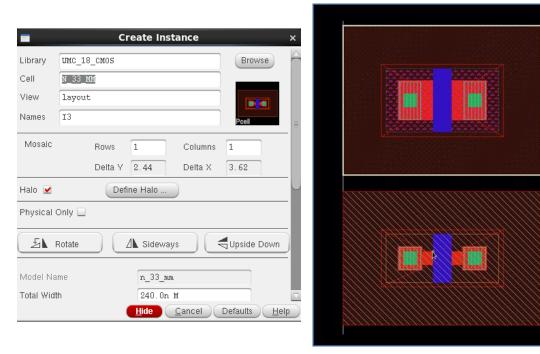

Ein CMOS Inverter besteht im Wesentlichen aus einem NMOS Transistor und einem PMOS Transistor. Daher werden diese beiden Komponenten als erstes in das Layout eingefügt. Hierzu ist eine Instanz hinzuzufügen. Durch Auswahl des Menüpunktes *Create*—*Instance* bzw. mithilfe des Hotkey "I" wird ein Dialog geöffnet (Abbildung 7.5 a)). In

diesem Fenster können die benötigten Bauteile aus der Programmbibliothek ausgewählt werden. Die Auswahl wird mit dem Button *Hide* bestätigt und das ausgewählte Bauelement dem Layout hinzugefügt.

a) Anlegen einer Instanz

b) Layout mit PMOS und NMOS

Abbildung 7.5: Einfügen des PMOS und NMOS

Die eingefügten Bauelemente können selektiert und zur gewünschten Position verschoben werden. Dabei werden sie mit minimalem Absatz zueinander platziert, um ein möglichst kompaktes Layout zu erhalten. Durch betätigen der Taste "q" erscheint ein Dialogfenster mit den Blockparametern. In diesem Fenster können unter anderem die Koordinaten des Blocks eingeben werden. Außerdem kann mithilfe dieses Fensters überprüft werden, ob die Parameter des Transistors im Layout mit jenen im Schaltplan übereinstimmen und die gegebenenfalls erforderlichen Änderungen vorgenommen werden.

Im nächsten Schritt sind die Gate-Elektroden der beiden Transistoren zu verbinden, was mit einem rechteckigen Stück aus Polysilizium umgesetzt wird. Hierzu ist im LSW auf der linken Seite der Layer PO1-drw auszuwählen. Durch Drücken der Taste "R" wird der Modus zum Einfügen eines Rechtecks aktiviert. Durch klicken mit der linken Maustaste und einer gleichzeitigen Ziehbewegung mit der Maus, wird ein Rechteck mit der gewünschten Größe und Position eingefügt. In diesem Fall ist dies, dem ausgewählten Layer-Typ entsprechend, ein blaues Rechteck welches als geometrisches Verbindungselement zwischen den beiden, ebenfalls blau dargestellten, Gate-Anschlüssen eingefügt wird (siehe Abbildung 7.6).

Abbildung 7.6: Verbindung der Gate-Elektroden

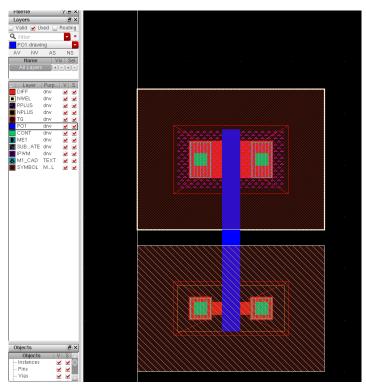

Im nächsten Schritt sind die Bulkkontakte für die Transistoren zu erstellen. Diese werden als Durchkontaktierungen, kurz Vias, angelegt. Dabei ist zu beachten, dass der Bulkkontakt beim NMOS zum Substrat und beim PMOS zum n-Well-Layer erfolgt (vgl.Abbildung 3.1). Die zugehörigen Kontaktelemente in Virtuoso heißen M1\_PDIFF und M1\_NWELL. Um sie einzufügen ist im Menü die Option *Create→Via* auszuwählen oder die Taste "O" zu drücken.

Abbildung 7.7: Erstellen der Kontakte M1\_PIIFF für NMOS und M1\_NWEL für PMOS

Es öffnet sich ein Fenster, in dem der Via ausgewählt und konfiguriert werden kann (Abbildung 7.). Die per Default ausgewählte Konfiguration kann in der Regel übernommen werden. Wichtig sind die Felder Columns und Rows mit der – falls Werte größer 1 angegeben werden – ein Gruppe von Vias erzeugt werden kann. Hier wird Colums 3 und Rows 1 gewählt, um eine Reihe mit 3 Vias zu erzeugen. Mit dem Button *Hide* werden die Via-Elemente in das Layout eingefügt. Danach werden die Kontakte mit geringstmöglichem Abstand dem jeweiligen Transistor angeordnet. Anschließend wird der Kontakt M1\_PDIFFf mit dem noch freien Drain-Kontakt des NMOS verbunden. Der Kontakt M1\_NWELL wird mit den N-Wannen des PMOS verbunden.

Des Weiteren sind aktive Kontakte, d. h. Verbindungen zwischen der Metal-1-Schicht und der aktiven Schicht, herzustellen. In die diesem Fall gehören zu aktiven Schicht die Drain- und Source-Bereiche der beiden Transistoren, welche mit Diffusions-Metal-1-Kontakten versehen sind. Für die Erstellung der Verbindungen wird im LSW die Metal-1-Schicht (ME1-drw) ausgewählt (s. Abbildung 7.8).

Abbildung 7.8: Verbindung von Gates und Drains

Wie bereits bei der Verbindung der Gates wird wieder ein Rechteck gezeichnet und entsprechend positioniert. Auf diese Weise werden drei Verbindungen erstellt:

- Verbindung der Source des NMOS mit der GND-Schiene

- Verbindung der Source des PMOS mit der VDD-Schiene

Verbindung der beiden Drain-Anschlüsse von NMOS mit PMOS.

Die letztgenannte Verbindung stellt gleichzeitig den Ausgangsknoten des Inverters dar.

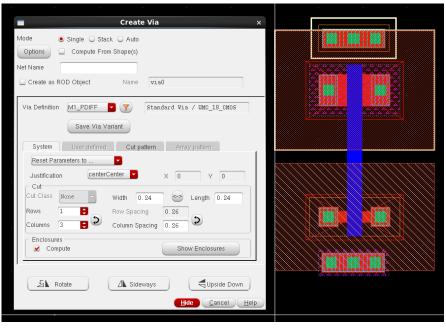

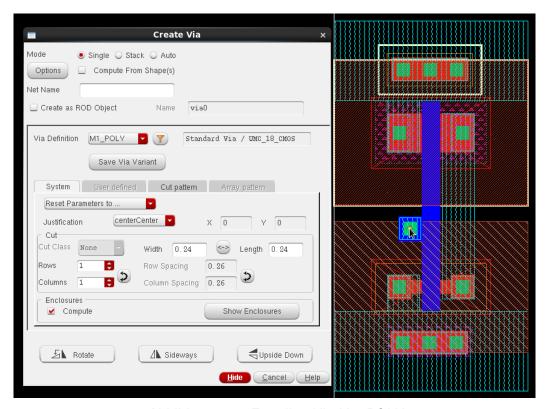

Als letzte Verbindung ist der Eingangsknoten zu erstellen, d. h. die Verbindung zu den Gates der Transistoren. Dazu wird ein Via M1\_Poly eingefügt. Wie bereits für die anderen Vias beschrieben, wird dazu die Menüoption *Create→Via* gewählt oder die Taste "o" gedrückt. Im Konfigurationsdialog wird aus der Auswahlliste M1\_POLY ausgewählt (s. Abbildung 7.9)

Abbildung 7.9: Erstellen Via M1\_POLY

Wie die Abbildung zeigt, wird der Via mittig an der Verbindung zwischen den beiden Gates platziert.

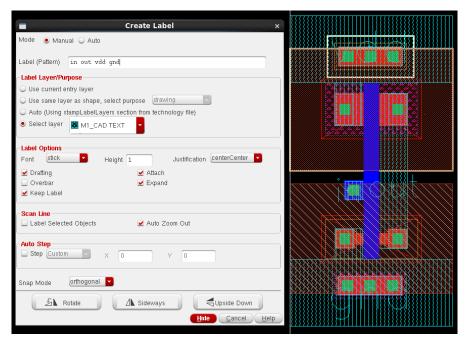

Um das Layout zu vervollständigen, sind de Eingangs- und Ausgangspins zu definieren. Um einen Pin zu erstellen, wird der Menüpunkt *Create→Label* ausgewählt. Es öffnet sich das im linken Teil von Abbildung 7. dargestellte Dialog Fenster. In dem Dialog können die Namen (Label Pattern), die in dem ausgewählten Layer eingefügt werden sollen, festgelegt und deren Darstellung im Layout konfiguriert werden. Die Eingabe der Namen erfolgt somit en bloc, wobei die einzelnen Namen jeweils durch ein Leerzeichen getrennt werden.

Abbildung 7.10: Erstellen von Labels

Nach der Bestätigung der Eingabe (Button *Hide*) werden im Layout die Namen sukzessive durch Mausklick den gewünschten Anschlüssen zugeordnet, wobei die Namen in der zuvor eingegebenen Reihenfolge abgerufen werden. Bei der Vergabe der Namen ist darauf zu achten, dass die Namen mit den Bezeichnungen im Schematic übereinstimmen und die Zuordnung zum richtigen Layer erfolgt.

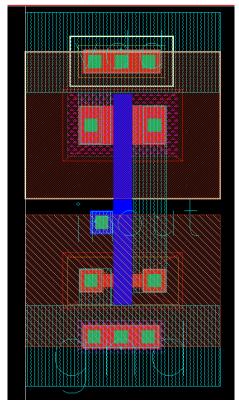

Abbildung 7.11: Vollständiges Inverter-Layout

Unter Beachtung dieser Vorgehensweise ergibt sich das vollständige Layout für einen einzelnen Inverter, dass in Abbildung 7. dargestellt ist.

### 7.1.3 Überprüfung des Layouts

Um die Funktion der anhand des Layouts erstellten Schaltung zu gewährleisten, wird es abschließend überprüft. Dabei wird zum einen die Einhaltung der Designregeln verifiziert und zum anderen die Übereinstimmung von Layout und Schaltplan überprüft. Diese beiden Überprüfungen werden nicht nur bei der Erstellung durchgeführt, sondern auch bei jeder weiteren Bearbeitung des Layouts.

#### ❖ Überprüfung der Einhaltung der Designregeln

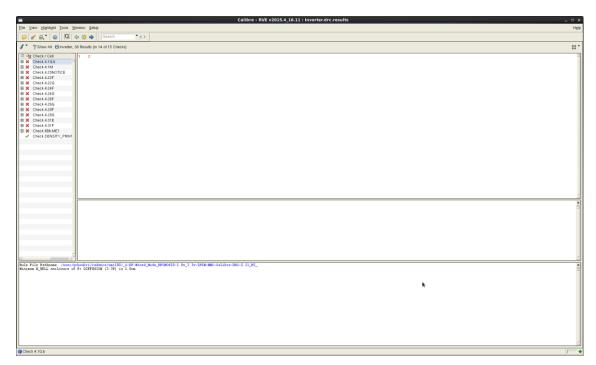

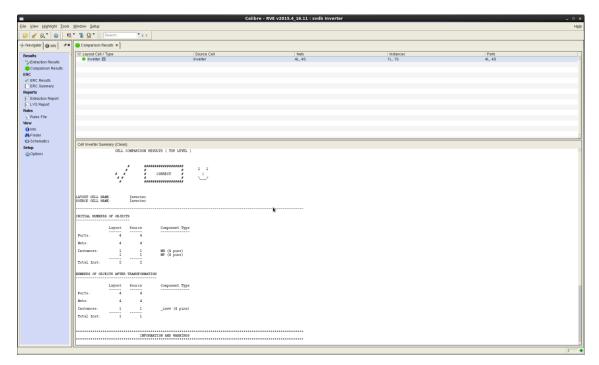

Wie bereits erwähnt, muss das Layout einer Reihe von Designregeln entsprechen. Diese Regeln basieren im Wesentlichen auf Designvorgaben des Herstellers. Die Prüfung wird durch einen sog. Design Rule Check (DRC) umgesetzt. Um diesen Check zu starten ist im Menü Calibre →Run DRC auszuwählen. Es erscheint ein Dialogfenster mit dem DRC-Formular. Hier müssen allerdings keine Änderungen an den vorgegebenen Eintragungen vorgenommen werden, sodass der Check unmittelbar mit der Schaltfläche Run DRC gestartet werden kann. Da beim Anlegen des Layouts die Bibliothek mit der UMC-180-Technologie festgelegt wurde, erfolgt der DRC nach den zugehörigen Regeln. Nach Abschluss des Checks öffnet sich die Results Viewing Environment (RVE), welche in Abbildung 7.12 dargestellt ist.

Abbildung 7.12 Results Viewing Environment des Design Rule Check

Der linke Teil des Fensters enthält eine Liste mit den Regeln, die geprüft worden sind, wobei durch ein grünes Häkchen bzw. ein rotes Kreuz angezeigt wird, ob die Prüfung erfolgreich war oder nicht. Bei Auswahl einer der Regeln wird im unteren Teil des Fensters eine Kurzbeschreibung der Regel angezeigt. Des Weiteren wird für den Fall, dass bei der Überprüfung dieser Regel Fehler aufgetreten sind, im Hauptteil des Fensters die Koordinaten der einzelnen Regelverstöße angezeigt. Wird einer dieser Koordinateneinträge ausgewählt, kann durch einen Doppelklick zur Layout-Ansicht gewechselt werden, in welcher der ausgewählte Fehler hervorgehoben ist.

#### Der Layout-versus-Schematic-Check

Nachdem das Layout der Zelle bezüglich der Designregeln überprüft und ggf. aufgetretene Fehler korrigiert wurden, wird im zweiten Prüfschritt die Übereinstimmung des Layout mit dem Schaltplan geprüft. Bei diesem Layout-versus-Schemtic-Check (LVS-Checkt) wird automatisch aus dem Layout eine Netzliste extrahiert und mit dem Schaltplan verglichen. Dadurch wird sichergestellt, dass keine Verbindungsfehler, wie fehlende Verbindungen oder Kurzschlüsse, vorhanden sind. Die Vorgehensweise ähnelt weitgehend der des DRC. Der LVS-Check wird im Menü unter *Caliber→Run LVS* durchgeführt. Anschließend öffnet sich ein RVE-Fenster mit den Prüfergebnissen (siehe Abbildung 7.13).

Abbildung 7.13: Results Viewing Environment des LVS-Check

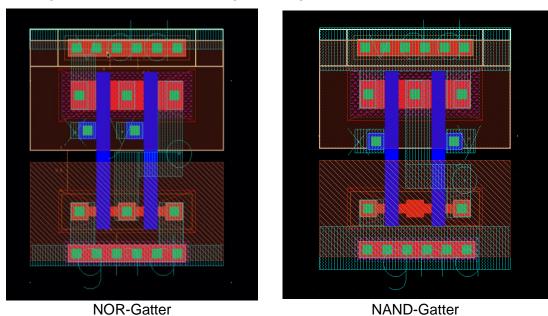

## 7.2 Erstellung des Gesamtlayouts

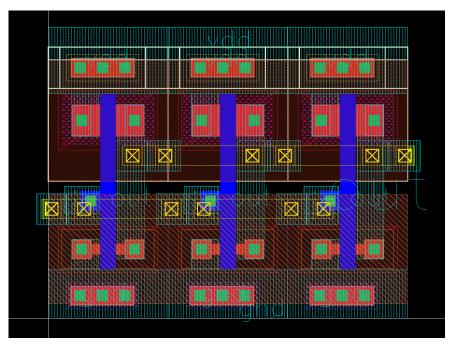

Die Treiberstufenschaltung enthält neben den Invertern, auch NAND- und NOR-Gatter als Grundelemente. Der Entwurf für die zugehörigen Zellen erfolgt analog zu den Invertern und wird daher nicht eigens erläutert. Die fertigen Layouts für die Zellen dieser Schaltungselemente sind in Abbildung 7.14 dargestellt.

Abbildung 7.14: Layout NOR- und NAND-Gatter

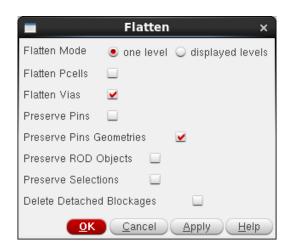

Um mehrere Zellen möglichst platzsparend miteinander kombinieren zu können, werden die Elemente am Rand beschnitten. Hierzu wird die zu beschneidende Zelle selektiert und im Menü *Edit Hierachy Flatten* ausgewählt. Es öffnet sich der Dialog, der in Abbildung dargestellt ist.

Abbildung 7.15: Dialog zum Entfernen der Hierarchien

Durch die gezeigte Einstellung werden alle Elemente auf die gleiche Hierarchieebene gesetzt, wodurch ein flaches Layout ohne Subzellen entsteht. Dies ist die Voraussetzung

dafür, um einzelne Elemente des Layouts selektieren und verändern zu können. Für das Beschneiden wird die Umschalttaste + "C" und anschließend "R" gedrückt. Folgend kann im Layout mit der Maus ein Rechteck mit dem auszuschneidenden Bereich aufgezogen werden (siehe Abbildung 7.16).

Abbildung 7.16: Beschneiden von Layern.

Auf diese Weise werden alle erforderlichen Layer seitlich beschnitten, um den Platzbedarf eines einzelnen Inverters zu minimieren. Dies ermöglicht eine kompakte Verbindung der Inverter zu größeren Zellen, wie Abbildung 7.17 an einem Beispiel zeigt.

Abbildung 7.17: Zelle mit drei Invertern in Reihe

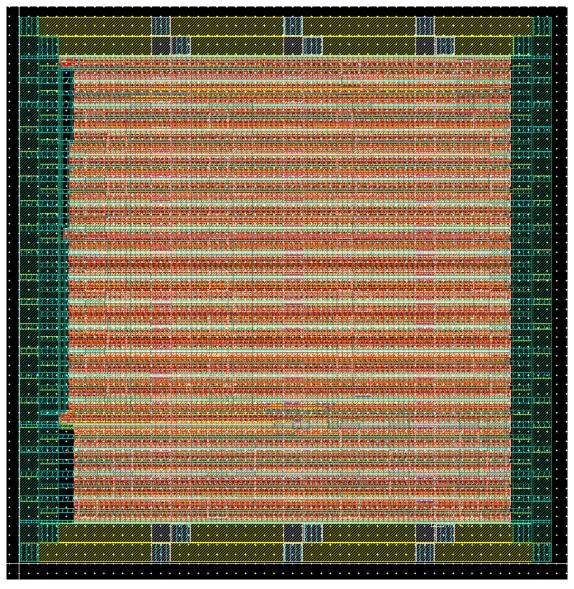

Auf diese Weise werden die einzelnen Elemente sukzessive zu größer werdenden Zellen kombiniert, bis sich schließlich das vollständige Layout der Treiberschaltung in Abbildung 7.18 ergibt.

Abbildung 7.18: Layout der vollständigen Treiberstufe

8 Fazit 44

#### 8 Fazit

Die Funktion der Hauptschaltung des Tiefsetzstellers mit integrierter Treiberstufe wurde erfolgreich verifiziert und ist damit für die Anwendung einsetzbar.

Durch diese Arbeit bin ich zu der Erkenntnis gekommen, dass die Treiberstufe im Abwärtswandler eine wichtige Komponente für den Schaltvorgang der Leistungsschalter darstellt. Insbesondere verhindert sie, dass sich die MOSFETS gleichzeitig schließen, wodurch ein direkter Kurzschluss zur Masse entsteht.

Beim Layout der Treiberstufe wurde die Einhaltung alle Designregeln verifiziert und die Übereinstimmung von Layout und Schaltplan überprüft.

Diese Bachelorarbeit habe ich im Labor der Fachhochschule Dortmund bei Herrn Prof. Dr. Karagounis durchgeführt. Die Simulationen zu dem behandelten Thema wurden in der Software "Virtuoso" umgesetzt.

0 Literaturverzeichnis 45

## Literaturverzeichnis

- [1] TARUN AGRWAL: https://www.elprocus.com/

- [2] R. Jacob Baker, CMOS Circuit Design, Layout, and Simulation

- [3] Virtuoso 6.1-64 vom Softwarehersteller "Cadence Design Systems"

- [4] Armin A. Fomani, "An integrated segmented gate driver with adjustable driving Capability for efficiency optimization", 2010,

- [5] 06-林永裁-Integrated CMOS Buck DC-DC Converter with On-Chip PWM Circuit

- [6] ECE 410, Prof. A: Mason Lecture Notes Page 3.1; Review: CMOS Logic Gates,

- [7] ,, Computer Aided Design in der Mikroelektronik" Universität Bonn"

# Selbstständigkeitserklärung

| "Hiermit versichere ich an Eides statt, dass d | ie von mir vorgelegte Prüfungsleistung    |

|------------------------------------------------|-------------------------------------------|

| selbstständig und ohne unzulässige fremde Hi   | lfe erstellt worden ist. Alle verwendeten |

| Quellen sind in der Arbeit so aufgeführt, dass | Art und Umfang der Verwendung nach-       |

| vollziehbar sind."                             |                                           |

|                                                |                                           |

|                                                |                                           |

|                                                |                                           |

|                                                |                                           |

|                                                |                                           |

| Ort, Datum                                     | Unterschrift                              |