# Optimierung eines Local Passive Interpolation Time-to-Digital Converters mit Sub-Gate Delay für eine Time-of-Flight Anwendung

# Masterarbeit

Andreas Pille

Matrikelnummer: 7203440

Erstprüfer: Prof. Dr. Michael KARAGOUNIS

Zweitprüfer: Dr. Wolfram BUDDE

# Kurzfassung

Im Rahmen dieser Masterthesis wird in Zusammenarbeit mit der Firma Elmos Semiconductor AG ein Time-To-Digital Converter für eine Time-of-Flight Anwendung weiterentwickelt und optimiert. Als Ausgangspunkt dafür dient die in der vorhergehenden Masterstudienarbeit optimierte Schaltung eines vorhandenen TDC.<sup>1</sup>

Die primäre Aufgabe des Time-to-Digital Converters ist die Quantifizierung einer zeitlichen Verzögerung zwischen zwei Eingangssignalen. Genutzt wird dafür ein Local Passive Interpolation (LPI) TDC mit einer angepeilten Auflösung von 70 Pikosekunden, der als integrierte Schaltung in einer 350 nm CMOS-Technologie realisiert wird. Hauptbestandteil dieser Arbeit ist die Verringerung vorhandener Messungenauigkeiten, die Untersuchung des Einflusses von Layout-Effekten auf die Funktion des TDC und die Überführung der optimierten Schaltung in ein Layout.

## **Abstract**

Subject of this thesis is the development and optimization of a Time-to-Digital Converter (TDC) for the use in a Time-of-Flight (TOF) application in cooperation with Elmos Semiconductor AG. A previous work of the author<sup>1</sup> serves as a conceptual basis for this thesis.

The primary objective of the TDC is the quantification of a time-delay between two input signals. To accomplish this, a Local Passive Interpolation (LPI) TDC with a targeted resolution of 70 ps, realized as an integrated circuit in a 350 nm process technology, is used. The main focus of this thesis is the reduction of measurement errors, the influence of layout effects on the reliability of the TDC and the transfer of the optimized schematics to a layout.

# Eidesstattliche Erklärung

Hiermit erkläre ich, dass ich die vorliegende Arbeit eigenständig und ohne fremde Hilfe angefertigt habe. Textpassagen, die wörtlich oder dem Sinn nach auf Publikationen oder Vorträgen anderer Autoren beruhen, sind als solche kenntlich gemacht.

Die Arbeit wurde bisher keiner anderen Prüfungsbehörde vorgelegt und auch noch nicht veröffentlicht.

Ort, Datum

Unterschrift

# Inhaltsverzeichnis

| 1 | Einl | eitung 1                                               |

|---|------|--------------------------------------------------------|

|   | 1.1  | Anwendung                                              |

|   |      | 1.1.1 Time-of-Flight                                   |

|   |      | 1.1.2 Funktionsprinzip der Kamera                      |

|   |      | 1.1.3 Einordnung des Time-to-Digital Converters        |

|   | 1.2  | Ziele                                                  |

| 2 | The  | oretische Grundlagen 9                                 |

|   | 2.1  | Time-to-Digital Converter                              |

|   |      | 2.1.1 Delay-Line basierte TDC                          |

|   |      | 2.1.2 Leistungsmerkmale von TDC                        |

|   | 2.2  | Delay-Locked-Loop basierte TDC                         |

|   | 2.3  | TDC mit Sub-Gate-Delay                                 |

|   | 2.4  | Parasitäre Einflüsse des Layouts                       |

|   |      | 2.4.1 Substrateffekte                                  |

|   |      | 2.4.2 Oberflächeneffekte                               |

|   |      | 2.4.3 Einfluss der Metallschichten                     |

|   | 2.5  | Matching                                               |

|   |      | 2.5.1 Einheitselemente                                 |

|   |      | 2.5.2 Ortsabhängige Prozessgradienten                  |

| 3 | Auf  | bau des TDC 31                                         |

|   | 3.1  | Gesamtaufbau des TDC                                   |

|   | 3.2  | Phasendetektor                                         |

|   | 3.3  | Charge Pump                                            |

|   | 3.4  | Spannungsregler                                        |

|   | 3.5  | False- und Harmonic-Lock                               |

|   | 3.6  | Delay-Line                                             |

|   | 3.7  | Regelschleife                                          |

| 4 | Opt  | imierung des TDC-Designs 45                            |

|   | 4.1  | Delay-Line Flipflop                                    |

|   | 4.2  | Testchip                                               |

|   |      | 4.2.1 Anpassung des Pegelwandlers                      |

|   |      | 4.2.2 Tap-Buffer                                       |

|   |      | 4.2.3 Sensing Buffer                                   |

|   | 4.3  | Generation des Start-Stop Signals                      |

|   | 4.4  | Variable Verzögerungskette für den Gesamtregelkreis 61 |

| 5 | Lay  | out 64                                                 |

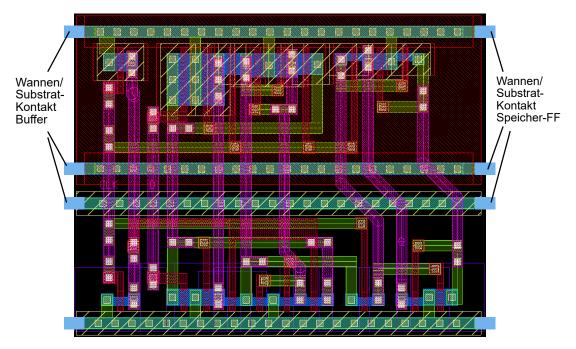

|   | 5.1  | Layout des Testchips                                   |

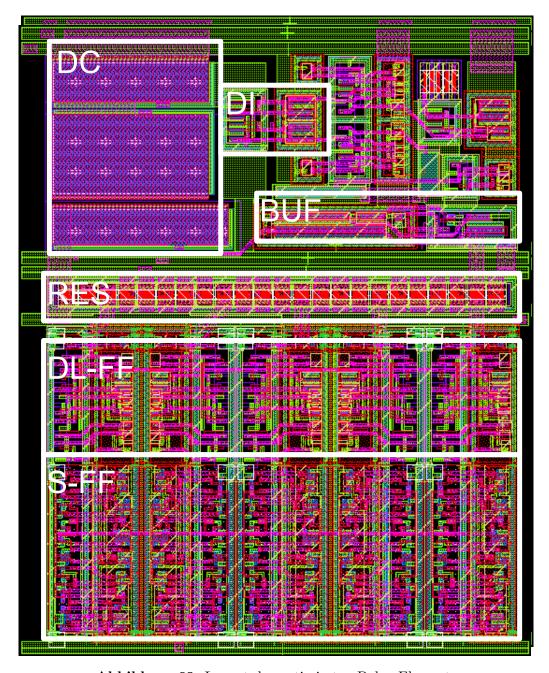

|   | 5.2  | Parasitäre Einflüsse des Testchip-Layouts              |

## Inhaltsverzeichnis

| 6 | Fazi | it und Ausblick                              | 78 |

|---|------|----------------------------------------------|----|

|   | 5.4  | Parasitäre Einflüsse des optimierten Layouts | 74 |

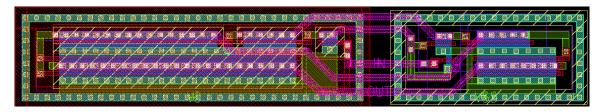

|   |      | 5.3.3 Layout des Delay-Elements              | 72 |

|   |      | 5.3.2 Layout des Interpolationsbuffers       | 72 |

|   |      | 5.3.1 Layout des Delay-Line Flipflops        | 71 |

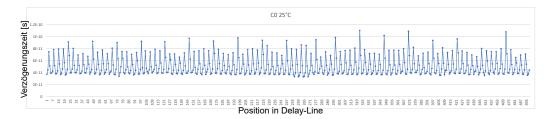

|   | 5.3  | Layout des optimierten Designs               | 70 |

# Abbildungsverzeichnis

| 1  | Time-of-Flight Funktionsprinzip                                           | 3  |

|----|---------------------------------------------------------------------------|----|

| 2  | Vereinfachte Darstellung eines Active-Pixel-Sensors                       | 3  |

| 3  | Messverfahren der Time-of-Flight Kamera                                   | 4  |

| 4  | Abstandsbild aus Messungen der Pixelmatrix                                | 5  |

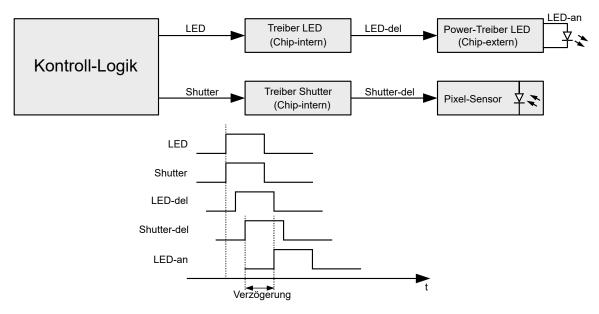

| 5  | Erzeugung der LED- und Shutter-Signale                                    | 6  |

| 6  | Quantisierung eines Zeitintervalls mithilfe eines zählerbasierten TDC     | 10 |

| 7  | Aufbau eines Delay-Line basierten TDC                                     | 11 |

| 8  | Ausgangs-Code bei Nutzung von Buffer- oder Inverter-Verzögerungselementen |    |

|    |                                                                           | 11 |

| 9  | Übertragungsfunktion des idealen TDC                                      | 12 |

| 10 | Auswirkung der DNL auf die Übertragungsfunktion des TDC                   | 14 |

| 11 | Funktionsprinzip des DLL-TDC                                              | 15 |

| 12 | Funktionsprinzip der LPI (a) und LPI mit zu starker Verzögerung (b)       | 17 |

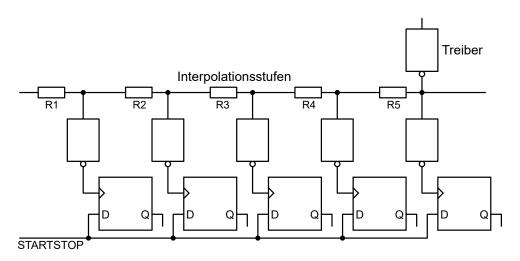

| 13 | Aufbau des LPI-TDC                                                        | 18 |

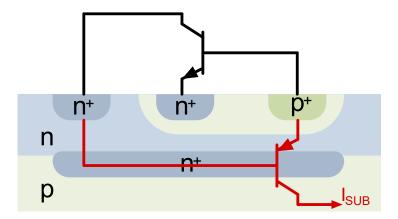

| 14 | Parasitäre Substratstromquelle                                            | 20 |

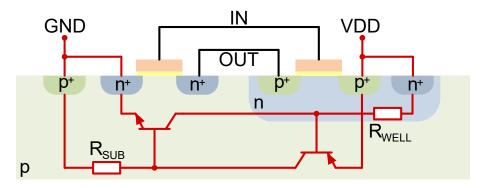

| 15 | Parasitärer Thyristor bei einem CMOS-Inverter                             | 21 |

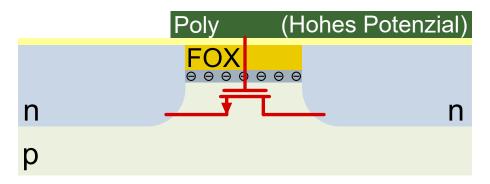

| 16 | Parasitärer NMOS-Transistor durch Oberflächeneffekte                      | 21 |

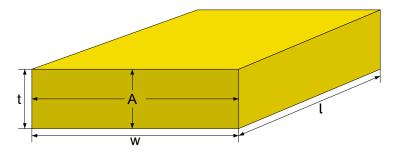

| 17 | Dimensionen der Metallbahnen                                              | 22 |

| 18 | Schichtwiderstand in Metallbahnen                                         | 23 |

| 19 | Parasitäre Kapazitäten zwischen den Schichten eines Layouts               | 24 |

| 20 | Crosstalk zwischen Metallbahnen                                           | 25 |

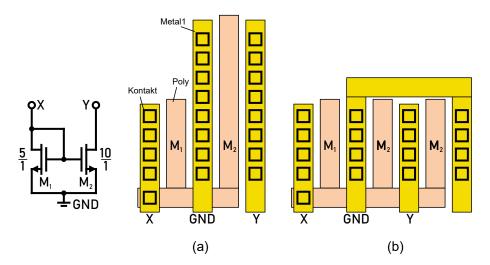

| 21 | Layout eines Spannungsteilers mit (a) und ohne (b) Matching               | 27 |

| 22 | Layout eines Stromspiegels ohne (a) und mit (b) Matching                  | 28 |

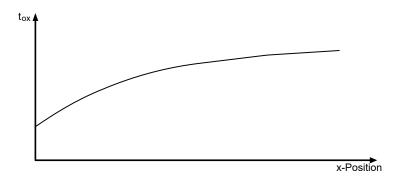

| 23 | Gateoxidtiefe über der Position auf einem Chip                            | 28 |

| 24 | Einfluss der Gateoxidtiefe auf unterschiedliche Transistoren              | 29 |

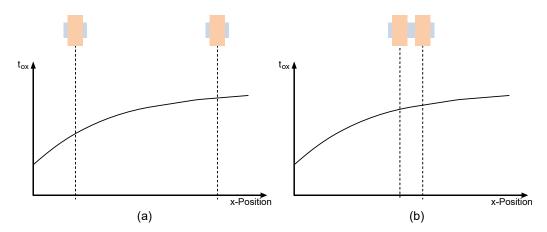

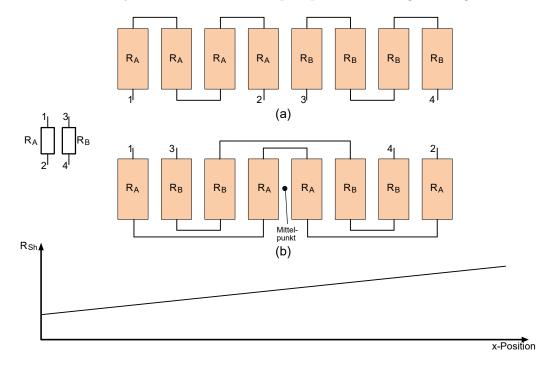

| 25 | Common-Centroid Layout bei Poly-Widerständen                              | 29 |

| 26 | Blockdiagramm des Time-to-Digital Converters                              | 31 |

| 27 | Aufbau eines einfachen Positive-Edge-Triggered (PET)-Phasendetektors      | 33 |

| 28 | Signalverlauf des Phasendetektors bei unterschiedlichen Phasenverschie-   |    |

|    | bungen                                                                    | 34 |

| 29 | Aufbau des erweiterten Phasendetektors mit zusätzlichen Eingangssignalen  | 34 |

| 30 | Aufbau der Charge-Pump                                                    | 35 |

| 31 | Vereinfachter Aufbau des Spannungsreglers                                 | 36 |

| 32 | Einschwingen auf minimales Delay bei einem False-Lock                     | 37 |

| 33 | False-Lock Detektor                                                       | 37 |

| 34 | Signalverlauf bei einem Harmonic-Lock                                     | 38 |

| 35 | Aufbau des Harmonic-Lock Detektors                                        | 39 |

| 36 | Schematische Darstellung der spannungsgesteuerten Delay-Line              | 40 |

| 37 | Aufbau eines Verzögerungselements                                         | 41 |

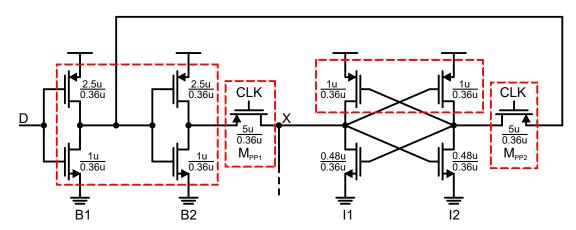

| 38 | Aufbau des Delay-Line Flipflops zu Beginn der Betrachtungen               | 42 |

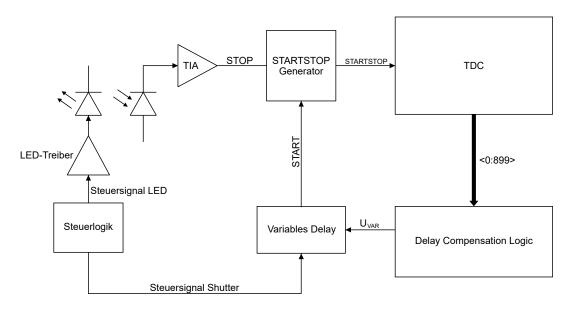

| 39 | Vereinfachte Darstellung der Gesamtanwendung                              | 43 |

| 40 | Position der Delay-Line Flipflops im Verzögerungselement                  | 45 |

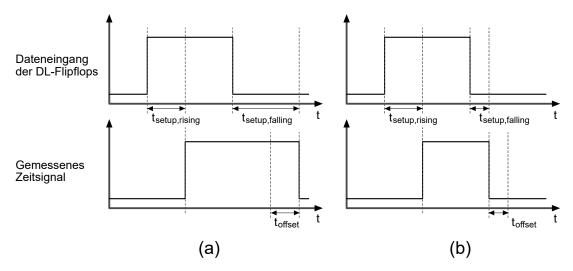

| 41               | Resultierender Offset bei unterschiedlichen Setup-Zeiten                  |

|------------------|---------------------------------------------------------------------------|

| 42               | Ansatzpunkte für die Optimierung des DL-Flipflops                         |

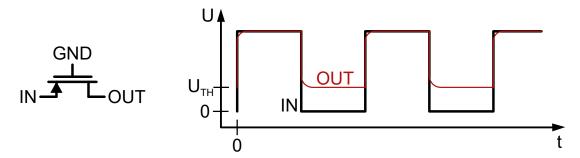

| 43               | Ein- und Ausgangssignal eines PMOS Pass-Gates                             |

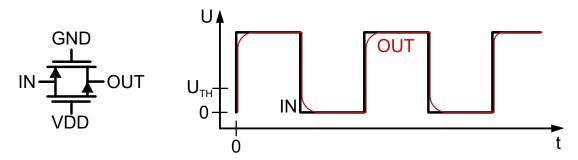

| 44               | Ein- und Ausgangssignal eines Transmission-Gates                          |

| 45               | Eingangsstufe des DL-Flipflops nach Anpassung                             |

| 46               | Angepasstes Delay-Line Flipflop                                           |

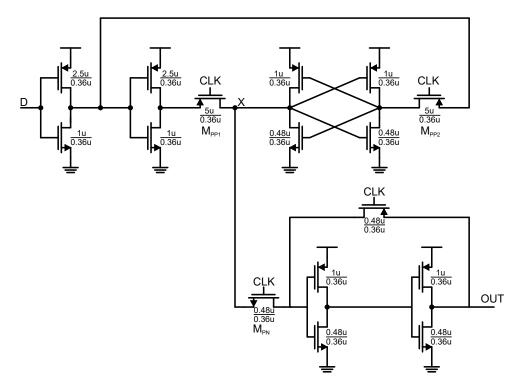

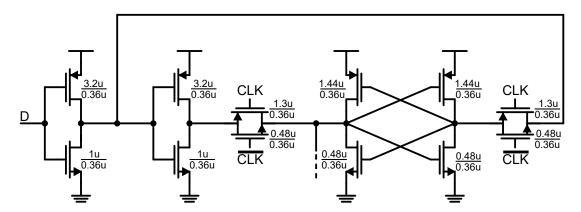

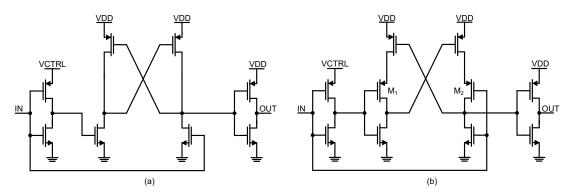

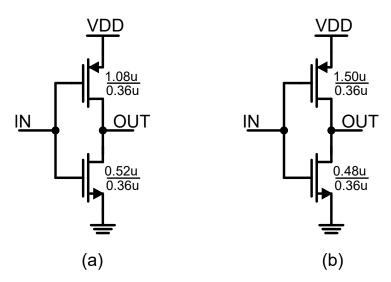

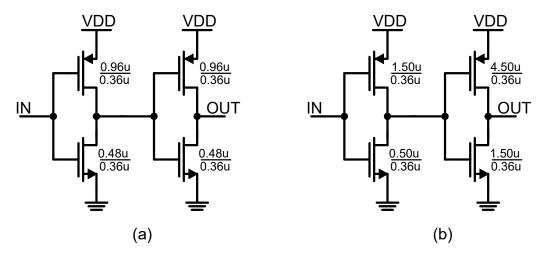

| 47               | Aufbau der im TDC (a) und Testchip (b) verwendeten Pegelwandler 53        |

| 48               | Ein- und Ausgangssignale der beiden Pegelwandler                          |

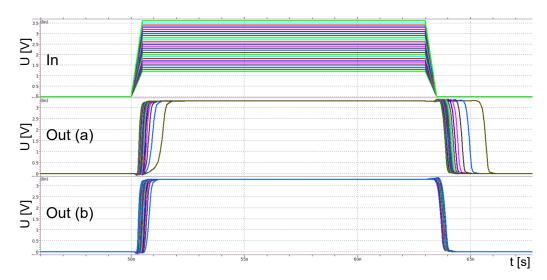

| 49               | Verzögerung der Interpolationsstufen an unterschiedlichen Positionen der  |

|                  | Delay-Line                                                                |

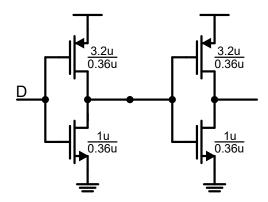

| 50               | Unterschiede der Bufferstufen im Testchip (a) und der aktuellen Schaltung |

|                  | (b)                                                                       |

| 51               | Sensing Buffer im Testchip (a) und im aktuellen Design (b)                |

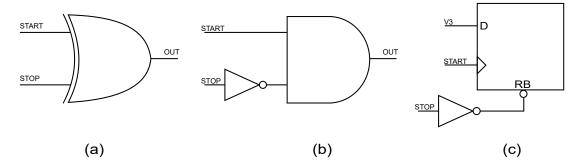

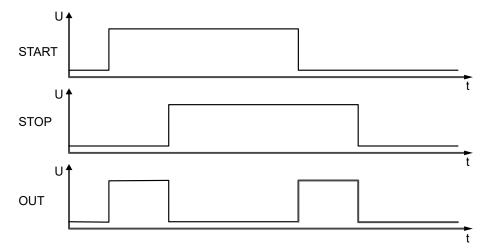

| 52               | Generierung eines STARTSTOP Signals                                       |

| 53               | Ein- und Ausgangssignale des XOR-Gates                                    |

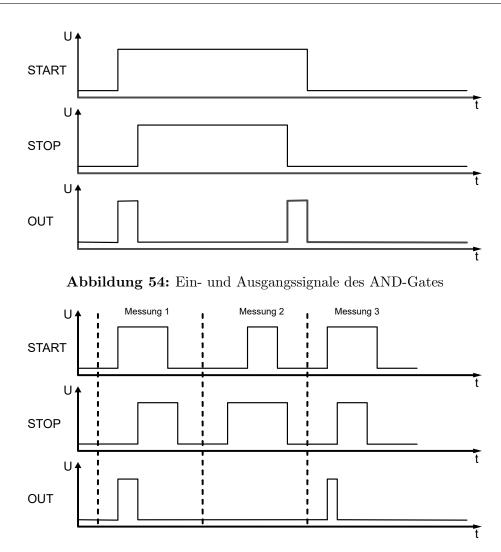

| 54               | Ein- und Ausgangssignale des AND-Gates 61                                 |

| 55               | Ein- und Ausgangssignale des Flipflops 61                                 |

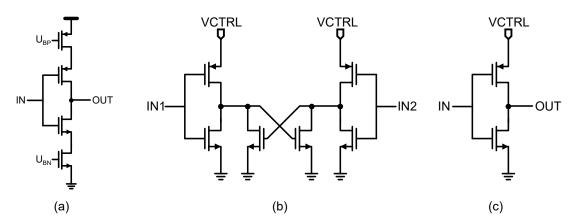

| 56               | Mögliche Verzögerungselemente für das variable Delay 62                   |

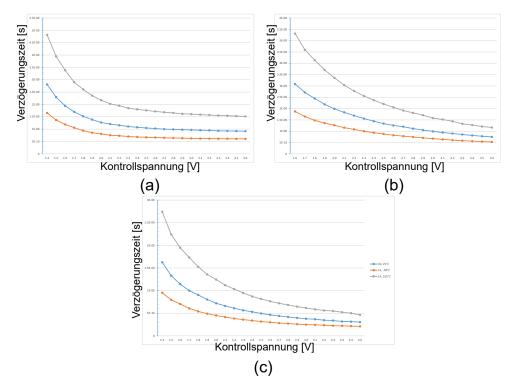

| 57               | Verzögerungsverlauf der unterschiedlichen Verzögerungselemente 63         |

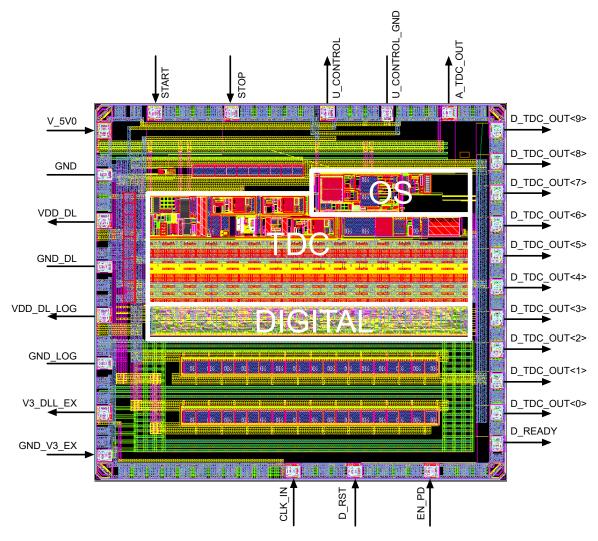

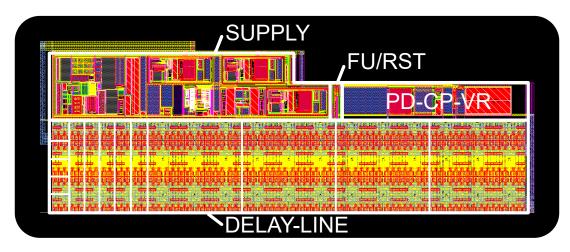

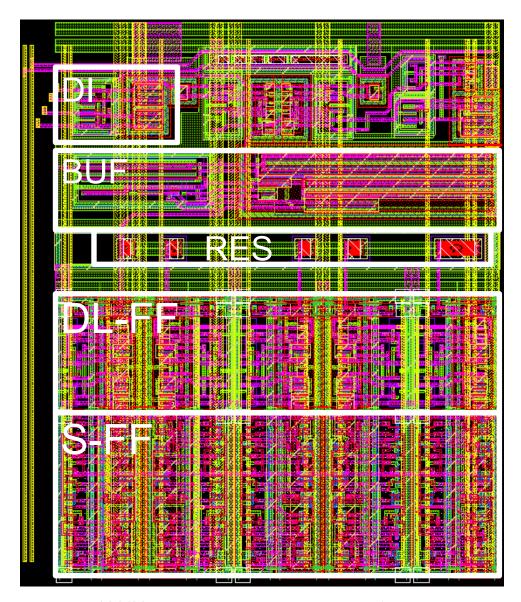

| 58               | Layout des Testchips                                                      |

| 59               | Layout des TDC                                                            |

| 60               | Layout eines Verzögerungselements                                         |

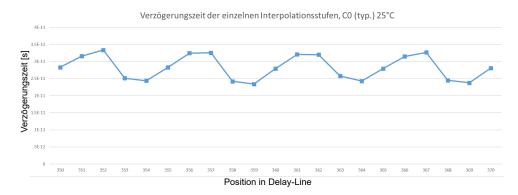

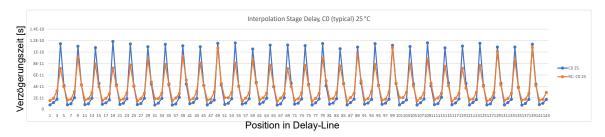

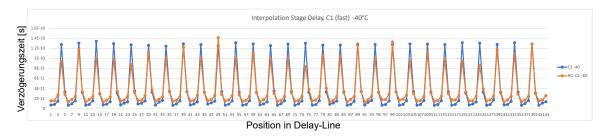

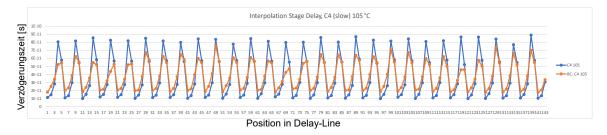

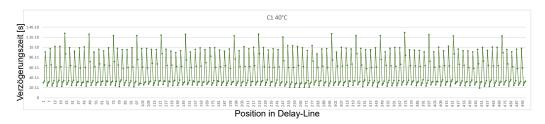

| 61               | Verzögerung zwischen Interpolationsstufen, C0 25°C 69                     |

| 62               | Verzögerung zwischen Interpolationsstufen, C1 -40°C 69                    |

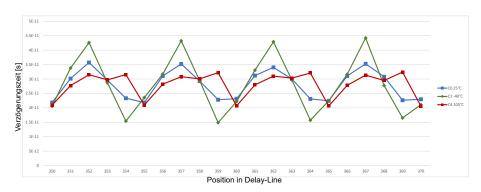

| 63               | Verzögerung zwischen Interpolationsstufen, C4 105°C 69                    |

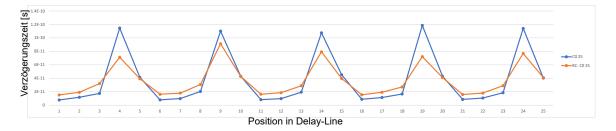

| 64               | Vergrößerte Ansicht der Verzögerungszeiten                                |

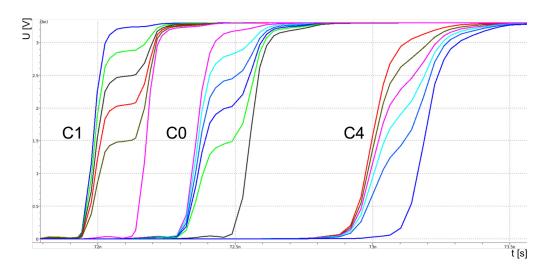

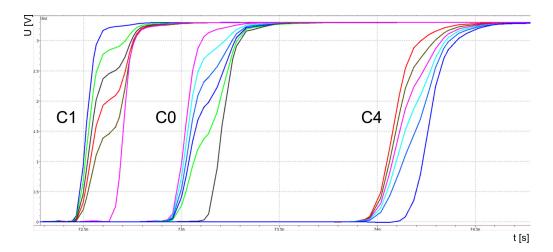

| 65               | Signalverlauf durch die Interpolationsstufen ohne Einfluss des Layouts 70 |

| 66               | Signalverlauf mit parasitären Kapazitäten und Widerständen 70             |

| 67               | Layout des Delay-Line Flipflops                                           |

| 68               | Layout der Treiberstufe                                                   |

| 69               | Layout des optimierten Delay-Elements                                     |

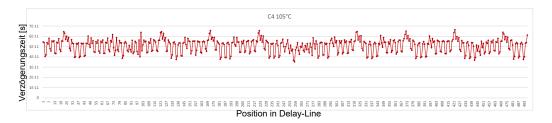

| 70               | Verzögerung zwischen Interpolationsstufen, C0 25°C                        |

| 71               | Verzögerung zwischen Interpolationsstufen, C1 -40°C                       |

| 72<br><b>7</b> 2 | Verzögerung zwischen Interpolationsstufen, C4 105°C                       |

| 73               | Vergrößerte Ansicht der Verzögerungszeiten                                |

| 74               | Messpunkt im Delay-Line Flipflop für Homogenitätsbetrachtung 79           |

|                  |                                                                           |

|                  |                                                                           |

| Tabe             | ellenverzeichnis                                                          |

|                  |                                                                           |

| 1                | Setup-Zeiten des DL-Flipflops im Ausgangszustand                          |

| 2                | Setup-Zeiten des DL-Flipflops mit Transmission-Gates                      |

| 3                | Setup-Zeiten mit vergrößerten PMOS-Transistoren im Master-Latch 49        |

| 4                | Setup-Zeiten nach Anpassung der Eingangsstufe                             |

## Tabellenverzeichnis

| 5  | Resimulation einer Zeitmessung mit optimiertem Delay-Line Flipflop   | 51 |

|----|----------------------------------------------------------------------|----|

| 6  | Vergleich der Homogenität mit unterschiedlichen Pegelwandlern        | 54 |

| 7  | Resimulation einer Zeitmessung mit geändertem Pegelwandler           | 55 |

| 8  | Vergleich der Homogenität mit unterschiedlichen Tap-Buffern          | 56 |

| 9  | Resimulation einer Zeitmessung mit geändertem Pegelwandler           | 57 |

| 10 | Vergleich der Homogenität mit unterschiedlichen Sensing Buffern      | 58 |

| 11 | Homogenität ohne zweiten Sensing-Buffer                              | 59 |

| 12 | Verzögerung eines einzelnen Delay-Elements mit und ohne Parasitics   | 68 |

| 13 | Verzögerung eines optimierten Delay-Elements mit und ohne Parasitics | 74 |

| 14 | Standardabweichung, DNL und INL des erstellten Layouts               | 77 |

# Abkürzungsverzeichnis

ADC Analog-Digital-Converter

**APS** Active-Pixel-Sensor

**DLL** Delay Locked Loop

**DL-TDC** Delay-Line basierten TDC

**DLL-TDC** Delay-Locked-Loop basierten TDC

**DNL** Differenzielle Nichtlinearität

INL Integrale Nichtlinearität

**LPI** Local Passive Interpolation

LPI-TDC Local-Passive-Interpolation TDC

**PET** Positive-Edge-Triggered

**TDC** Time-to-Digital Converter

**TOF** Time-of-Flight

# 1 Einleitung

Seit einigen Jahren ist der stetige technologische Trend zu beobachten, dass immer mehr technische Systeme mit lokaler Intelligenz und vielfältiger Sensorik ausgestattet werden. In Wissenschaft, Industrie und Alltag ermöglichen Sensoren zusätzlichen Komfort und Sicherheit durch die automatisierte Interaktion von Mensch und Maschine und die Überwachung von Umwelt-und Arbeitsbedingungen. Bewusst oder unbewusst kommt jeder Mensch täglich mit unterschiedlichen Sensortypen in Berührung. So sind zum Beispiel in Mobiltelefonen, in Automobilen oder anderen Alltagsgegenständen zahlreiche Sensoren verbaut, die für eine leichtere Bedienung und eine Erweiterung des Funktionsumfangs sorgen und Unfälle verhindern sollen.

Time-of-Flight Sensoren stellen dabei eine spezielle Kategorie von optischen Sensoren dar. Mithilfe von Lichtpulsen, welche oftmals von einer Laser-Lichtquelle generiert und von der Umgebung reflektiert werden, können hochpräzise Messungen durchgeführt werden. Die Anwendungsgebiete von Time-of-Flight Sensoren sind vielfältig und teilweise hochspezialisiert. Eine der wohl häufigsten Anwendungen sind Messungen, bei der die Laufzeit eines Lichtimpulses zur Berechnung des Abstands zwischen dem Sensor und einem Objekt genutzt wird.

Time-of-Flight Sensoren finden beispielsweise im Automobil oder in der Industrie häufig Anwendung und müssen daher auch bei schwierigen Umweltbedingungen zum Beispiel bei großen Temperaturschwankungen fehlerfrei funktionieren. Der Sensorbetrieb unter derartigen Bedingungen hat Messungenauigkeiten zur Folge, die durch zusätzliche Elektronik ausgeglichen werden müssen, um akkurate Ergebnisse zu erzielen. Aufgrund der hohen Ausbreitungsgeschwindigkeit der generierten Lichtpulse können bereits geringe Abweichungen in der Zeitmessung zu starken Messabweichungen führen.

Für die genaue Messung von Zeitintervallen werden in einigen Anwendungsbereichen schon seit Jahrzehnten Time-to-Digital Converter eingesetzt<sup>2</sup>. Vor allem für die Messung des zeitlichen Abstands zwischen zwei eingehenden Impulsen sind diese Schaltungen von großem Nutzen. Time-to-Digital Converter ermöglichen eine binäre Repräsentation des gemessenen Zeitintervalls, und ermöglichen so die digitale Weiterverarbeitung der gewonnenen Information.

$<sup>^{2}[2],</sup> S.5$

## 1.1 Anwendung

Die Elmos Semiconductor AG in Dortmund entwickelt eine 3D-Kamera, die in Automobilanwendungen genutzt werden soll. Diese Kamera soll mithilfe des Time-of-Flight Prinzips präzise Abstandsbilder erzeugen und die Detektion von Objekten und deren Entfernung ermöglichen.

Die erzeugten Abstandsbilder können im Innen- und Außenraum eines Automobils für unterschiedliche Zwecke genutzt werden. Im Außenraum eines Fahrzeugs kann eine solche Kamera beispielsweise für die Erkennung von Hindernissen, die kontaktlose Bedienung eines Kofferraums oder für Fahr- und Parkassistenzsysteme eingesetzt werden. Im Innenraum ist eine Verwendung unter anderem im Rahmen der Gestensteuerung oder für Sicherheitssysteme denkbar.

Für einen Überblick auf die geplante Anwendung des zu optimierenden Time-to-Digital Converters, ist es zunächst sinnvoll, das Time-of-Flight Prinzip und die Funktionsweise der Kamera näher zu erläutern.

### 1.1.1 Time-of-Flight

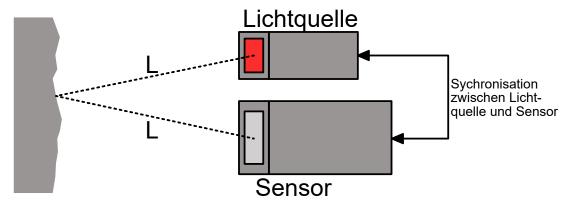

Das Time-of-Flight Messprinzip basiert auf der Konstanz der Lichtgeschwindigkeit. Wie in Abbildung 1 dargestellt, erzeugt eine Lichtquelle einen Lichtimpuls, der von einem Objekt in einer Entfernung L reflektiert wird. Ein Empfänger, der sich im gleichen Abstand zum Objekt befindet, registriert den reflektierten Lichtpuls und berechnet die Strecke L. Die Messung des reflektierten Lichtimpulses und die Berechnung des Abstands kann mithilfe unterschiedlicher direkter und indirekter Verfahren erfolgen. Generell gilt für den gemessenen Abstand L:

$$L = \frac{1}{2} \cdot c \cdot \Delta T \tag{1}$$

Der Faktor c steht dabei für die Lichtgeschwindigkeit, die als konstant angenommen wird und  $\Delta T$  für die gemessene Laufzeit des Lichtpulses. Durch die Multiplikation mit dem Faktor  $\frac{1}{2}$  wird berücksichtigt, dass der reflektierte Lichstrahl die doppelte Strecke L auf dem Weg vom Sender zum Objekt und wieder zurück zum Empfänger zurücklegt, der sich in örtlicher Nähe zum Sender befindet.

Abbildung 1: Time-of-Flight Funktionsprinzip

### 1.1.2 Funktionsprinzip der Kamera

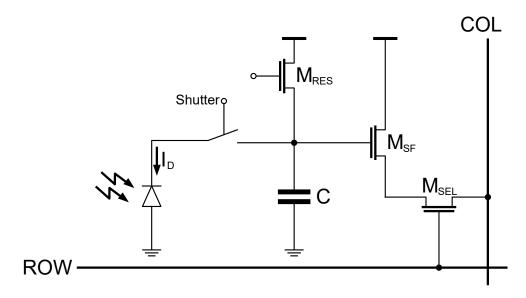

Die Kamera nutzt zur Einhaltung der Augenschutzregularien eine LED für die Erzeugung der gesendeten Lichtpulse. Als Empfänger dient eine Matrix aus lichtempfindlichen Pixelelementen, die auf dem Active-Pixel-Sensor (APS) Funktionsprinzip beruhen. Abbildung 2 zeigt eine vereinfachte Darstellung eines solchen Pixelelements.

Abbildung 2: Vereinfachte Darstellung eines Active-Pixel-Sensors

Eine lichtempfindliche Photodiode wird über einen elektronischen Shutter mit einer Kapazität verbunden. Trifft das reflektierte Licht auf die Diode, hat dies bei geschlossenem Shutter einen Diodenstrom zur Folge, der die Kapazität entsprechend der Lichtintensität entlädt. Der Source-Folger  $M_{SF}$  ermöglicht die Auslesung der Pixelspannung ohne eine Entladung der Kapazität zu verursachen. Über den Transistor  $M_{SEL}$  kann das Pixelelement bei Auswahl der entsprechenden Zeile und Spalte ausgelesen werden. Um das Pi

xelelement zurückzusetzen, wird die Kapazität durch das Schließen des Transistors  $M_{RES}$  wieder auf eine definierte Ausgangsspannung aufgeladen. Um mithilfe dieser Pixelelemente eine Abstandsmessung durchzuführen, werden mehrere Messungen hintereinander durchgeführt.

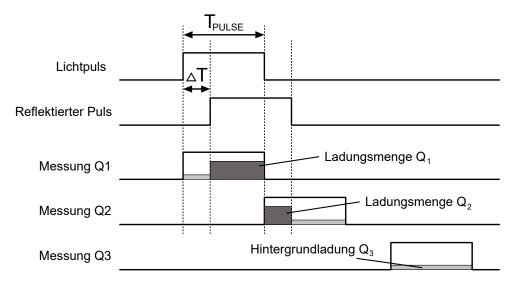

Abbildung 3: Messverfahren der Time-of-Flight Kamera

Wie in Abbildung 3 dargestellt, wird zeitgleich mit dem ausgesandten Lichtpuls eine Messung Q1 gestartet, deren Dauer der Lichtpulslänge  $T_{PULSE}$  entspricht. Trifft während dieser Messung das reflektierte Licht auf den Sensor, wird die Kapazität um eine Ladungsmenge  $Q_1$  entladen. Im direkten Anschluss wird eine zweite Messung Q2 mit gleicher Dauer durchgeführt, bei der eine Ladungsmenge  $Q_2$  entladen wird. Je weiter das zu messende Objekt von Sender und Empfänger entfernt ist, desto größer wird der Anteil der Ladung, der während der zweiten Messung von der Kapazität des Pixels entfernt wird. Daraus ergibt sich folgender Zusammenhang zwischen der Laufzeit des gesendeten Lichtpulses und den Ladungsmengen  $Q_1$  und  $Q_2$ :

$$\frac{\Delta T}{T_{PULSE}} = \frac{Q_2}{Q_1 + Q_2} \tag{2}$$

Da die Pixelelemente zusätzlich zu dem gesendeten Lichtpuls auch vom Umgebungslicht beeinflusst werden, muss die daraus resultierende Ladungsmenge durch eine weitere Messung Q3 ermittelt werden. Diese Messung muss zu einem Zeitpunkt erfolgen, an dem kein von der Lichtquelle gesendeter Lichtpuls eingeht. Die resultierende Ladungsmenge  $Q_3$  wird von jeder Teilladung abgezogen, um den Einfluss des Umgebungslichts auf die Abstandsmessung auszugleichen:

$$\frac{\Delta T}{T_{PULSE}} = \frac{Q_2 - Q_3}{Q_1 + Q_2 - 2Q_3} \tag{3}$$

Durch Umstellen und Einsetzen in Gleichung 1 kann der Abstand zum gemessenen Objekt berechnet werden:

$$L = \frac{1}{2} \cdot c \cdot T_{PULSE} \cdot \frac{Q_2 - Q_3}{Q_1 + Q_2 - 2Q_3} \tag{4}$$

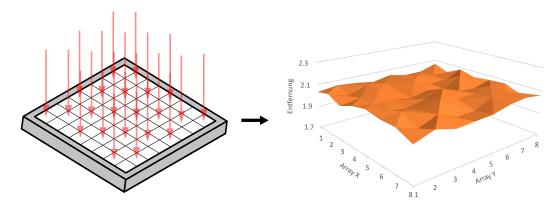

Diese Abstandsmessung wird für jedes Pixelelement der Sensormatrix durchgeführt und die Ergebnisse ausgelesen. Dadurch ergibt sich ein dreidimensionales Abstandsbild, wie in Abbildung 4 dargestellt:

Abbildung 4: Abstandsbild aus Messungen der Pixelmatrix

#### 1.1.3 Einordnung des Time-to-Digital Converters

Die Genauigkeit des beschriebenen Messverfahrens ist stark davon abhängig, ob der Lichtpuls und der Shutter zeitgleich ausgelöst werden. Sind diese Signale nicht synchronisiert, kommt es zu Messfehlern, die sich proportional zur vorhandenen Verzögerung auswirken. Da die Berechnung auf der Lichtgeschwindigkeit beruht, führen bereits Abweichungen im Nanosekundenbereich zu Messfehlern in der Größenordnung von fünfzehn Zentimetern.

Die Steuersignale für die LED-Lichtquelle und die elektronischen Shutter in den Pixelelementen werden, wie in Abbildung 5 dargestellt von einer einzelnen zentralen Steuereinheit erzeugt und sind bei Verlassen dieser Steuerlogik synchron. Beide Signale durchlaufen zunächst Treiber, die auf dem Chip integriert sind. Für die Lichtquelle werden weitere Treiber benötigt, die aufgrund ihrer Stromaufnahme von mehreren Ampere als externe

Abbildung 5: Erzeugung der LED- und Shutter-Signale

Bauelemente realisiert werden müssen. Sowohl die Treiberstufen auf dem Chip als auch die externen LED-Treiber erzeugen Verzögerungen, die zu einer Asynchronität der LED- und Shutter-Signale führen. Besonders die starke Temperaturabhängigkeit der resultierenden Verzögerungszeiten sind für die Distanzmessung von Nachteil, da sich mit wechselnder Temperatur das aufgenommene Distanzbild verschiebt. Neben der Treiberverzögerung ist zusätzlich eine Einschaltverzögerung der Lichtquelle vorhanden, die auch bei idealen, verzögerungsfreien Treibern einen Messfehler zur Folge hat.

Die Kamera verfügt bereits über die Möglichkeit, die Phasenlage der Steuersignale mit einer Auflösung von 1ns zu definieren. Damit kann eine grobe Voreinstellung vorgenommen werden, die allerdings nur zu einer sehr begrenzten Messgenauigkeit führt. Um diese Verzögerungen auch während des Betriebs mit einer deutlich höheren Auflösung auf einen gewünschten Wert regeln zu können, wird ein Time-to-Digital Converter genutzt. Mithilfe des TDC werden die LED- und Shutter-Signale in regelmäßigen Abständen verglichen und deren zeitliche Verzögerung in ein digitales Signal umgewandelt, das mit einer zusätzlichen Kontrolllogik verarbeitet und für die Anpassung der Phasenlage der Signale genutzt werden kann. Damit können temperaturbedingte Veränderungen der Durchlaufzeit der Treiberstufen ausgeregelt und Messfehler deutlich reduziert werden.

## 1.2 Ziele

Das primäre Ziel dieser Masterarbeit ist die Optimierung des vorhandenen Time-to-Digital Converters. In der vorhergehenden Masterstudienarbeit<sup>3</sup> wurde der TDC bereits auf seine Stromaufnahme, seine Auflösung und auf die Homogenität der Verzögerungszeiten zwischen den einzelnen Interpolationsstufen untersucht. Es wurden vor allem bei der inverterbasierten Delay-Line einige Änderungen vorgenommen, die bei der Simulation in einer deutlichen Verbesserung dieser drei Eigenschaften resultierten.

Trotz der vorgenommenen Anpassungen, wurde bei einer simulierten Messung des TDC eine Diskrepanz von mehreren  $T_{LSB}$  zwischen dem real angelegten, zu messenden Zeitintervall und dem Messergebnis festgestellt. Eines der Ziele dieser Arbeit ist daher die Ermittlung der Ursache für diese Diskrepanz und die Anpassung des betreffenden Schaltungsteils um den vorhandenen Messfehler zu verkleinern.

Ein weiteres Ziel ist der Entwurf einer zeitlich variablen Verzögerungskette für den Gesamt-Regelkreis der Anwendung. Da bei dieser Verzögerungskette, im Gegensatz zur Delay-Line des TDC, die Anforderungen an die Genauigkeit der zeitlichen Verzögerung eines einzelnen Elements nur gering sind, wird bei dem Entwurf dieses Schaltungsteils vorrangig darauf geachtet, mit möglichst geringem Aufwand die benötigten Verzögerungszeiten zu erzielen.

Ein bisher nicht betrachteter Faktor ist der Einfluss des Layouts auf die Funktion des TDC. Um festzustellen, in welcher Form und Stärke sich die parasitären Kapazitäten und Widerstände des Layouts unter anderem auf die Homogenität der Verzögerungszeiten zwischen den einzelnen Interpolationsstufen und auf die Gesamtverzögerung der Delay-Line auswirken, wird ein bereits gefertigter Testchip genutzt, auf dem eine ähnliche Ausführung des TDC implementiert ist. Aus der Extraktion der parasitären Kapazitäten und Widerstände und dem Vergleich zwischen den extrahierten und idealen Schaltungsteilen sollen Schlüsse über das Verhalten des optimierten TDC nach Erstellung des Layouts gezogen werden. Sollte bei der Betrachtung der Layout-Effekte auffallen, dass sich das Verhalten des Delay Locked Loop (DLL) deutlich verändert, sind möglicherweise weitere Anpassungen bei der Delay-Line oder anderen Schaltungsteilen notwendig.

Bei der Erstellung des Layouts wird mit der Delay-Line begonnen. Um auch bei der angepassten Schaltung den Einfluss der parasitären Kapazitäten und Widerstände, vor allem auf die Homogenität der Verzögerungszeiten zu ermitteln, sollen nach Erstellung des

$<sup>^{3}[1]</sup>$

Layouts die parasitären Einflüsse extrahiert und beurteilt werden. Sind in Folge weitere Änderungen notwendig, werden diese umgesetzt und die Betrachtungen erneut durchgeführt.

# 2 Theoretische Grundlagen

In diesem Kapitel werden die theoretischen Grundlagen dargelegt, die für das Verständnis der Schaltung, der erzielten Ergebnisse und ihrer Eignung für die Anwendung benötigt werden. Insbesondere wird dabei auf das Funktionsprinzip und die grundlegenden Eigenschaften von Time-to-Digital Convertern eingegangen, welche eine Bewertung der Leistungsfähigkeit erlauben. Da eine Vielzahl von unterschiedlichen analogen und digitalen TDC Ausführungen existiert, kann in dieser Arbeit nur eine Auswahl dieser verschiedenen Schaltungstypen beleuchtet werden. Um einen engen Bezug zur konkreten Anwendung zu wahren, beziehen sich die folgenden theoretischen Ausführungen größtenteils auf digitale TDC, wobei vor allem die Subkategorie der Local Passive Interpolation TDC den Schwerpunkt bildet.

## 2.1 Time-to-Digital Converter

Time-to-Digital Converter (TDC) werden genutzt, um ein zu messendes Zeitintervall in eine diskrete bzw. digitale Repräsentation dieses Zeitraums umzuwandeln. Im Allgemeinen wird unterschieden zwischen analogen und digitalen TDC. Beim analogen TDC-Ansatz wird das Zeitintervall in eine analoge Spannung umgewandelt, welche anschließend mithilfe eines Analog-Digital-Converters (ADC) digitalisiert wird. Da TDCs in analoger Ausführung einige Beschränkungen sowohl in Hinsicht auf die Austauschbeziehung zwischen maximal messbarem Zeitintervall und dabei erzielbarer Auflösung, als auch in ihrer Anwendung im Rahmen von Mixed-Signal Systemen aufweisen<sup>4</sup>, kommen in hochintegrierten Schaltungen besonders digitale TDC zum Einsatz.

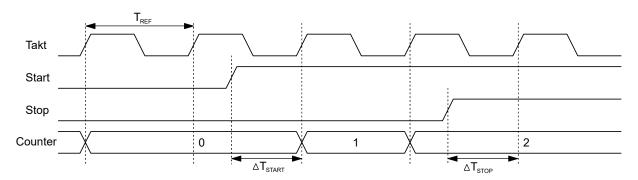

Digitale TDC nutzen zur Quantisierung des Zeitintervalls einen Referenztakt. Im einfachsten Anwendungsfall wird das Messergebnis berechnet, indem gezählt wird, wieviele Taktzyklen in das zu messende Zeitintervall fallen. Das Messintervall wird hierbei durch ein Start- und ein Stop-Signal begrenzt. Wie in Abbildung 6 dargestellt, entstehen bei dieser Art der Messung Quantisierungsfehler  $\Delta T_{START}$  und  $\Delta T_{STOP}$ , die aus der Asynchronität von Takt- und Zeitsignalen resultieren.

Für das gemessene Zeitintervall gilt:

<sup>&</sup>lt;sup>4</sup>[2], S. 8-11

Abbildung 6: Quantisierung eines Zeitintervalls mithilfe eines zählerbasierten TDC

$$\Delta T = N \cdot T_{REF} + (T_{REF} - \Delta T_{STOP}) - (T_{REF} - \Delta T_{START}) \tag{5}$$

Wobei N die Anzahl der gemessenen Taktperioden und  $T_{REF}$  die Periodendauer angibt. Die Auflösung eines solchen TDC ist durch die Frequenz des Taktsignals limitiert. Da eine Erhöhung des Taktsignals ab einer bestimmten Grenze nicht ohne erheblichen Entwurfsund Kostenaufwand realisierbar ist, wird auf alternative Methoden zur Erhöhung der Messgenauigkeit zurückgegriffen.

## 2.1.1 Delay-Line basierte TDC

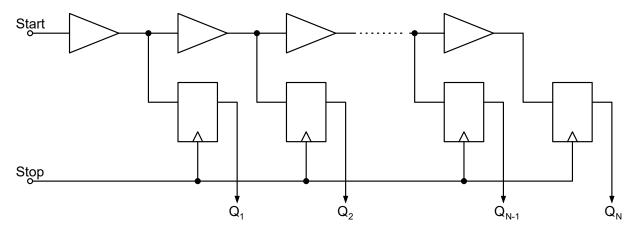

Eine Möglichkeit zur Erhöhung der Auflösung eines TDC ist die Unterteilung einer Taktperiode in kleinere Zeitabschnitte. Um dies zu erreichen, kann eine Kette aus identischen Verzögerungselementen genutzt werden (engl. delay-line), die phasenverschobene Duplikate des Referenztaktes erzeugen. Abbildung 7 zeigt den prinzipiellen Aufbau eines Delay-Line basierten TDC (DL-TDC).

Das Taktsignal, welches in dieser Anwendung gleichzeitig das Start-Signal der Zeitmessung darstellt, wird durch die Delay-Elemente verzögert und nach jedem Element als Dateneingang für ein Latch oder Flipflop verwendet. Das Stop-Signal wird als Takteingang für alle Speicherelemente der Delay-Line genutzt. Bei Eintreffen des Stop-Signals wird folglich in allen Speicherelementen, an denen bereits das Start-Signal anliegt, ein logischer HIGH-Pegel gespeichert, während alle übrigen Elemente ein logischen LOW-Wert aufweisen. Hierdurch entsteht ein Thermometer-Code, dessen HIGH - LOW Übergang angibt, wie viele Delay-Elemente das Start-Signal passiert hat, bis das Stop-Signal eingetroffen ist<sup>5</sup>. Für das gemessene Zeitintervall gilt bei dieser Vorgehensweise:

<sup>&</sup>lt;sup>5</sup>[2], S. 14

Abbildung 7: Aufbau eines Delay-Line basierten TDC

$$\Delta T = N \cdot T_{LSB} + \epsilon \tag{6}$$

wobei N für die Anzahl der Speicherelemente mit logischem HIGH Pegel steht,  $T_{LSB}$  die Verzögerungszeit eines einzelnen Delay-Elements und damit gleichzeitig die Auflösung angibt, und  $\epsilon$  den Quantisierungsfehler beschreibt, der dadurch entsteht, dass die Flipflops sich nur im HIGH oder LOW Zustand befinden können. Zwischenzustände können nicht erkannt werden.

Als Delay-Elemente können sowohl Bufferstufen, bestehend aus zwei CMOS Invertern, oder einfache Inverter genutzt werden. Die Nutzung von Invertern hat den Vorteil, dass die Auflösung des TDC erneut verdoppelt wird. Allerdings ist zu beachten, dass durch die invertierende Wirkung der Delay-Elemente sowohl die steigende als auch die fallende Flanke des Taktsignals zur Messung genutzt werden. Dies hat zum einen zur Folge, dass anstatt des Thermometer-Codes ein Pseudo-Thermometer-Code mit abwechselnden HIGH und LOW Zuständen entsteht. Das Ende des Zeitintervalls wird durch einen Phasenwechsel im Code deutlich, wie in Abbildung 8 gezeigt.

##

Abbildung 8: Ausgangs-Code bei Nutzung von Buffer- oder Inverter-Verzögerungselementen

Zum anderen wird durch die Nutzung beider Taktflanken eine Nichtlinearität in das System eingeführt, da die Verzögerung der Inverter für steigende und fallende Flanken unterschiedlich groß sein kann. Dieser Effekt wird durch Prozessvariationen und Tempera-

tureinflüsse verstärk $t^6$ .

### 2.1.2 Leistungsmerkmale von TDC

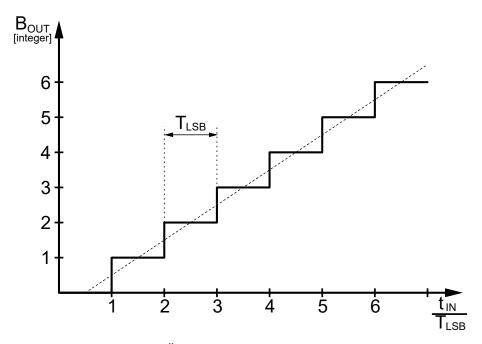

Das Zeitintervall, das als Eingangssignal für den TDC dient, wird in einen diskreten Ausgangswert umgewandelt. Dies hat die Eingangs-Ausgangscharakteristik, die in Abbildung 9 abgebildet ist, zur Folge.

Abbildung 9: Übertragungsfunktion des idealen TDC

Da ein kontinuierlicher Wert in einen diskreten Wert umgewandelt wird, wird folglich eine Reihe von Zeitwerten in den gleichen diskreten Ausgangswert überführt. Wie in Abbildung 9 dargestellt führt dies zu einer stufenförmigen Übertragungsfunktion des TDC, wobei die Breite jeder dieser diskreten Stufen immer den Zeitraum von  $T_{LSB}$  besitzt, welcher der Auflösung des TDC entspricht. Dies setzt jedoch voraus, dass jede einzelne Verzögerungsstufe der genutzten Delay-Line exakt die selbe Verzögerungszeit aufweist. In diesem idealen Fall entspricht das Messergebnis bis auf den Quantisierungsfehler dem zugeführten Zeitintervall. In einer realen Anwendung können sich die Verzögerungszeiten der einzelnen Verzögerungsstufen allerdings voneinander unterscheiden, ohne dass dabei die Gesamtverzögerung der Delay-Line vom eingeregelten Wert variiert. Auch wenn alle Delay-Elemente gleich ausgelegt sind, führen zufällige Abweichungen im Fertigungsprozess zu unterschiedlichen Verzögerungszeiten. Dieser Unterschied zwischen scheinbar

<sup>&</sup>lt;sup>6</sup>[2], S. 16

identischen Bauelementen wird auch als Mismatch bezeichnet. Um das reale Verhalten des TDC zu charakterisieren, gibt es Kenngrößen, die die Qualität eines TDC und vorhandene Messabweichungen beschreiben.

#### Differentielle Nichtlinearität

Die differentielle Nichtlinearität (DNL) eines TDC beschreibt die Abweichung der Schrittweite jedes Zeitschritts von dessen Idealwert  $T_{LSB}^{7}$ . Zur Berechnung des zeitlichen Wertes der DNL an jeder Position der Delay-Line wird die ideale Schrittweite des TDC  $T_{LSB}$  von der realen Schrittweite an der Position i abgezogen:

$$t_{DNL,i}$$

= Reale Schrittweite an Position i – Ideale Schrittweite

=  $T_{LSB,i} - T_{LSB} = t_{i+1} - t_i - T_{LSB}$  (7)

Häufig wird die differenzielle Nichtlinearität auf die ideale Schrittweite bezogen und in der Einheit LSB angegeben:

$$DNL_i = \frac{T_{LSB,i}}{T_{LSB}} - 1 \tag{8}$$

Für jedes Element der Delay-Line kann ein separater Wert für die DNL angegeben werden. Um die Güte der gesamten Delay-Line in Bezug auf die DNL zu quantifizieren, kann die Standardabweichung der DNL über die gesamte Länge der Delay-Line berechnet werden:

$$\sigma_{DNL} = \sqrt{\frac{\sum_{i=0}^{N} DNL_i^2}{N}} \tag{9}$$

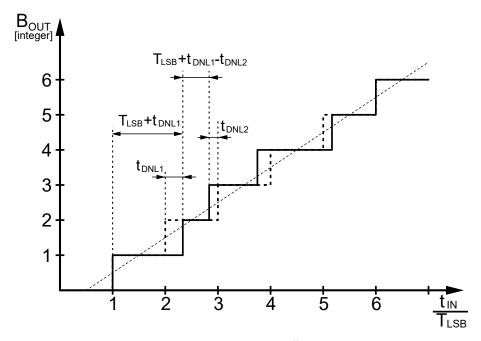

Abbildung 10 zeigt die Auswirkung der DNL auf die Übertragungsfunktion eines realen TDC. Die Schrittweiten können sowohl breiter als auch schmaler als die ideale Schrittweite ausfallen. Die differentielle Nichtlinearität kann folglich auch negative Werte annehmen.

<sup>&</sup>lt;sup>7</sup>[2], S. 24, 38

Abbildung 10: Auswirkung der DNL auf die Übertragungsfunktion des TDC

### Integrale Nichtlinearität

Die Integrale Nichtlinearität (INL) ist eine quantitative Beschreibung der Krümmung der TDC-Charakteristik<sup>8</sup>. Sie gibt an, wie stark die reale Schrittposition von der idealen Position abweicht. Der real gemessene Wert am Verzögerungselement i wird mit dem idealen Wert an derselben Position verglichen:

$$t_{INL,i} =$$

Gemessener Zeitwert an Position i – Idealer Zeitwert an Position i

=  $t_i - i \cdot T_{LSB}$  (10)

Die INL wird üblicherweise ebenfalls bezogen auf ein  $T_{LSB}$  dargestellt:

$$INL_i = \frac{t_i}{T_{LSB}} - i \tag{11}$$

Bezogen auf die gesamte Delay-Line, kann die Standardabweichung der INL angegeben werden als:

<sup>&</sup>lt;sup>8</sup>[2], S. 24

$$\sigma_{DNL} = \sqrt{\frac{\sum_{i=0}^{N} INL_i^2}{N}} \tag{12}$$

## 2.2 Delay-Locked-Loop basierte TDC

Delay-Line basierte TDC nutzen Verzögerungselemente, deren Verzögerung von Prozess-variationen, Temperatur und ihrer Versorgungsspannung abhängt<sup>9</sup>. Daher kann ohne eine Kalibration vor dem Messvorgang keine Angabe über den gemessenen Zeitwert gemacht werden. Es kann nur festgestellt werden, wie viele der Verzögerungselemente während der Messung durchlaufen wurden.

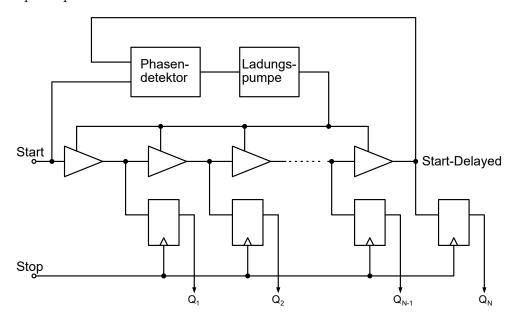

Um eine Kalibration vor der Messung zu umgehen und dennoch eine absolute Aussage über das gemessene Zeitintervall machen zu können, ist die Nutzung eines Delay-Locked-Loop basierten Time-to-Digital Converter (DLL-TDC) möglich. Abbildung 11 zeigt das Funktionsprinzip des DLL-TDC.

Abbildung 11: Funktionsprinzip des DLL-TDC

Eine Delay-Line, bestehend aus Inverter- oder Buffer-Elementen, wird durch die Einbindung in einen Regelkreis auf eine feste Gesamtverzögerung geregelt. Der Referenztakt, der als Eingangssignal der Delay-Line und gleichzeitig als Start-Signal fungiert, wird am Anfang und Ende der Delay-Line abgegriffen. Die beiden zueinander verzögerten Signale werden mithilfe eines Phasendetektors auf ihre Phasenlage verglichen. Ziel ist es, die

<sup>&</sup>lt;sup>9</sup>[2], S. 53

Gesamtverzögerung der Delay-Line auf eine Taktperiode des Eingangstakts einzuregeln. Trifft die steigende Taktflanke des verzögerten Signals zuerst beim Phasendetektor ein, ist die Verzögerung zu kurz. Eilt die steigende Flanke des Eingangstakts dem verzögerten Signal vor, ist die Verzögerung der Delay-Line zu lang.

Eine Ladungspumpe (engl. charge pump) verarbeitet die entsprechenden Ausgangssignale des Phasendetektors und erzeugt eine Spannung, mit der die Verzögerungselemente versorgt werden. Eine niedrigere Versorgungsspannung führt zu einer höheren Gesamtverzögerung, eine höhere Versorgungsspannung zu einer niedrigeren Verzögerungszeit.

Ist die Delay-Line auf die gewünschte Verzögerungszeit eingeregelt, kann der aus einer Messung resultierende Thermometer-Code $^{10}$  in ein Zeitintervall umgerechnet werden, indem die Anzahl der HIGH geschalteten Flipflops mit der zeitlichen Verzögerung eines einzelnen Elements multipliziert wird.

Zu beachten ist bei dieser Anwendung, dass die Ladungspumpe bei Implementationen mit langen Messintervallen und kleinen Auflösungen eine Vielzahl an Verzögerungselementen treiben muss. Für einen stabileren Betrieb des DLL-TDC wird ein Spannungsregler zwischen Ladungspumpe und Delay-Line geschaltet, der in der Lage ist, die Verzögerungselemente mit dem benötigten Strom zu versorgen, ohne dass Schwankungen in der Versorgungsspannung auftreten.

# 2.3 TDC mit Sub-Gate-Delay

Die bisher betrachteten TDC sind in ihrer Auflösung limitiert auf die Verzögerungzeit eines einzelnen Delay-Elements. Um die Auflösung weiter zu erhöhen, kann bei diesen TDC nur auf die Verwendung einer schnelleren CMOS Technologie zurückgegriffen werden. Um diese Technologie-Abhängigkeit zu umgehen, gibt es unterschiedliche Techniken, die eine Auflösung unterhalb des Gate-Delays eines einzelnen Inverters zulassen. Beispiele für diese Arten von TDC sind Anwendungen mit parallel geschalteten Delay-Elementen, Vernier-TDC oder Pulse Shrinking TDC. Diese TDC-Ausführungen werden an dieser Stelle nur beispielhaft genannt. Genauer betrachtet wird jedoch der Local Passive Interpolation TDC, da die vorhandene Anwendung auf diesem Funktionsprinzip beruht.

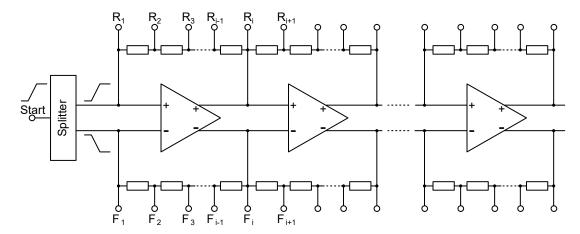

Der LPI-TDC nutzt eine Delay-Line mit Inverter-Verzögerungselementen, zwischen deren Ein- und Ausgängen Interpolationselemente eingefügt werden. Als Verzögerungselemente

<sup>&</sup>lt;sup>10</sup>Siehe Abschnitt 2.1.1

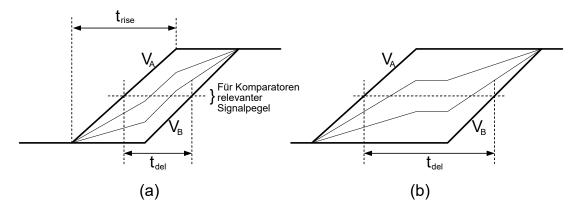

bieten sich differenzielle Inverter an, da diese in der Lage sind logisch äquivalente Signale mit einer Verzögerung eines einzelnen Inverters zu erzeugen. Diese Eigenschaft ist für die Funktion der Interpolation wichtig. In Abbildung 12 (a) ist das Prinzip der Local-Passive-Interpolation dargestellt.

Abbildung 12: Funktionsprinzip der LPI (a) und LPI mit zu starker Verzögerung (b)

Die beiden fett gezeichneten äußeren Linien stellen das in ein Delay-Element eingehende Taktsignal  $V_A$  und dessen Ausgangssignal  $V_B$  dar, die um die Verzögerungszeit des Elements  $t_{del}$  verschoben sind. Die dünner gezeichneten Linien zeigen die aus den Interpolationselementen resultierenden Signale  $V_{int,i}$ , die berechnet werden können zu:

$$V_{int,i} = V_B + a_i(V_A - V_B) \tag{13}$$

Der Faktor  $a_i$  steht für den Interpolationskoeffizienten, der von der Anzahl der Interpolationselemente abhängt. Beispielsweise ergibt sich mit zwei Interpolationselementen ein  $a_i$  von  $\frac{1}{2}$ , mit drei Elementen die Faktoren  $a_i = \{\frac{1}{3}, \frac{2}{3}\}$ . Generell gilt für den Interpolationskoeffizienten:

$$a_i = \frac{i}{IF}$$

$$i = 1...(IF - 1)$$

(14)

IF steht für den Interpolationsfaktor, der die Anzahl der Interpolationselemente angibt. Aus Gleichung 13 und aus Abbildung 12 (b) wird deutlich, warum die Verzögerung zwischen den Signalen  $V_A$  und  $V_B$  und die Anstiegszeit  $t_{rise}$  dieser Signale ausschlaggebend für die Funktion des LPI-TDC sind. Ist die Verzögerung zwischen den Signalen zu groß bzw. ist die Anstiegszeit zu schnell, ergibt sich ein deutlich abweichender Verlauf der

interpolierten Spannungen.

Wichtig für die Messung sind die Abstände der Signale bei 50% ihrer Amplituden, da die interpolierten Signale bei Eintreffen des Stop-Signals mithilfe von Komparatoren abgeglichen werden, deren Schwelle sich in diesem Bereich befindet. Anhand der Abbildung 13, die den prinzipiellen Aufbau eines LPI-TDC zeigt, kann der Ablauf der Messung nachvollzogen werden.

Abbildung 13: Aufbau des LPI-TDC

Wie in den bisher betrachteten Anwendungen wird ein Taktsignal gleichzeitig als Start-Signal für die Zeitmessung genutzt. Dieses Start-Signal wird mithilfe eines Splitters, beispielsweise eines einfachen Inverters, in zwei entgegengesetzt verlaufende Signale verzweigt. Die differenziellen Inverter der Delay-Line werden so verschaltet, dass die Interpolationselemente sich jeweils zwischen zwei Signalen gleicher Polarität befinden. Zu Beginn der Messung befinden sich die Zwischenstufen  $R_i$  im LOW Zustand, die Interpolationsstufen  $F_i$  im Zustand HIGH. Bei Durchlaufen des Start-Signals durch die Delay-Line werden die Zustände der Interpolationsstufen  $R_i$  und  $F_i$  umgekehrt. Bei Eintreffen des Stop-Signals kann mithilfe von Komparatoren festgestellt werden, wie weit diese Umkehrung die Delay-Line passiert hat. Daraus kann das vergangene Zeitintervall berechnet werden.

Als Interpolationselemente können ohmsche Widerstände genutzt werden. Die Anzahl der Elemente und die Verzögerung des differenziellen Inverters bestimmen die Auflösung des LPI-TDC. Ein Vorteil dieser Konfiguration ist, das die Auflösung des TDC erhöht werden kann, ohne die Länge der Delay-Line zu verändern. Die Anzahl und Größe der Interpolationselemente ist allerdings limitiert.

## 2.4 Parasitäre Einflüsse des Layouts

Bei der physischen Implementierung einer Schaltung müssen parasitäre Effekte des Layouts in die Betrachtung einbezogen werden, um das reale Verhalten nach der Fertigung beurteilen zu können. Sowohl das Halbleitermaterial, in dem die Transistoren gefertigt werden, als auch die Metallschichten bringen potenziell parasitäre Widerstände, Kapazitäten, Dioden oder Transistoren in das Design ein, welche die Funktion der Schaltung beeinträchtigen können. Einige dieser parasitären Layout-Effekte sollen in diesem Kapitel betrachtet werden.

#### 2.4.1 Substrateffekte

In dem Substrat eines Halbleiter-Chips befindet sich eine Vielzahl von n- und p-dotierten Regionen, in denen die Transistoren gefertigt werden. Diese dotierten Regionen besitzen einerseits einen ohmschen Widerstand und zum anderen formen sie parasitäre Dioden und Bipolartransistoren, die bei Entwurf des Layouts berücksichtigt werden müssen.

## Änderung des Substratpotenzials

In einem Prozess mit p-dotiertem Substrat wird das Potenzial dieses Substrats typischerweise als Bezugspotenzial oder auch Masse verwendet. Dieses Potenzial ist im Idealfall konstant und behält seinen Wert auch bei Betrieb der auf dem Chip gefertigten Schaltung bei. Der endliche ohmsche Widerstand des Substratmaterials hat allerdings zur Folge, dass auftretende Substratströme zur lokalen Erhöhung des Substratpotenzials mit einem Wert von

$$\Delta V = R_{Sub} \cdot I_{Sub} \tag{15}$$

führen. Substratströme sind in jedem Fall unerwünscht, daher ist bei Erstellung des Layouts sicherzustellen, dass auftretende Substratströme auf dem kürzesten Weg das Substrat wieder verlassen. Um die lokale Potenzialveränderung im Substrat möglichst gering zu halten, werden oft stark dotierte Substrate, d.h. Substrate mit geringem Widerstand, mit einer gering dotierten Schicht an der Oberfläche genutzt<sup>11</sup>. Die leicht dotierte Oberfläche ist in diesem Fall notwendig, um eine Umdotiertung des Materials zur Fertigung

<sup>&</sup>lt;sup>11</sup>[3], S. 258

der Transistoren weiterhin zu ermöglichen. Abbildung 14 zeigt eine Substratstromquelle, in diesem Fall ein parasitärer PNP-Bipolartransistor (rot), die aus dem Layout eines NPN-Bipolartransistors resultiert.

Abbildung 14: Parasitäre Substratstromquelle

Da Substratströme nicht in jedem Fall verhindert werden können, ist es notwendig, so nah wie möglich an der parasitären Stromquelle einen Substratkontakt zu platzieren, über den der Strom aus dem Substrat abfließen kann. Häufig werden dafür sogennannte "Guard-Rings" genutzt. Der betreffende Schaltungsteil wird komplett mit einem Substratkontakt umgeben, um einen Substratstromfluss in angrenzende Schaltungsteile zu verhindern.

### Latchup

Als Latchup bezeichnet man die Entstehung eines parasitären Thyristors, bestehend aus zwei parasitären Bipolartransistoren, der einen unerwünschten niederohmigen Pfad zwischen zwei MOS-Transistoren erzeugt. Eine typische Schaltung, bei der dieser Effekt auftreten kann, ist ein Inverter, bei dem ein NMOS und ein PMOS Transistor direkt nebeneinander gefertigt werden. Abbildung 15 zeigt das vereinfachte Layout eines CMOS-Inverters, mit den parasitären Bipolartransistoren, die aus den NPN- und PNP-Übergängen aus Source/Drain Anschluss, Wanne und Substrat resultieren.

Der Latchup-Effekt wird ausgelöst, wenn einer der beiden Bipolartransistoren in einen leitenden Zustand versetzt wird. Durch positives Feedback im Thyristor wird der Stromfluss durch die beiden parasitären Transistoren solange aufrecht erhalten, bis die Versorgungsspannung entfernt wird. Ursache für das Latchup sind häufig Spannungsspitzen bei Masse oder Versorgungsspannung. Aber auch Eingangssignale mit steilen Flanken können über die Gate-Drain Kapazitäten der Transistoren für Änderungen der Ausgangsspannung führen, die in Folge einen Stromfluss über den parasitären Thyristor erzeugen. Um Latchup

Abbildung 15: Parasitärer Thyristor bei einem CMOS-Inverter

zu verhindern sollten die Widerstände  $R_{WELL}$  und  $R_{SUB}$  so gering wie möglich gehalten werden. Dies ist vor allem durch eine ausreichende und nah an den MOS-Transistoren gelegene Kontaktierung von Substrat und Wanne möglich.

#### 2.4.2 Oberflächeneffekte

Die zahlreichen unterschiedlich dotierten Flächen auf einem Chip können neben den bisher betrachteten parasitären Bipolartransistoren auch parasitäre MOS-Transistoren zur Folge haben. In Abbildung 16 ist ein solcher Feld-Oxid (FOX) Transistor dargestellt.

Abbildung 16: Parasitärer NMOS-Transistor durch Oberflächeneffekte

Zwei nebeneinander liegende N-Wannen formen die Source- und Drain-Anschlüsse des Transistors. Verläuft ein Leiter mit hohem Potenzial über dem zwischen den Wannen liegenden Oxid, kann sich ein parasitärer Kanal bilden und ein unerwünschter Strom zwischen den beiden N-Wannen fließen, insofern diese unterschiedliche Potenziale aufweisen.

Diese parasitären Einflüsse spielen vor allem bei Chips mit hohen Betriebsspannungen eine Rolle. In Anwendungen mit niedrigen Betriebsspannungen reichen die Potenzialunterschiede oft nicht aus um durch Inversion einen parasitären Kanal zwischen den zwei

Regionen zu formen<sup>12</sup>. Um diesem Effekt vorzubeugen, werden bei vielen modernen Fertigungsprozessen sogenannte "channel-stop implants" eingefügt, welche die effektive Schwellenspannung von FOX Transistoren deutlich erhöhen.

#### 2.4.3 Einfluss der Metallschichten

Die Metalllagen in einem CMOS-Prozess werden genutzt, um die im Substrat gefertigten Schaltungsteile miteinander zu verbinden. Diese Metallverbindungen bringen, ähnlich wie Kabelverbindungen in Schaltungen aus diskreten Bauelementen, ohmsche, kapazitive und induktive Komponenten in das Design ein. Während die induktiven Anteile bei Signalfrequenzen unterhalb von einigen Gigahertz eine untergeordnete Rolle spielen<sup>13</sup>, können sich die parasitären ohmschen Widerstände und Kapazitäten deutlich auf die Funktion des Chips auswirken.

### Leitungsverluste und Signalverzerrung

Der ohmsche Widerstand einer metallischen Leiterbahn kann mithilfe des Schichtwiderstands (engl. sheet resistance)  $R_{Sh}$  berechnet werden. Der Widerstand eines homogenen Leitermaterials wird über die Formel

$$R = \rho \cdot \frac{l}{A} \tag{16}$$

bestimmt. Der Faktor  $\rho$  beschreibt dabei den spezifischen elektrischen Widerstand des Materials, l die Länge der Leiterbahn, die vom Strom durchflossen wird und A die zugehörige Querschnittsfläche, wie in Abbildung 17 dargestellt.

Abbildung 17: Dimensionen der Metallbahnen

$<sup>^{12}[3]</sup>$ , S. 268

<sup>&</sup>lt;sup>13</sup>[3], S. 272

Da die Metallbahnen in Halbleiterprozessen größtenteils flache, annähernd rechteckige Strukturen aufweisen, kann die Querschnittsfläche durch die Multiplikation der Tiefe t und Breite w der Metallbahnen errechnet werden. Damit ergibt sich für den Widerstand

$$R = \rho \cdot \frac{l}{t \cdot w} \tag{17}$$

Die Tiefe der Metalllagen ist durch den gewählten Prozess vorgegeben und über das gesamte Layout konstant. Daher wird der Schichtwiderstand  $R_{Sh}$  genutzt um die Widerstandsberechnung zu vereinfachen:

$$R_{Sh} = \frac{\rho}{t} \tag{18}$$

Damit gilt für den Gesamtwiderstand R:

$$R = R_{Sh} \cdot \frac{l}{w} \tag{19}$$

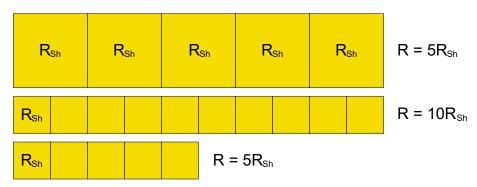

Setzt man die Breite und und Länge gleich, erhält man den Widerstandswert für einen quadratischen Ausschnitt der betrachteten Leiterbahn. Die Größe dieses Quadrats spielt bei der Berechnung des Widerstands keine Rolle, da der Widerstandswert auch bei Skalierung konstant bleibt. Diese Eigenschaft ist nützlich für die Abschätzung des Widerstands einer Metallbahn, da anstatt einer Berechnung des Gesamtwiderstands einfach die Zahl der Quadrate gezählt werden kann. Abbildung 18 zeigt eine schematische Darstellung dieses Funktionsprinzips.

Abbildung 18: Schichtwiderstand in Metallbahnen

Der Strom, der durch die Metallbahnen fließt, hat zum einen thermische Verluste der Höhe  $I^2 \cdot R$  zur Folge, zum anderen bewirkt er einen Spannungsabfall über den Widerstand des

Leiters in Höhe von  $I \cdot R$ . Folglich unterscheidet sich das Potenzial am Anfang des Leiters vom Potenzial am Leiterende. Um hohe Spannungsabfälle zu vermeiden, kann die Breite der Leiterbahnen und damit der Gesamtwiderstand verringert werden. Zusätzlich sollte die Platzierung auf dem Chip so gewählt werden, dass die Leiterlänge bei hohen Strömen möglichst gering ist.

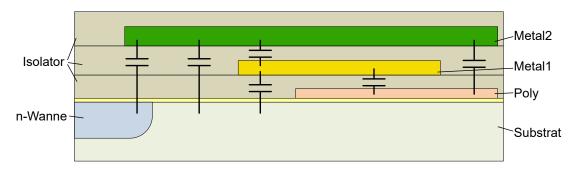

Die dünnen Schichten und damit kleinen Abstände zwischen den unterschiedlichen Schichten eines Halbleiterprozesses haben teilweise signifikante Kapazitäten zwischen Metallund Substratschicht oder zwischen unterschiedlichen Metallschichten zur Folge. Abbildung 19 zeigt eine schematische Darstellung verschiedener parasitärer Kapazitäten zwischen übereinander verlaufenden Schichten.

Abbildung 19: Parasitäre Kapazitäten zwischen den Schichten eines Layouts

Die Widerstände und Kapazitäten, die mit den Leiterbahnen einhergehen, haben eine RC-Verzögerung zur Folge, die beim Entwurf des Layouts beachtet werden muss, da diese Verzögerung zu signifikanten Verzerrung des gewünschten Signals führen kann. Eine Verkürzung von Leiterbahnen reduziert auch die Widerstands- und Kapazitätskomponenten. Die Nutzung breiterer Metallschichten hat bei Widerstand und Kapazität einen gegenläufigen Effekt. Der parasitäre Widerstand des Leiters wird reduziert, die Kapazität durch die Vergrößerung der Oberfläche erhöht. In den meisten Fällen ist die Verringerung des Widerstands der dominante Faktor für die resultierende RC-Verzögerung, daher führen breitere Leiterbahnen zu einem geringeren Einfluss auf das Signal, das auf dem Leiter geführt wird.

Die Kapazitätswerte zwischen den unterschiedlichen Schichten sind vom genutzten Prozess abhängig und werden durch geeignete Teststrukturen ermittelt.

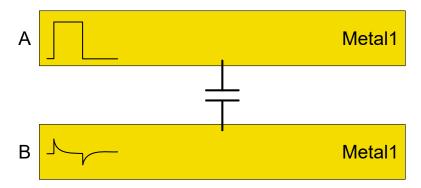

#### Crosstalk

Neben den parasitären Kapazitäten zwischen Leiterbahnen und der Substratschicht befinden sich auch zwischen Leiterbahnen auf der gleichen Metallebene Kapazitäten. In

Abbildung 20 sind die Kapazitäten zwischen zwei nebeneinander verlaufenden Metall1-Leiterbahnen dargestellt.

Abbildung 20: Crosstalk zwischen Metallbahnen

Durch ein auf Leiter A verlaufendes Spannungssignal wird ein Strom  $I_{Cross}$  mit der Größe

$$I_{Cross} = C_{Cross} \cdot \frac{dV_A}{dt} \tag{20}$$

auf den Leiter B gekoppelt und das auf Leiter B anliegende Potenzial dementsprechend beeinflusst. Die parasitäre Kapazität kann durch eine Vergrößerung des Abstands zwischen den Leiterbahnen verringert werden. Mit der starken Skalierung der Halbleitertechnologie und dementsprechend immer kleiner werdenden Abständen gewinnen diese parasitären Einflüsse jedoch zunehmend an Bedeutung. Vor allem bei der Kombination aus digitalen Schaltungen, die typischerweise mit hoher Flankensteilheit betrieben werden, und analogen Schaltungen, die empfindlich auf kleine Potenzialänderungen reagieren, ist es sinnvoll, die unterschiedlichen Schaltungsteile voneinander zu isolieren.

## 2.5 Matching

Die zahlreichen Fertigungsschritte eines CMOS-Prozesses sind unvermeidlich mit Fertigungstoleranzen verbunden, welche die elektrischen Parameter der auf einem Chip genutzten Bauelemente beeinflussen. Auch wenn diese Toleranzen sehr kleine Werte annehmen, ergeben sich aus der Summe der Toleranzen aller Fertigungsschritte deutliche Abweichungen zwischen scheinbar identischen Bauelementen. Werden Bauelemente auf dem gleichen Chip gefertigt, sind sie ähnlichen Einflüssen bei der Fertigung ausgesetzt und weisen daher deutlich geringere Unterschiede als Bauelemente auf, die auf unterschiedlichen Chips, unterschiedlichen Wafern oder in verschiedenen Produktionszyklen gefertigt werden. Im

besten Fall sind die Unterschiede mehrerer gleich ausgelegter Bauelemente so gering, dass sie sich nicht merklich auf die Funktion einer Schaltung auswirken. Das Verringern bzw. das Verhindern dieser Unterschiede durch geeignete Schritte im Layout-Prozess wird Matching genannt.

Die Funktion einiger sehr häufig genutzter Schaltungen beruht auf der Symmetrie der genutzten Bauelemente. Daher ist gutes Matching bei diesen Schaltungen unbedingt erforderlich. Dazu zählen unter anderem Stromspiegel, differenzielle Eingangsstufen von Operationsverstärkern, Spannungsreferenzen oder auch resistive Spannungsteiler. Die relative Abweichung der elektrischen Parameter kann durch bestimmte Layout-Techniken deutlich verbessert werden. Einige davon sollen in den folgenden Abschnitten vorgestellt werden.

#### 2.5.1 Einheitselemente

Die elektrischen Parameter von Bauelementen in CMOS-Prozessen sind proportional zur Größe der Strukturen im Layout. Diese Parameter können folglich durch eine Skalierung im Layout verändert werden. Bei der Fertigung dieser Bauelemente werden allerdings Randeffekte (engl. *fringe effects*) erzeugt, die ihre Größe bei Skalierung der Bauelemente nicht verändern und sich auf die Parameter von Bauelementen auswirken<sup>14</sup>. Die Tatsache, dass diese Effekte sich nicht proportional zur Skalierung der Bauelemente verändern, hat zur Folge, dass die Auswirkungen der Randeffekte bei kleinen Bauelementen deutlich stärker sind als bei räumlich großen Bauelementen.

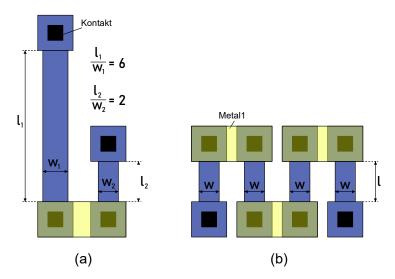

Um dieses Mismatch zwischen Bauelementen zu vermeiden, bietet es sich an, Elemente mit Einheitsgrößen zu verwenden. Durch die gleiche Dimensionierung wirken die Randeffekte gleich stark auf alle Bauelemente und der relative Fehler wird ausgeglichen. Abbildung 21 zeigt das Prinzip bei der Auslegung zweier Widerstände für einen resistiven 3:1 Spannungsteiler.

Die Widerstände im linken Teil der Abbildung unterscheiden sich sowohl in ihrer Breite als auch in ihrer Länge. Die Randeffekte bewirken aufgrund der kleineren Dimensionen deutlich stärkere Veränderungen des gewünschten Widerstandswerts bei Widerstand  $R_2$  als bei  $R_1$ . Im rechten Teil der Abbildung ist der selbe Spannungsteiler, allerdings aufgebaut aus Einheitselementen, gezeigt. Die bei allen Widerständen gleichen Dimensionen

<sup>&</sup>lt;sup>14</sup>[3], S. 241f

Abbildung 21: Layout eines Spannungsteilers mit (a) und ohne (b) Matching

haben zur Folge, dass sich die Randeffekte auf die effektiven Widerstandswerte aller Teilwiderstände gleich auswirken. Da bei einem ohmschen Spannungsteiler nicht die eigentlichen Widerstandswerte, sondern das Größenverhältnis für die Funktion entscheidend ist, wird der Spannungsteiler aus Abbildung 21 (b) eine Ausgangsspannung bewirken, die deutlich näher am gewünschten Wert liegt, als die Ausgangsspannung des Spannungsteilers aus unterschiedlich dimensionierten Widerständen.

Die gleiche Technik kann für das Matching von MOS-Transistoren angewendet werden. Die Randeffekte bewirken bei den Transistoren eine Änderung der effektiven Breite und Kanallänge. Um auch in diesem Fall den relativen Fehler zwischen zwei Bauelementen zu verringern, sollten Transistoren mit gleichen Dimensionen verwendet werden. Um die Länge und Breite bei der Nutzung von Einheitselementen zu verändern werden mehrere Transistoren in Reihe oder parallel geschaltet. Abbildung 22 zeigt das Layout eines einfachen Stromspiegels, mit dem der Referenzstrom  $I_{REF}$  gespiegelt und verdoppelt werden soll.

#### 2.5.2 Ortsabhängige Prozessgradienten

Wie bereits beschrieben, haben die Toleranzen bei der Fertigung eines Halbleiterchips zur Folge, dass sich bestimmte Parameter von Bauelementen an unterschiedlichen Stellen des Wafers oder des Chips voneinander unterscheiden. Um die Auswirkungen dieser örtlichen Änderungen zu verdeutlichen, wird der Sachverhalt anhand eines Beispiels erläutert, bei dem die Tiefe des Gateoxids über die Fläche eines Chips aufgrund von Fertigungstole-

Abbildung 22: Layout eines Stromspiegels ohne (a) und mit (b) Matching

ranzen leicht variiert. Abbildung 23 zeigt die Oxiddicke aufgetragen über der Position in x-Richtung auf dem Chip<sup>15</sup>.

Abbildung 23: Gateoxidtiefe über der Position auf einem Chip

Da es sich bei den Prozessgradienten um stochastische Prozesse handelt, sind die resultierenden Kurven dem Schaltungs- bzw. Layout-Entwickler typischerweise unbekannt. Um dennoch schlechtes Matching zu vermeiden, kann auf bestimmte Techniken zurückgegriffen werden, welche die unbekannten Parameteränderungen ausgleichen. In Abbildung 24 ist das Matching zweier MOS-Transistoren bei örtlich variierender Oxiddicke dargestellt.

Die große Entfernung der Transistoren in Abbildung 24 (a) bewirkt besonders starke Unterschiede in der Oxiddicke und damit auch der elektrischen Parameter, daher ist das Matching der beiden Bauelemente unzureichend. Die Platzierung der Elemente in direkter örtlicher Nähe (b) verringert den Einfluss der örtlichen Prozessunterschiede und verbessert das Matching. Bauelemente, für die eine gute Übereinstimmung eine Rolle spielt, sollten folglich im Layout mit geringem räumlichen Abstand platziert werden.

<sup>&</sup>lt;sup>15</sup>Es könnte auch ein anderer Parameter betrachtet werden, z.B. der Flächenwiderstand von Polysilizium

Abbildung 24: Einfluss der Gateoxidtiefe auf unterschiedliche Transistoren

Neben der Platzierung in räumlicher Nähe gibt es weitere Möglichkeiten das Matching durch die Anordnung der Bauelemente zu beeinflussen. Eine davon ist das sogenannte Common-Centroid Layout, dessen Funktionsprizip in Abbildung 25 dargestellt ist.

Abbildung 25: Common-Centroid Layout bei Poly-Widerständen

Im dargestellten Graphen ist beispielhaft die Veränderung des Schichtwiderstands von Poly-Silizium über der Position auf dem Chip aufgetragen. Die im oberen Teil der Abbildung gezeigte Widerstandskonfiguration (a) führt zu einer Abweichung zwischen den Widerstandswerten von  $R_A$  und  $R_B$ , die aus der Variation des Schichtwiderstands resultiert. Dieser Unterschied im Widerstandswert kann durch die Anordnung in Abbildung 25 (b) verringert werden. Die Nutzung des gemeinsamen Mittelpunkts für beide Widerstände

bewirkt, dass sich die prozessbedingten Veränderungen im Schichtwiderstand in gleicher Weise sowohl auf Widerstand  $R_A$  als auch auf  $R_B$  auswirken. Die selbe Technik kann auch für MOS-Transistoren oder Kapazitäten verwendet werden.

## 3 Aufbau des TDC

In diesem Kapitel wird der Aufbau des TDC dargestellt. Auf einige der Komponenten wird dabei in größerem Umfang eingegangen als auf andere, da diese bereits in Vorarbeiten<sup>16</sup> entworfen und umfangreich beschrieben wurden. Zusätzlich wird der Regelkreis, in dem der TDC verwendet wird, in kurzer Form betrachtet. Dargestellt wird der Ausgangszustand der Schaltung zu Beginn dieser Arbeit. Die Optimierungen, die in der vorhergehenden Masterstudienarbeit<sup>17</sup> erarbeitet wurden, sind daher bereits umgesetzt und die Schaltung dementsprechend angepasst worden. Alle weiteren, im Rahmen dieser Arbeit vorgenommenen Änderungen, sind in Folgekapiteln beschrieben.

## 3.1 Gesamtaufbau des TDC

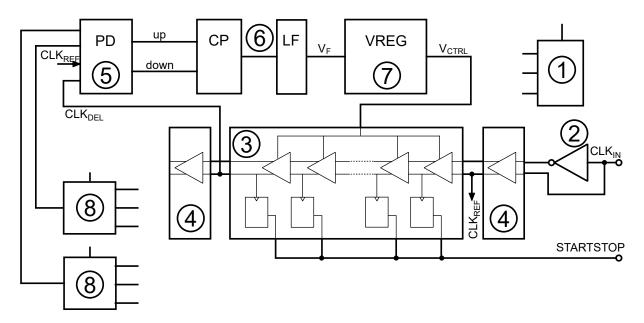

Abbildung 26: Blockdiagramm des Time-to-Digital Converters

Abbildung 26 zeigt eine vereinfachte Darstellung des TDC-Aufbaus. Im den folgenden Abschnitten werden die Komponenten des TDC im Detail betrachtet, um einen genauen Überblick über die Funktion der Gesamtschaltung zu schaffen.

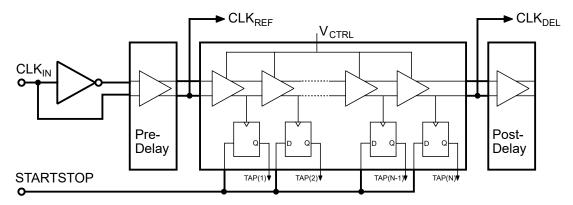

Bei dem vorhandenen TDC handelt es sich um einen Local-Passive-Interpolation TDC (LPI-TDC), der mithilfe eines DLL realisiert wurde. Zur Erzeugung des Bias-Stroms zur

<sup>&</sup>lt;sup>16</sup>[4], [5] <sup>17</sup>[1]

Arbeitspunkteinstellung des Spannungsreglers und der benötigten 3.3V Versorgungsspannung der digitalen und analogen Schaltungsteile des TDC steht eine Schaltung der Firma Elmos zur Verfügung (1).

Als Eingangstakt  $CLK_{IN}$  wird ein Taktsignal von 40MHz genutzt. Um bei den Schaltungssimulationen ein realitätsnahes Signal zu erzeugen und um ein invertiertes Eingangssignal für die differentielle Delay-Line zu erzeugen, wird das von einer idealen Spannungsquelle erzeugte Taktsignal zunächst durch eine Reihe von Invertern verzögert (2). Das Eingangssignal ist an die Delay-Line (3) angeschlossen, an deren Ende das verzögerte Taktsignal  $CLK_{DEL}$  austritt. Um am Anfang und Ende der Delay-Line eine gleichmäßige Last am Ein- und Ausgang der Delay-Elemente zu gewährleisten, sind einige Dummy-Delay-Elemente (4) platziert, die nicht zur Gesamtverzögerung der Delay-Line beitragen. Der für die Regelung relevante Referenztakt  $CLK_{REF}$  wird daher erst nach der Vorverzögerung durch die Dummy-Elemente abgegriffen.

Der Referenztakt und das verzögerte Taktsignal werden mithilfe eines Phasendetektors (5) auf ihre Phasenlage zueinander verglichen. Je nach vorauseilender Taktflanke wird vom Phasendetektor ein up oder down Signal generiert, das als Eingangssignal für die folgende Ladungspumpe mit Loop-Filter (6) dient. Die Ladungspumpe führt dem Loop-Filter abhängig vom Eingangssignal einen positiven oder negativen Strom zu, der die ausgehende Spannung  $V_F$  erhöht oder verringert.  $V_F$  dient als Eingangssignal für den Linearregler (7), der entsprechend seines Referenzsignals eine Kontrollspannung  $V_{CTRL}$  erzeugt, mit der die Delay-Line betrieben wird. Die Gesamtverzögerung der Delay-Line wird somit über die Spannung  $V_{CTRL}$  geregelt. Zusätzlich sind False- und Harmonic-Lock Detektoren (8) vorhanden, die ein fehlerhaftes Einschwingen des DLL verhindern sollen<sup>18</sup>.

Das zu messende Zeitintervall, in den bisherigen Betrachtungen begrenzt durch ein START und ein STOP Signal, wird als einzelnes STARTSTOP Signal in den TDC eingeführt. Daher ist eine externe Verknüpfung der beiden einzelnen Signale nötig, die in Abschnitt 4.3 betrachtet wird. Das STARTSTOP Signal wird mit den Dateneingängen der in der Delay-Line verwendeten Flipflops verbunden. Wird eine Messung durchgeführt, erzeugen die Flipflops einen Thermometer Code, der an den Datenausgängen TAP < 0 : N > abgegriffen werden kann.

<sup>&</sup>lt;sup>18</sup>Siehe Abschnitt 3.5

#### 3.2 Phasendetektor

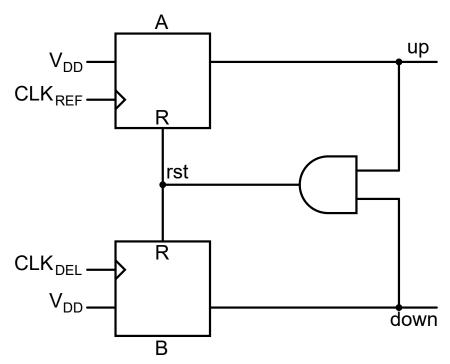

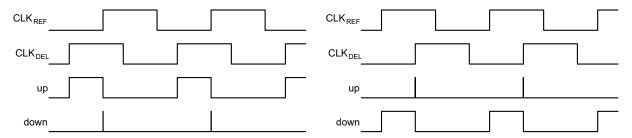

Der Phasendetektor gleicht den Eingangstakt mit dem durch die Delay-Line verzögerten Taktsignal ab und erzeugt entsprechend der Phasenlage der beiden Eingangssignale zwei Ausgangssignale. Realisiert werden kann ein Phasendetektor auf unterschiedliche Arten, zum einen durch ein XOR-Gate und zum anderen durch zwei D-Flipflops und einem AND-Gate<sup>19</sup>. Für die TDC-Schaltung wurde ein Phasendetektor mit D-Flipflops gewählt, welcher auch als Positive-Edge-Triggered (PET) Phasendetektor bezeichnet wird, da er auf die positive Flanke der Eingangssignale reagiert. Abbildung 27 zeigt die einfachste Ausführung dieses Phasendetektors, bestehend aus zwei Flipflops und einem AND-Gate.

Abbildung 27: Aufbau eines einfachen PET-Phasendetektors

Die Dateneingänge der Flipflops sind an die Versorgungsspannung des TDC angeschlossen. Im Falle eines voreilenden Referenztakts, wird bei steigender Flanke des  $CLK_{REF}$  Signals der Ausgang des Flipflop A und damit das Signal up auf HIGH geschaltet. Sobald im Flipflop B die steigende Flanke des nacheilenden Taktsignals  $CLK_{DEL}$  eingeht, wird auch down auf HIGH geschaltet und über das AND-Gate das Signal rst ausgelöst, das die Ausgänge der Flipflops zurücksetzt.

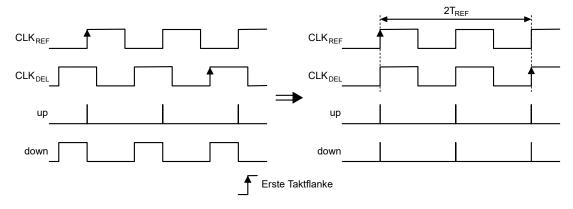

Eilt eines der beiden Taktsignale dem Anderen voraus, entsteht folglich ein up- oder downPuls, dessen Breite der Phasendifferenz der Taktsignale entspricht. Diese Pulse werden als

<sup>&</sup>lt;sup>19</sup>[6], S. 553ff

Eingangssignale für die nachfolgende Ladungspumpe genutzt. Ist kein Phasenunterschied vorhanden, verbleiben die Ausgänge des Phasendetektors auf LOW.

Abbildung 28: Signalverlauf des Phasendetektors bei unterschiedlichen Phasenverschiebungen

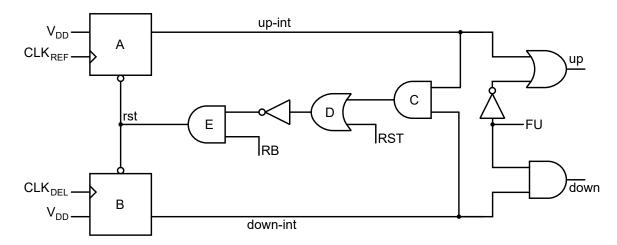

In der realen Anwendung wird der Phasendetektor um einige Komponenten erweitert, um ein externes Reset-Signal und die Ausgänge der Force-Up und False-Lock Schaltungen<sup>20</sup> zu integrieren. Abbildung 29 zeigt das Blockdiagramm des erweiterten Phasendetektors.

Abbildung 29: Aufbau des erweiterten Phasendetektors mit zusätzlichen Eingangssignalen

Über das OR-Gate D wird ein von der False-Lock Schaltung erzeugtes Reset-Signal RST in den Phasendetektor eingeführt. Sind also entweder die beiden up-int und down-int Signale, die durch das AND-Gate C verknüpft sind, oder der False-Lock Mechanismus aktiv, werden die Flipflops A und B zurückgesetzt. Da die Reset-Eingänge der Flipflops als "Active-Low"-Eingänge realisiert sind, ist eine Invertierung des Signals notwendig. Mithilfe des AND-Gates E wird ein weiteres Reset-Signal RB integriert, das zur externen Zurücksetzung des TDC genutzt werden kann. Das Force-Up Signal FU, das ebenfalls "Active-Low"ist, und bei Aktivierung einen konstanten up-Puls erzeugen soll, wird mithilfe eines AND- und eines OR-Gates mit den Ausgängen des Phasendetektors verknüpft.

$<sup>^{20}\</sup>mathrm{Siehe}$  Abschnitt 3.5

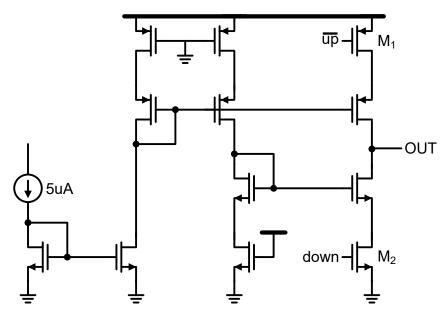

## 3.3 Charge Pump

Die Charge Pump hat die Aufgabe, entsprechend der beiden Ausgänge des Phasendetektors dem Loop-Filter einen Strom zuzuführen oder zu entziehen. Abbildung 30 zeigt den vereinfachten Aufbau der genutzten Charge-Pump.

Abbildung 30: Aufbau der Charge-Pump

Mithilfe eines Stromspiegels wird ein Strom von  $5\mu A$  auf die Eingangstransistoren  $M_1$  und  $M_2$  gespiegelt. Liegt ein down Signal an, wird Transistor  $M_2$  geschlossen und der eingestellte Strom fließt durch den Transistor. Da gleichzeitig zum down Signal kein up Signal anliegen kann, ist der Transistor  $M_1$  geöffnet und lässt daher keinen Stromfluss zu. Der Strom wird daher dem nachgeschalteten Loop-Filter entzogen, der aus einer einzelnen Kapazität aufgebaut ist. Liegt ein up Signal an, ist Transistor  $M_1$  geschlossen und der eingestellte Strom wird dem Loop-Filter zugeführt, da Transistor  $M_2$  in diesem Fall keinen Stromfluss zulässt.

Der detaillierte Entwurf und Test verschiedener Charge Pumps für die vorhandene TDC-Anwendung wurde bereits in Vorarbeiten durchgeführt<sup>21</sup> und wird daher im Rahmen dieser Arbeit nicht genauer betrachtet.

<sup>&</sup>lt;sup>21</sup>[5], S. 48ff

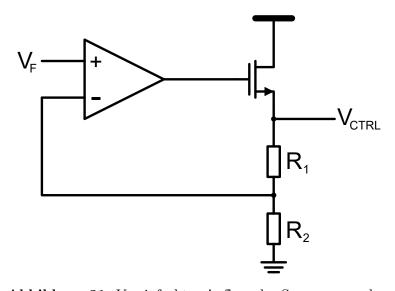

## 3.4 Spannungsregler

Der Linear-Spannungsregler wird genutzt, um die Ausgangsspannung des Loop-Filters  $V_{REF}$  von der Last der Delay-Line zu entkoppeln. Für die Spannungsversorgung der Delay-Line, die aus zahlreichen Elementen besteht, wird eine stabile Spannung benötigt, die bei der vorhandenen Last nicht von der Ladungspumpe mit Loop-Filter bereitgestellt werden kann.

Abbildung 31: Vereinfachter Aufbau des Spannungsreglers

Abbildung 31 zeigt den vereinfachten Aufbau des Spannungsreglers. Als Eingang wird ein differenzieller Verstärker genutzt der die eingehende Filterspannung mit dem Wert der über das negative Feedback zurückgeführten Ausgangsspannung vergleicht. Über ein Pass-Device, in dieser Anwendung ein als Source-Folger konfigurierter NMOS-Transistor, wird die Ausgangsspannung  $V_{CTRL}$  reguliert. Die Dimensionierung der Feedback-Widerstände  $R_1$  und  $R_2$  bestimmt den Anteil der Ausgangsspannung, der an die differenzielle Eingangsstufe zurückgeführt wird. Für die Ausgangsspannung gilt:

$$V_{CTRL} = V_F \cdot \left(1 + \frac{R_1}{R_2}\right) \tag{21}$$

In der vorhandenen Schaltung wurde für die Widerstände ein Verhältnis von  $\frac{R_1}{R_2} = \frac{1}{3}$  gewählt. Die Filterspannung  $V_F$  wird folglich mit einem Faktor von  $\frac{4}{3}$  multipliziert. Da für die vorhandene Anwendung ein Standard-Regler aus der Design-Bibliothek der Firma Elmos genutzt wurde und im Rahmen dieser Arbeit keine Veränderungen am Spannungsregler vorgenommen wurden, wird an dieser Stelle nicht detailliert auf den Aufbau auf

Transistorebene eingegangen.

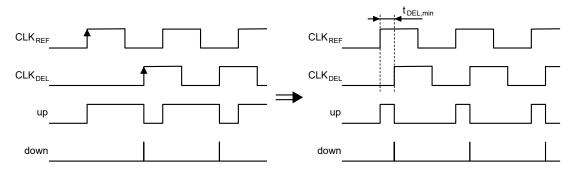

#### 3.5 False- und Harmonic-Lock

Der Vergleich des eingehenden Taktsignals mit dem durch die Delay-Line verzögerten Taktsignal am eingesetzten Phasendetektor führt unter bestimmten Ausgangssbedingungen zu einem ungewünschten Verhalten der Delay Locked Loop. Ist beispielsweise die Verzögerung der Delay-Line zu Beginn des Betriebs der DLL geringer als die Dauer einer Taktperiode des Referenztakts, erzeugt der Phasendetektor, wie in Abbildung 32 dargestellt, lange *up*-Pulse mit dem Ziel die Phasenverschiebung der beiden Eingangssignale auf Null zu regeln. Da dies nicht möglich ist, wird sich die DLL auf die Minimalverzögerung der Delay-Line einschwingen. Dieses Fehlverhalten bezeichnet man als False-Lock.

Abbildung 32: Einschwingen auf minimales Delay bei einem False-Lock

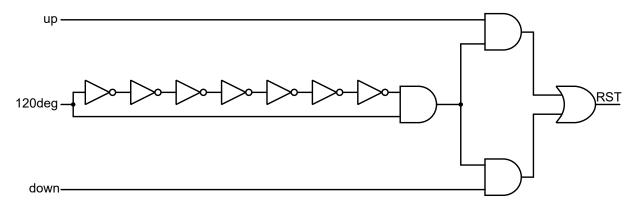

Um zu vermeiden, dass ein solcher False-Lock ensteht, wird ein zusätzlicher Schaltungsteil eingeführt, der die Länge von up- und down-Pulsen auf ein Maximum begrenzt. Abbildung 33 zeigt die schematische Darstellung des verwendeten False-Lock Detektors.

**Abbildung 33:** False-Lock Detektor

Das Signal 120deq wird dem False-Lock Detektor aus der Delay-Line zugeführt, und ent-

spricht dem Eingangstakt nachdem dieser ein Drittel der Delay-Line durchlaufen hat. Durch eine Inversion, eine Verzögerung, welche durch eine Kette aus sechs Invertern realisiert wird, und Verknüpfung mit einem AND-Gatter entsteht bei jedem Durchlauf des Taktsignals ein kurzer Puls hinter dem AND-Gatter dessen Breite der Verzögerungsdauer  $t_{delay}$  entspricht. Ist zur gleichen Zeit entweder das up- oder down-Signal aktiv, wird durch den Force-Up Detektor ein kurzer Reset-Puls erzeugt, der den Phasendetektor zurücksetzt. In der in Abbildung 32 dargestellten Situation wird nach der Zurücksetzung des Phasendetektors durch die folgende steigende Taktflanke des verzögerten Taktes  $CLK_{DEL}$  ein down-Puls ausgelöst und die Verzögerung der Delay-Line entsprechend erhöht, bis die DLL auf eine Taktperiode eingeschwungen ist.

Ein weiteres Problem tritt auf, wenn die Verzögerung der Delay-Line während des Betriebs das 1,5-fache der Referenzperiodendauer überschreitet. In diesem Fall wird durch den Phasendetektor fälschlicherweise ein down-Signal ausgelöst und die Delay-Line wird auf eine Verzögerung geregelt, die dem Vielfachen einer Periodendauer entspricht. Dieser Zustand wird als Harmonic-Lock bezeichnet.

Abbildung 34: Signalverlauf bei einem Harmonic-Lock

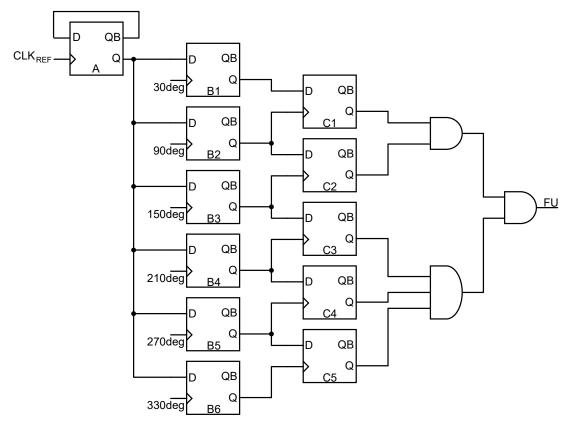

Um das Einschwingen auf das Vielfache einer Taktperiode zu verhindern, wird eine weitere Schaltung benötigt, die im Falle einer zu großen Verzögerung ein up-Signal des Phasendetektors erzwingt.

Der Aufbau des Harmonic-Lock Detektors ist in Abbildung 35 dargestellt. Über das D-Flipflop A wird der Referenztakt von 40 MHz auf 20 MHz halbiert. Dieser halbierte Takt dient als Dateneingang der folgenden Flipflops. An den Takteingängen der Flipflops B1-B6 werden in gleichmäßigen Abständen verzögerte Signale aus der Delay-Line angeschlossen. Dies hat zur Folge, dass die folgenden Flipflops (C1-C5) nur auf den logischen High-Zustand umschalten, wenn alle eingehenden Signale aus der Delay-Line innerhalb einer Taktperiode des Referenztakts auftreten. Ist die zeitliche Verzögerung der Delay-Line zu

Abbildung 35: Aufbau des Harmonic-Lock Detektors

groß, d.h. geht eines der eingehenden Taktsignale zu spät ein, wird das Force-Up Signal FU durch die AND Verknüpfung der Flipflops auf LOW geschaltet. Das Signal FU, das als "Active-Low"-Signal implementiert ist, erzwingt ein up Signal im Phasendetektor und verkürzt folglich die Verzögerungszeit der Delay-Line, bis alle Eingänge des Harmonic-Lock Detektors innerhalb einer Taktperiode auftreten.

## 3.6 Delay-Line

Die Delay-Line des TDC hat die Aufgabe, das eingehende Taktsignal um genau eine Taktperiode zu verzögern. Um dies bei verschiedenen Temperaturen und über unterschiedliche Prozesscorner zu erreichen, muss die Verzögerung steuerbar sein. Für die Änderung der zeitlichen Verzögerung der einzelnen Verzögerungselemente stehen unterschiedliche Ansätze zur Verfügung, die im Detail in Vorarbeiten untersucht wurden<sup>22</sup>.

In der vorhandenen Schaltung werden spannungsgesteuerte differenzielle Inverter als Ver-

$<sup>\</sup>frac{1}{22}[4]$

zögerungselemente genutzt. Um die Verzögerungszeit der Elemente zu verändern, wird die Versorgungsspannung der Inverter angepasst bis die Verzögerung der Delay-Line einer Taktperiode des Referenztakts entspricht. In der vorhergehenden Masterstudienarbeit wurde die Delay-Line von einer Länge von 144 Elementen auf 180 Elemente erweitert. Da während der Betrachtung der Homogenität der Verzögerungszeiten festgestellt wurde, dass es in den ersten und letzten Elementen der Delay-Line starke Variationen zwischen den Verzögerungzeiten gibt, werden weitere Elemente am Anfang und am Ende der Delay-Line platziert, die allerdings nicht zur Gesamtverzögerung beitragen.

Abbildung 36: Schematische Darstellung der spannungsgesteuerten Delay-Line

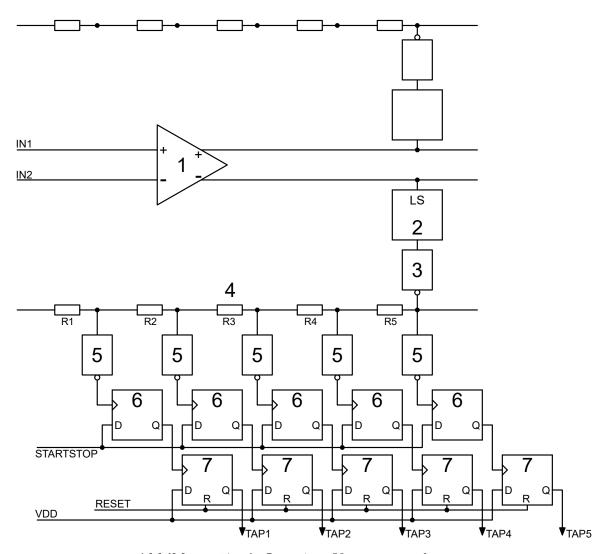

#### Aufbau der Verzögerungselemente

Die einzelnen Verzögerungselemente der Delay-Line bestehen neben dem differenziellen Inverter aus einer Reihe von Bauelementen. Abbildung 37 zeigt den Aufbau eines Verzögerungselements.

Da die Kontrollspannung  $V_{CTRL}$  direkt als Versorgungsspannung der Inverterkette genutzt wird, sind auch die Ausgangsspannungen der Inverter (1) auf den Wert der Kontrollspannung begrenzt. Um die Ausgangswerte für die weitere Nutzung wieder auf einen Signalpegel von 3.3V anzuheben, werden an den Ausgängen der Inverter Level-Shifter (2) verwendet. Eine ausreichend starke Bufferstufe (3) aus in Reihe geschalteten, stufenweise größer dimensionierten Invertern wird benötigt, um die Interpolationswiderstände (4) und die damit verbundenen Ausgangs-Bufferstufen (5) zu treiben. Die Interpolationswiderstände ermöglichen die Verbesserung der Auflösung, wie in Abschnitt 2.3 beschrieben.

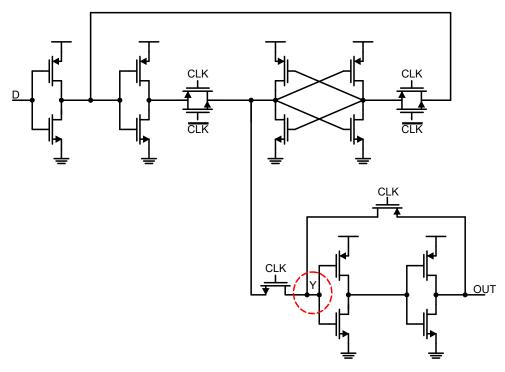

Jeder Ausgang eines Interpolationswiderstandes ist nach Durchlaufen der zusätzlichen Bufferstufe mit dem Takteingang eines D-Flipflops (6) verbunden. Liegt am Dateneingang der Flipflops das STARTSTOP Signal an, wird bei Durchlaufen des Taktsignals

Abbildung 37: Aufbau eines Verzögerungselements